# International Rectifier

- Application Specific MOSFETs

- Ideal for CPU Core DC-DC Converters

- Low Conduction Losses

- Low Switching Losses

- Low Profile (<0.7 mm)

- Dual Sided Cooling Compatible

- Compatible with existing Surface Mount Techniques

IRF6604

HEXFET® Power MOSFET

| V <sub>DSS</sub> | R <sub>DS(on)</sub> max          | Qg   |

|------------------|----------------------------------|------|

| 30V              | 11.5m $\Omega$ @ $V_{GS} = 7.0V$ | 17nC |

|                  | $13m\Omega@V_{GS} = 4.5V$        |      |

Applicable DirectFET Outline and Substrate Outline (see p.9,10 for details)

| I | SQ | SX | ST | MQ | MX | MT |  |  |

|---|----|----|----|----|----|----|--|--|

### **Description**

The IRF6604 combines the latest HEXFET® Power MOSFET Silicon technology with the advanced DirectFET™ packaging to achieve the lowest on-state resistance charge product in a package that has the footprint of an SO-8 and only 0.7 mm profile. The DirectFET package is compatible with existing layout geometries used in power applications, PCB assembly equipment and vapor phase, infra-red or convection soldering techniques, when application note AN-1035 is followed regarding the manufacturing methods and process. The DirectFET package allows dual sided cooling to maximize thermal transfer in power systems, IMPROVING previous best thermal resistance by 80%.

The IRF6604 balances both low resistance and low charge along with ultra low package inductance to reduce both conduction and switching losses. The reduced total losses make this product ideal for high efficiency DC-DC converters that power the latest generation of processors operating at higher frequencies. The IRF6604 has been optimized for parameters that are critical in synchronous buck converters including Rds(on) and gate charge to minimize losses in the control FET socket.

**Absolute Maximum Ratings**

|                                        | Parameter                                        | Max.         | Units |

|----------------------------------------|--------------------------------------------------|--------------|-------|

| V <sub>DS</sub>                        | Drain-to-Source Voltage                          | 30           | V     |

| $V_{GS}$                               | Gate-to-Source Voltage                           | ±12          |       |

| I <sub>D</sub> @ T <sub>C</sub> = 25°C | Continuous Drain Current, V <sub>GS</sub> @ 7.0V | 49           |       |

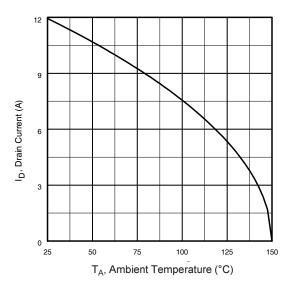

| I <sub>D</sub> @ T <sub>A</sub> = 25°C | Continuous Drain Current, V <sub>GS</sub> @ 7.0V | 12           | Α     |

| I <sub>D</sub> @ T <sub>A</sub> = 70°C | Continuous Drain Current, V <sub>GS</sub> @ 7.0V | 9.2          |       |

| I <sub>DM</sub>                        | Pulsed Drain Current ①                           | 92           |       |

| P <sub>D</sub> @T <sub>A</sub> = 25°C  | Power Dissipation ©                              | 2.3          |       |

| P <sub>D</sub> @T <sub>A</sub> = 70°C  | Power Dissipation ©                              | 1.5          | W     |

| P <sub>D</sub> @T <sub>C</sub> = 25°C  | Power Dissipation                                | 42           |       |

|                                        | Linear Derating Factor                           | 0.018        | W/°C  |

| T <sub>J</sub>                         | Operating Junction and                           | -40 to + 150 | °C    |

| T <sub>STG</sub>                       | Storage Temperature Range                        |              |       |

**Thermal Resistance**

|                           | Parameter                     | Тур. | Max. | Units |

|---------------------------|-------------------------------|------|------|-------|

| $R_{\theta JA}$           | Junction-to-Ambient ④®        |      | 55   |       |

| $R_{\theta JA}$           | Junction-to-Ambient \$\sime\$ | 12.5 |      |       |

| $R_{\theta JA}$           | Junction-to-Ambient ©®        | 20   |      | °C/W  |

| $R_{\theta JC}$           | Junction-to-Case ⑦®           |      | 3.0  |       |

| $R_{\theta J\text{-PCB}}$ | Junction-to-PCB Mounted       | 1.0  |      |       |

Notes ① through ® are on page 11 www.irf.com

### Static @ T<sub>J</sub> = 25°C (unless otherwise specified)

|                                                                    | Parameter                            | Min. | Тур. | Max. | Units | Conditions                                        |

|--------------------------------------------------------------------|--------------------------------------|------|------|------|-------|---------------------------------------------------|

| BV <sub>DSS</sub>                                                  | Drain-to-Source Breakdown Voltage    | 30   |      |      | V     | $V_{GS} = 0V, I_{D} = 250\mu A$                   |

| $\Delta \mathrm{BV}_{\mathrm{DSS}}/\Delta \mathrm{T}_{\mathrm{J}}$ | Breakdown Voltage Temp. Coefficient  | _    | 27   |      | mV/°C | Reference to 25°C, I <sub>D</sub> = 1mA           |

| R <sub>DS(on)</sub>                                                | Static Drain-to-Source On-Resistance | _    | 9.0  | 11.5 | mΩ    | $V_{GS} = 7.0V, I_D = 12A$ ③                      |

|                                                                    |                                      |      | 10   | 13   | 1     | $V_{GS} = 4.5V, I_D = 9.6A$ ③                     |

| $V_{GS(th)}$                                                       | Gate Threshold Voltage               | 1.3  |      | 2.1  | V     | $V_{DS} = V_{GS}, I_{D} = 250\mu A$               |

| $\Delta V_{GS(th)}/\Delta T_J$                                     | Gate Threshold Voltage Coefficient   | _    | -4.5 | _    | mV/°C |                                                   |

| I <sub>DSS</sub>                                                   | Drain-to-Source Leakage Current      |      |      | 30   | μΑ    | $V_{DS} = 24V, V_{GS} = 0V$                       |

|                                                                    |                                      |      |      | 50   | μΑ    | $V_{DS} = 30V, V_{GS} = 0V$                       |

|                                                                    |                                      | _    |      | 100  | 1     | $V_{DS} = 24V, V_{GS} = 0V, T_{J} = 125^{\circ}C$ |

| I <sub>GSS</sub>                                                   | Gate-to-Source Forward Leakage       |      |      | 100  | nA    | V <sub>GS</sub> = 12V                             |

|                                                                    | Gate-to-Source Reverse Leakage       |      |      | -100 | 1     | V <sub>GS</sub> = -12V                            |

| gfs                                                                | Forward Transconductance             | 38   |      | _    | S     | $V_{DS} = 15V, I_{D} = 9.6A$                      |

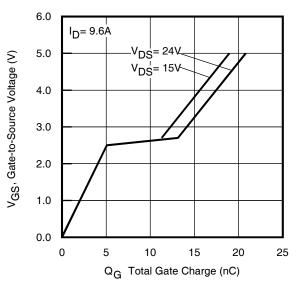

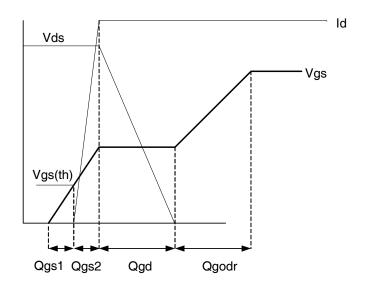

| $Q_g$                                                              | Total Gate Charge                    |      | 17   | 26   |       |                                                   |

| $Q_{gs1}$                                                          | Pre-Vth Gate-to-Source Charge        | _    | 4.1  |      | 1     | $V_{DS} = 15V$                                    |

| $Q_{gs2}$                                                          | Post-Vth Gate-to-Source Charge       |      | 1.0  |      | nC    | $V_{GS} = 4.5V$                                   |

| $Q_gd$                                                             | Gate-to-Drain Charge                 | _    | 6.3  |      | 1     | $I_{D} = 9.6A$                                    |

| $Q_{godr}$                                                         | Gate Charge Overdrive                |      | 5.6  |      |       | See Fig. 16                                       |

| $Q_{sw}$                                                           | Switch Charge $(Q_{gs2} + Q_{gd})$   |      | 7.3  |      | 1     |                                                   |

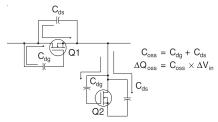

| Q <sub>oss</sub>                                                   | Output Charge                        |      | 9.5  |      | nC    | $V_{DS} = 16V, V_{GS} = 0V$                       |

| $R_G$                                                              | Gate Resistance                      |      | 1.1  | 2.0  | Ω     |                                                   |

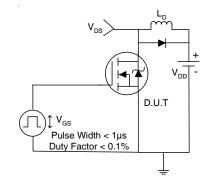

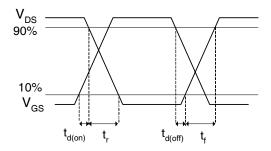

| t <sub>d(on)</sub>                                                 | Turn-On Delay Time                   |      | 11   |      |       | $V_{DD} = 15V, V_{GS} = 4.5V$ 3                   |

| t <sub>r</sub>                                                     | Rise Time                            |      | 4.3  |      | 1     | $I_{D} = 9.6A$                                    |

| t <sub>d(off)</sub>                                                | Turn-Off Delay Time                  |      | 18   |      | ns    | Clamped Inductive Load                            |

| t <sub>f</sub>                                                     | Fall Time                            |      | 25   |      | 1     |                                                   |

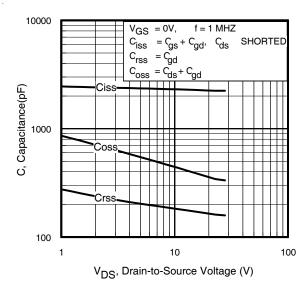

| C <sub>iss</sub>                                                   | Input Capacitance                    |      | 2270 |      |       | $V_{GS} = 0V$                                     |

| C <sub>oss</sub>                                                   | Output Capacitance                   |      | 420  |      | pF    | $V_{DS} = 15V$                                    |

| $C_{rss}$                                                          | Reverse Transfer Capacitance         |      | 190  |      | 1     | f = 1.0MHz                                        |

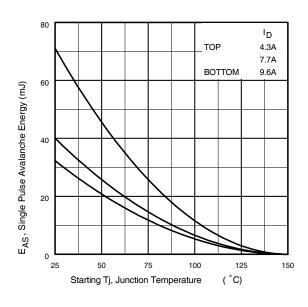

### **Avalanche Characteristics**

|                 | Parameter                      | Тур. | Max. | Units |

|-----------------|--------------------------------|------|------|-------|

| E <sub>AS</sub> | Single Pulse Avalanche Energy® |      | 32   | mJ    |

| I <sub>AR</sub> | Avalanche Current ①            |      | 9.6  | Α     |

| E <sub>AR</sub> | Repetitive Avalanche Energy ①  |      | 0.23 | mJ    |

### **Diode Characteristics**

|                 | Parameter                 | Parameter Min. Typ. N |      | Max. | Units | Conditions                                     |  |

|-----------------|---------------------------|-----------------------|------|------|-------|------------------------------------------------|--|

| I <sub>S</sub>  | Continuous Source Current |                       |      | 42   |       | MOSFET symbol                                  |  |

|                 | (Body Diode)              |                       |      |      | Α     | showing the                                    |  |

| I <sub>SM</sub> | Pulsed Source Current     |                       |      | 92   |       | integral reverse                               |  |

|                 | (Body Diode) ①            |                       |      |      |       | p-n junction diode.                            |  |

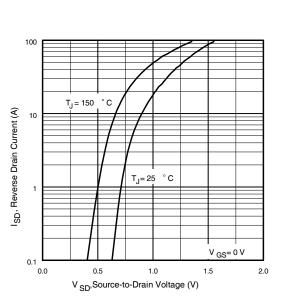

| $V_{SD}$        | Diode Forward Voltage     |                       | 0.94 | 1.2  | V     | $T_J = 25^{\circ}C, I_S = 9.6A, V_{GS} = 0V$ ③ |  |

| t <sub>rr</sub> | Reverse Recovery Time     |                       | 31   | 47   | ns    | $T_J = 25^{\circ}C, I_F = 9.6A$                |  |

| $Q_{rr}$        | Reverse Recovery Charge   |                       | 26   | 39   | nC    | di/dt = 100A/μs ③                              |  |

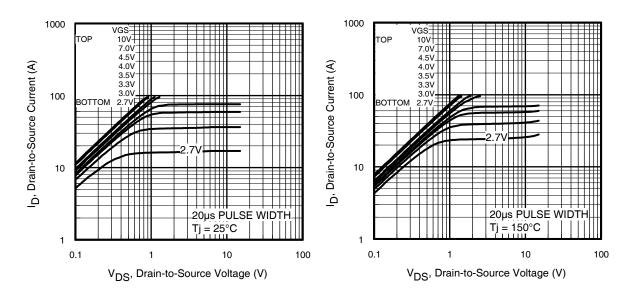

Fig 1. Typical Output Characteristics

Fig 2. Typical Output Characteristics

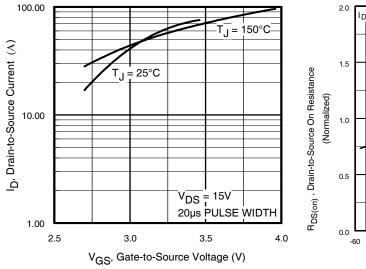

Fig 3. Typical Transfer Characteristics

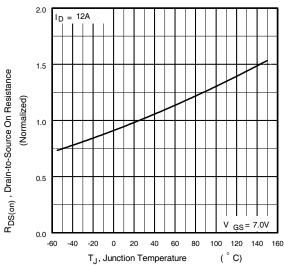

**Fig 4.** Normalized On-Resistance Vs. Temperature

**Fig 5.** Typical Capacitance Vs. Drain-to-Source Voltage

**Fig 7.** Typical Source-Drain Diode Forward Voltage

**Fig 6.** Typical Gate Charge Vs. Gate-to-Source Voltage

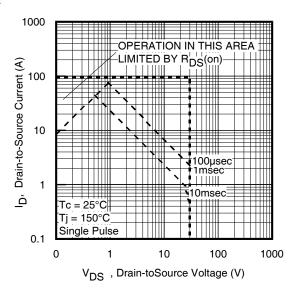

Fig 8. Maximum Safe Operating Area

2.0 1.8 VGS(th) Gate threshold Voltage (V) 1.6 1.4  $I_D = 250\mu A$ 1.2 1.0 0.8 0.6 0.4 0.2 0.0 -75 -50 25 50 75 100 125 150  $T_J$  , Temperature (  $^{\circ}C$  )

**Fig 9.** Maximum Drain Current Vs. Ambient Temperature

Fig 10. Threshold Voltage Vs. Temperature

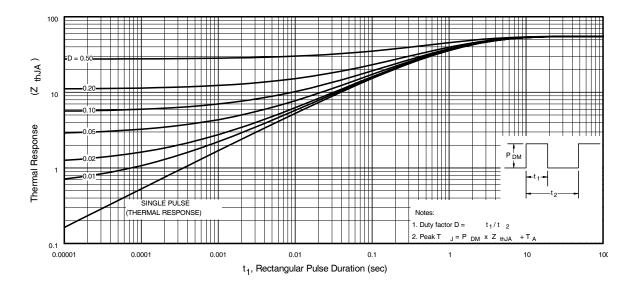

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Ambient

IRF6604 International Rectifier

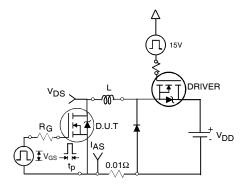

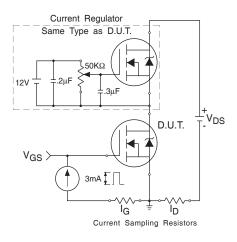

Fig 12a. Unclamped Inductive Test Circuit

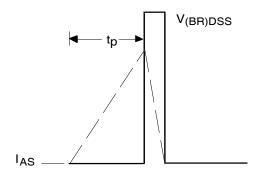

Fig 12b. Unclamped Inductive Waveforms

Fig 13. Gate Charge Test Circuit

**Fig 12c.** Maximum Avalanche Energy Vs. Drain Current

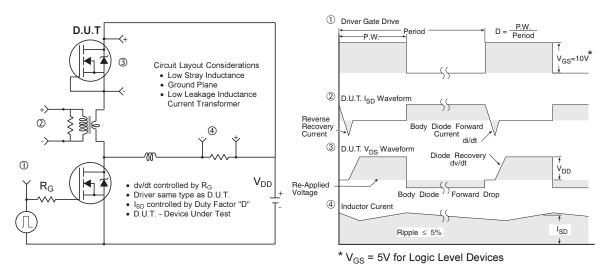

Fig 14a. Switching Time Test Circuit

**Fig 14b.** Switching Time Waveforms www.irf.com

Fig 15. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET® Power MOSFETs

Fig 16. Gate Charge Waveform

### Power MOSFET Selection for Non-Isolated DC/DC Converters

#### **Control FET**

Special attention has been given to the power losses in the switching elements of the circuit - Q1 and Q2. Power losses in the high side switch Q1, also called the Control FET, are impacted by the  $R_{\rm ds(on)}$  of the MOSFET, but these conduction losses are only about one half of the total losses.

Power losses in the control switch Q1 are given by;

$$P_{loss} = P_{conduction} + P_{switching} + P_{drive} + P_{output}$$

This can be expanded and approximated by;

$$\begin{split} P_{loss} &= \left(I_{rms}^{2} \times R_{ds(on)}\right) \\ &+ \left(I \times \frac{Q_{gd}}{i_{g}} \times V_{in} \times f\right) + \left(I \times \frac{Q_{gs2}}{i_{g}} \times V_{in} \times f\right) \\ &+ \left(Q_{g} \times V_{g} \times f\right) \\ &+ \left(\frac{Q_{oss}}{2} \times V_{in} \times f\right) \end{split}$$

This simplified loss equation includes the terms  ${\rm Q_{gs2}}$  and  ${\rm Q_{oss}}$  which are new to Power MOSFET data sheets.

$Q_{gs2}$  is a sub element of traditional gate-source charge that is included in all MOSFET data sheets. The importance of splitting this gate-source charge into two sub elements,  $Q_{gs1}$  and  $Q_{gs2}$ , can be seen from Fig 16.

$Q_{gs2}$  indicates the charge that must be supplied by the gate driver between the time that the threshold voltage has been reached and the time the drain current rises to  $I_{dmax}$  at which time the drain voltage begins to change. Minimizing  $Q_{gs2}$  is a critical factor in reducing switching losses in Q1.

$\rm Q_{\rm oss}$  is the charge that must be supplied to the output capacitance of the MOSFET during every switching cycle. Figure A shows how  $\rm Q_{\rm oss}$  is formed by the parallel combination of the voltage dependant (nonlinear) capacitance's  $\rm C_{\rm ds}$  and  $\rm C_{\rm dg}$  when multiplied by the power supply input buss voltage.

#### Synchronous FET

The power loss equation for Q2 is approximated by:

$$\begin{split} P_{loss} &= P_{conduction} + P_{drive} + P_{output}^* \\ P_{loss} &= \left(I_{rms}^2 \times R_{ds(on)}\right) \\ &+ \left(Q_g \times V_g \times f\right) \\ &+ \left(\frac{Q_{oss}}{2} \times V_{in} \times f\right) + \left(Q_{rr} \times V_{in} \times f\right) \end{split}$$

\*dissipated primarily in Q1.

For the synchronous MOSFET Q2,  $R_{\rm ds(on)}$  is an important characteristic; however, once again the importance of gate charge must not be overlooked since it impacts three critical areas. Under light load the MOSFET must still be turned on and off by the control IC so the gate drive losses become much more significant. Secondly, the output charge  $Q_{\rm oss}$  and reverse recovery charge  $Q_{\rm rr}$  both generate losses that are transfered to Q1 and increase the dissipation in that device. Thirdly, gate charge will impact the MOSFETs' susceptibility to Cdv/dt turn on.

The drain of Q2 is connected to the switching node of the converter and therefore sees transitions between ground and  $V_{\rm in}.$  As Q1 turns on and off there is a rate of change of drain voltage dV/dt which is capacitively coupled to the gate of Q2 and can induce a voltage spike on the gate that is sufficient to turn the MOSFET on, resulting in shoot-through current . The ratio of  $Q_{\rm gd}/Q_{\rm gs1}$  must be minimized to reduce the potential for Cdv/dt turn on.

Figure A: Qoss Characteristic

IRF6604

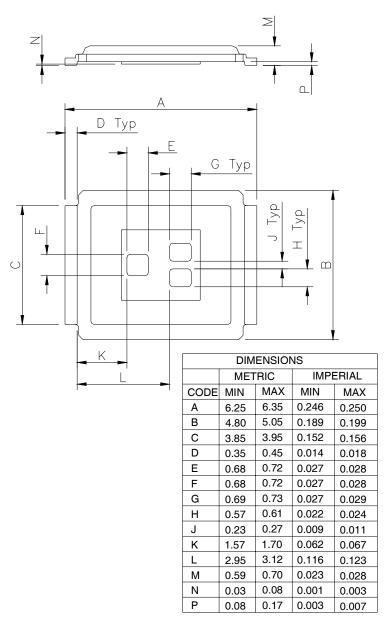

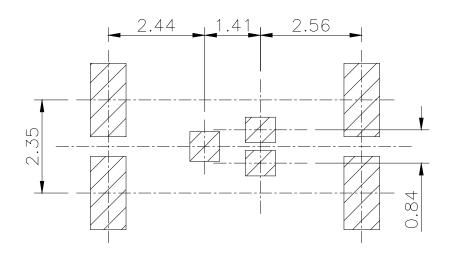

# DirectFET™ Outline Dimension, MQ Outline (Medium Size Can, Q-Designation).

Please see DirectFET application note AN-1035 for all details regarding the assembly of DirectFET. This includes all recommendations for stencil and substrate designs.

## IRF6604

International IOR Rectifier

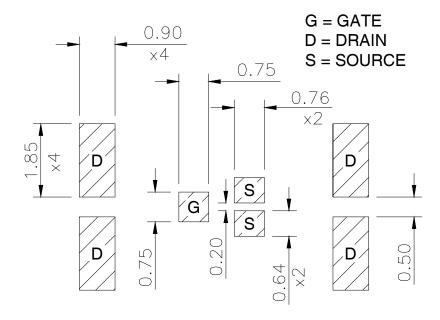

# DirectFET™ Substrate and PCB Layout, MQ Outline (MediumSize Can, Q-Designation).

Please see DirectFET application note AN-1035 for all details regarding the assembly of DirectFET. This includes all recommendations for stencil and substrate designs.

International **IOR** Rectifier

IRF6604

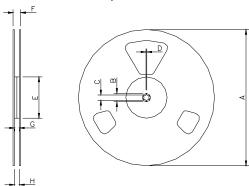

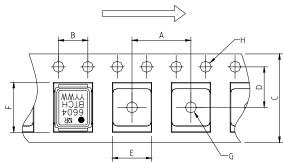

# DirectFET™ Tape & Reel Dimension (Showing component orientation).

NOTE: Controlling dimensions in mm Std reel quantity is 4800 parts. (ordered as IRF6604). For 1000 parts on 7" reel, order IRF6604TR1

|      | REEL DIMENSIONS |        |                       |       |        |       |       |       |  |  |  |

|------|-----------------|--------|-----------------------|-------|--------|-------|-------|-------|--|--|--|

| S    | TANDARI         | OPTION | TR1 OPTION (QTY 1000) |       |        |       |       |       |  |  |  |

|      | ME              | TRIC   | IMP                   | ERIAL | ME     | TRIC  | IMP   | ERIAL |  |  |  |

| CODE | MIN             | MAX    | MIN                   | MAX   | MIN    | MAX   | MIN   | MAX   |  |  |  |

| Α    | 330.0           | N.C    | 12.992                | N.C   | 177.77 | N.C   | 6.9   | N.C   |  |  |  |

| В    | 20.2            | N.C    | 0.795                 | N.C   | 19.06  | N.C   | 0.75  | N.C   |  |  |  |

| С    | 12.8            | 13.2   | 0.504                 | 0.520 | 13.5   | 12.8  | 0.53  | 0.50  |  |  |  |

| D    | 1.5             | N.C    | 0.059                 | N.C   | 1.5    | N.C   | 0.059 | N.C   |  |  |  |

| E    | 100.0           | N.C    | 3.937                 | N.C   | 58.72  | N.C   | 2.31  | N.C   |  |  |  |

| F    | N.C             | 18.4   | N.C                   | 0.724 | N.C    | 13.50 | N.C   | 0.53  |  |  |  |

| G    | 12.4            | 14.4   | 0.488                 | 0.567 | 11.9   | 12.01 | 0.47  | N.C   |  |  |  |

| Н    | 11.9            | 15.4   | 0.469                 | 0.606 | 11.9   | 12.01 | 0.47  | N.C   |  |  |  |

### LOADED TAPE FEED DIRECTION

| DIMENSIONS |       |       |          |       |  |  |  |  |

|------------|-------|-------|----------|-------|--|--|--|--|

|            | ME    | TRIC  | IMPERIAL |       |  |  |  |  |

| CODE       | MIN   | MAX   | MIN      | MAX   |  |  |  |  |

| Α          | 7.90  | 8.10  | 0.311    | 0.319 |  |  |  |  |

| В          | 3.90  | 4.10  | 0.154    | 0.161 |  |  |  |  |

| С          | 11.90 | 12.30 | 0.469    | 0.484 |  |  |  |  |

| D          | 5.45  | 5.55  | 0.215    | 0.219 |  |  |  |  |

| E          | 5.10  | 5.30  | 0.201    | 0.209 |  |  |  |  |

| F          | 6.50  | 6.70  | 0.256    | 0.264 |  |  |  |  |

| G          | 1.50  | N.C   | 0.059    | N.C   |  |  |  |  |

| Н          | 1.50  | 1.60  | 0.059    | 0.063 |  |  |  |  |

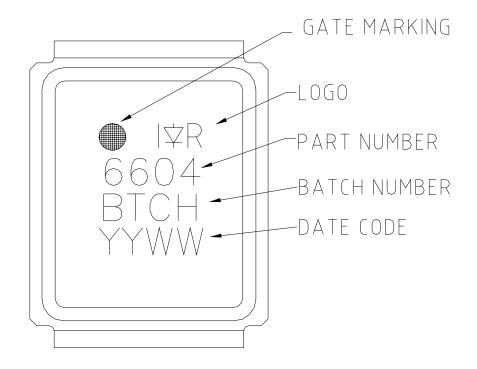

### DirectFET™ Part Marking

#### Notes:

- ① Repetitive rating; pulse width limited by max. junction temperature.

- ② Starting  $T_J = 25$ °C, L = 0.70mH  $R_G = 25\Omega$ ,  $I_{AS} = 9.6$ A.

- 3 Pulse width  $\leq 400\mu s$ ; duty cycle  $\leq 2\%$ .

- ④ Surface mounted on 1 in. square Cu board.

- ⑤ Used double sided cooling, mounting pad.

- ⑥ Mounted on minimum footprint full size board with metalized back and with small clip heatsink.

- T<sub>C</sub> measured with thermal couple mounted to top (Drain) of part.

- $\ensuremath{\$}\ \ensuremath{\mathsf{R}}_{\theta}$  is measured at  $T_J$  of approximately 90°C.

Data and specifications subject to change without notice.

This product has been designed and qualified for the Consumer market.

Qualification Standards can be found on IR's Web site.

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information, 11/05

Note: For the most current drawings please refer to the IR website at: <a href="http://www.irf.com/package/">http://www.irf.com/package/</a>