## JFET - VHF/UHF Amplifier Transistor

#### **N-Channel**

#### MMBFJ309LT1 MMBFJ310LT1

#### **MAXIMUM RATINGS**

| Rating               | Symbol          | Value | Unit |

|----------------------|-----------------|-------|------|

| Drain-Source Voltage | V <sub>DS</sub> | 25    | Vdc  |

| Gate-Source Voltage  | V <sub>GS</sub> | 25    | Vdc  |

| Gate Current         | IG              | 10    | mAdc |

## 2

CASE 318-08, STYLE 10 SOT-23 (TO-236AB)

# 3 GATE 1 DRAIN

#### THERMAL CHARACTERISTICS

| Characteristic                                                           | Symbol               | Max         | Unit  |

|--------------------------------------------------------------------------|----------------------|-------------|-------|

| Total Device Dissipation FR–5 Board <sup>(1)</sup> T <sub>A</sub> = 25°C | PD                   | 225         | mW    |

| Derate above 25°C                                                        |                      | 1.8         | mW/°C |

| Thermal Resistance, Junction to Ambient                                  | $R_{\theta JA}$      | 556         | °C/W  |

| Junction and Storage Temperature                                         | TJ, T <sub>stg</sub> | -55 to +150 | °C    |

#### **DEVICE MARKING**

MMBFJ309LT1 = 6U; MMBFJ310LT1 = 6T

#### **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                          |                      | Symbol             | Min          | Тур    | Max          | Unit         |

|---------------------------------------------------------------------------------------------------------|----------------------|--------------------|--------------|--------|--------------|--------------|

| OFF CHARACTERISTICS                                                                                     |                      |                    |              |        |              |              |

| Gate–Source Breakdown Voltage ( $I_G = -1.0 \mu Adc$ , $V_{DS} =$                                       | 0)                   | V(BR)GSS           | -25          | -      | -            | Vdc          |

| Gate Reverse Current (V <sub>GS</sub> = -15 Vdc)<br>(V <sub>GS</sub> = -15 Vdc, T <sub>A</sub> = 125°C) |                      | IGSS               | -<br>-       | _<br>_ | -1.0<br>-1.0 | nAdc<br>μAdc |

| Gate Source Cutoff Voltage<br>(V <sub>DS</sub> = 10 Vdc, I <sub>D</sub> = 1.0 nAdc)                     | MMBFJ309<br>MMBFJ310 | VGS(off)           | -1.0<br>-2.0 | -<br>- | -4.0<br>-6.5 | Vdc          |

| ON CHARACTERISTICS                                                                                      |                      | •                  |              |        | •            | •            |

| Zero-Gate-Voltage Drain Current<br>(V <sub>DS</sub> = 10 Vdc, V <sub>GS</sub> = 0)                      | MMBFJ309<br>MMBFJ310 | IDSS               | 12<br>24     | _<br>_ | 30<br>60     | mAdc         |

| Gate-Source Forward Voltage (I <sub>G</sub> = 1.0 mAdc, V <sub>DS</sub> = 0)                            |                      | V <sub>GS(f)</sub> | _            | -      | 1.0          | Vdc          |

| SMALL-SIGNAL CHARACTERISTICS                                                                            |                      |                    |              | •      | •            | •            |

| Forward Transfer Admittance (V <sub>DS</sub> = 10 Vdc, I <sub>D</sub> = 10 mAd                          | lc, f = 1.0 kHz)     | Y <sub>fs</sub>    | 8.0          | _      | 18           | mmhos        |

| Output Admittance ( $V_{DS} = 10 \text{ Vdc}$ , $I_D = 10 \text{ mAdc}$ , $f = 1.0 \text{ k}$           | Hz)                  | lyosl              | -            | -      | 250          | μmhos        |

| Input Capacitance (V <sub>GS</sub> = -10 Vdc, V <sub>DS</sub> = 0 Vdc, f = 1.0 M                        | ИHz)                 | C <sub>iss</sub>   | -            | -      | 5.0          | pF           |

| Reverse Transfer Capacitance ( $V_{GS} = -10 \text{ Vdc}$ , $V_{DS} = 0 \text{ Vdc}$                    | Vdc, f = 1.0 MHz)    | C <sub>rss</sub>   | -            | -      | 2.5          | pF           |

| Equivalent Short–Circuit Input Noise Voltage (VDS = 10 Vdc, ID = 10 mAdc, f = 100 Hz)                   |                      | e <sub>n</sub>     | -            | 10     | _            | nV/√Hz       |

<sup>1.</sup> FR-5 =  $1.0 \times 0.75 \times 0.062$  in.

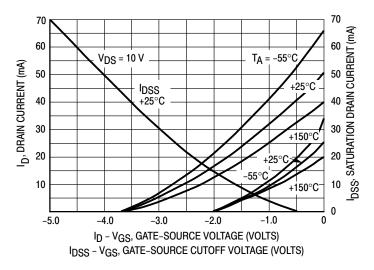

Figure 1. Drain Current and Transfer Characteristics versus Gate-Source Voltage

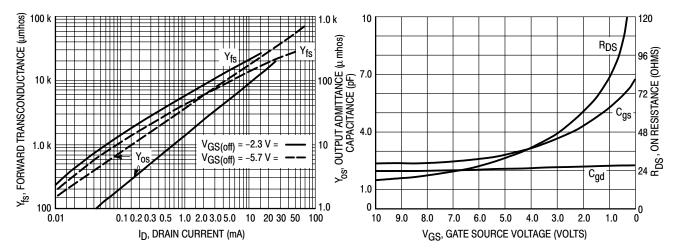

Figure 2. Common–Source Output

Admittance and Forward Transconductance

versus Drain Current

Figure 3. On Resistance and Junction Capacitance versus Gate-Source Voltage

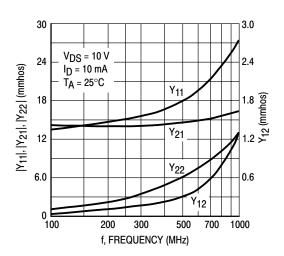

Figure 4. Common-Gate Y Parameter Magnitude versus Frequency

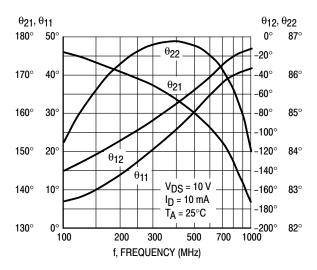

Figure 6. Common–Gate Y Parameter Phase–Angle versus Frequency

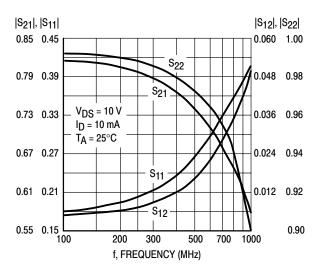

Figure 5. Common–Gate S Parameter Magnitude versus Frequency

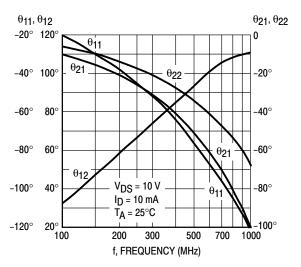

Figure 7. S Parameter Phase–Angle versus Frequency

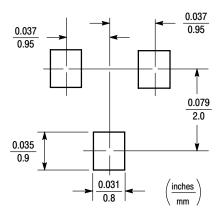

### INFORMATION FOR USING THE SOT-23 SURFACE MOUNT PACKAGE MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection

interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

SOT-23

#### **SOT-23 POWER DISSIPATION**

The power dissipation of the SOT–23 is a function of the pad size. This can vary from the minimum pad size for soldering to a pad size given for maximum power dissipation. Power dissipation for a surface mount device is determined by  $T_{J(max)}$ , the maximum rated junction temperature of the die,  $R_{\theta JA}$ , the thermal resistance from the device junction to ambient, and the operating temperature,  $T_A$ . Using the values provided on the data sheet for the SOT–23 package,  $P_D$  can be calculated as follows:

$$P_D = \frac{T_{J(max)} - T_A}{R_{\theta JA}}$$

The values for the equation are found in the maximum ratings table on the data sheet. Substituting these values into the equation for an ambient temperature  $T_A$  of 25°C, one can calculate the power dissipation of the device which in this case is 225 milliwatts.

$$P_D = \frac{150^{\circ}C - 25^{\circ}C}{556^{\circ}C/W} = 225 \text{ milliwatts}$$

The 556°C/W for the SOT-23 package assumes the use of the recommended footprint on a glass epoxy printed circuit board to achieve a power dissipation of 225 milliwatts. There are other alternatives to achieving higher power dissipation from the SOT-23 package. Another alternative would be to use a ceramic substrate or an aluminum core board such as Thermal Clad™. Using a board material such as Thermal Clad, an aluminum core board, the power dissipation can be doubled using the same footprint.

#### **SOLDERING PRECAUTIONS**

The melting temperature of solder is higher than the rated temperature of the device. When the entire device is heated to a high temperature, failure to complete soldering within a short time could result in device failure. Therefore, the following items should always be observed in order to minimize the thermal stress to which the devices are subjected.

- Always preheat the device.

- The delta temperature between the preheat and soldering should be 100°C or less.\*

- When preheating and soldering, the temperature of the leads and the case must not exceed the maximum temperature ratings as shown on the data sheet. When using infrared heating with the reflow soldering method, the difference shall be a maximum of 10°C.

- The soldering temperature and time shall not exceed 260°C for more than 10 seconds.

- When shifting from preheating to soldering, the maximum temperature gradient shall be 5°C or less.

- After soldering has been completed, the device should be allowed to cool naturally for at least three minutes.

Gradual cooling should be used as the use of forced cooling will increase the temperature gradient and result in latent failure due to mechanical stress.

- Mechanical stress or shock should not be applied during cooling.

- \* Soldering a device without preheating can cause excessive thermal shock and stress which can result in damage to the device.

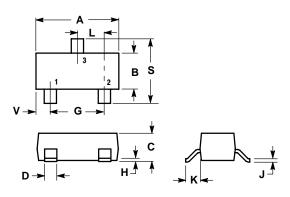

#### **PACKAGE DIMENSIONS**

SOT-23 (TO-236AB) CASE 318-08 ISSUE AF

STYLE 10: PIN 1. DRAIN 2. SOURCE 3. GATE

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

|     | INCHES |        | MILLIMETERS |       |  |

|-----|--------|--------|-------------|-------|--|

| DIM | MIN    | MAX    | MIN         | MAX   |  |

| Α   | 0.1102 | 0.1197 | 2.80        | 3.04  |  |

| В   | 0.0472 | 0.0551 | 1.20        | 1.40  |  |

| С   | 0.0350 | 0.0440 | 0.89        | 1.11  |  |

| D   | 0.0150 | 0.0200 | 0.37        | 0.50  |  |

| G   | 0.0701 | 0.0807 | 1.78        | 2.04  |  |

| Н   | 0.0005 | 0.0040 | 0.013       | 0.100 |  |

| J   | 0.0034 | 0.0070 | 0.085       | 0.177 |  |

| K   | 0.0140 | 0.0285 | 0.35        | 0.69  |  |

| L   | 0.0350 | 0.0401 | 0.89        | 1.02  |  |

| S   | 0.0830 | 0.1039 | 2.10        | 2.64  |  |

| V   | 0.0177 | 0.0236 | 0.45        | 0.60  |  |

SENSEFET is a trademark of Semiconductor Components Industries, LLC.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.