# 8-bit Proprietary Microcontroller cmos

## F<sup>2</sup>MC-8L MB89490 Series

## MB89498/F499/PV490

#### **■ DESCRIPTION**

The MB89490 series has been developed as a general-purpose version of the F<sup>2</sup>MC\*-8L family consisting of proprietary 8-bit single-chip microcontrollers.

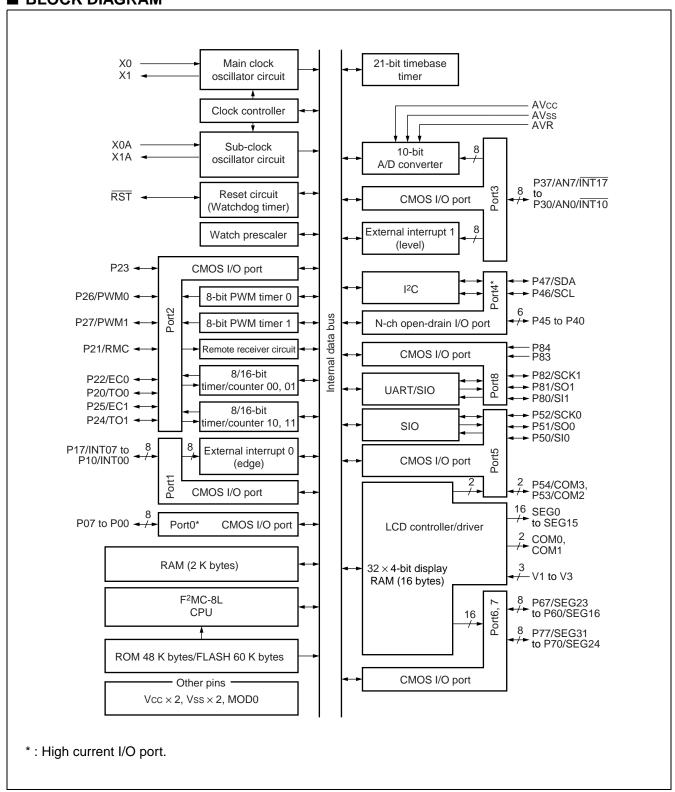

In addition to a compact instruction set, the general-purpose, single-chip microcontroller contains a variety of peripheral functions such as 21-bit timebase timer, watch prescaler, PWM timer, 8/16-bit timer/counter, remote receiver circuit, LCD controller/driver, external interrupt 0 (edge), external interrupt 1 (level), 10-bit A/D converter, UART/SIO, SIO, I<sup>2</sup>C and watchdog timer reset.

The MB89490 series is designed suitable for compact disc/radio receiver controller as well as in a wide range of applications for consumer product.

\*: F<sup>2</sup>MC is the abbreviation for Fujitsu Flexible Microcontroller.

#### **■ FEATURES**

Package

QFP, LQFP package for MB89F499, MB89498

MQFP package for MB89PV490

(Continued)

For the information for microcontroller supports, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

#### (Continued)

- High speed operating capability at low voltage

- Minimum execution time : 0.32 μs/12.5 MHz

- F2MC-8L family CPU core

Instruction set optimized for controllers

Multiplication and division instructions 16-bit arithmetic operations Branch instructions by test bit Bit manipulation instructions, etc.

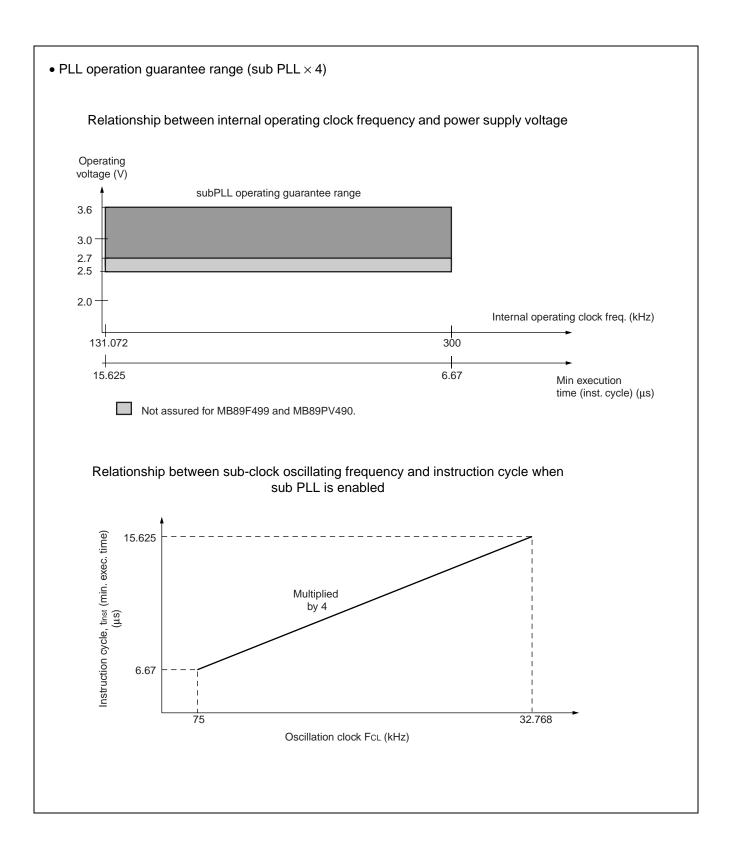

- PLL circuit for sub-clock

- Embedded for PLL clock multiplication circuit for sub-clock

- Operating clock (PLL for sub-clock) can be selected from no multiplication or 4 times of the sub-clock oscillation frequency.

- 6 timers

PWM timer × 2

8/16-bit timer/counter × 2

21-bit timebase timer

Watch prescaler

External interrupt

Edge detection (selectable edge): 8 channels

Low level interrupt (wake-up function): 8 channels

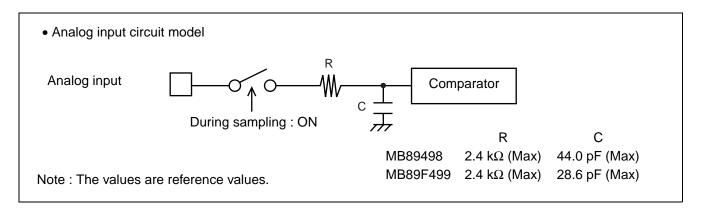

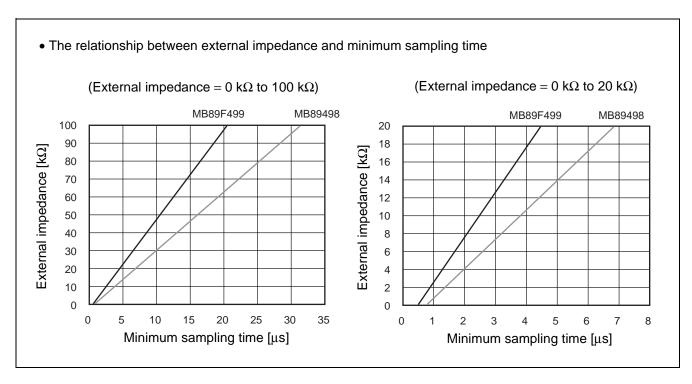

• 10-bit A/D converter (8 channels)

10-bit successive approximation type

• UART/SIO

Synchronous/asynchronous data transfer capability

SIC

Switching of synchronous data transfer capability

• LCD controller/driver

Max 32 segments output × 4 commons

- I2C interface circuit

- Remote receiver circuit

- Low-power consumption mode

Stop mode (oscillation stops so as to minimize the current consumption.)

Sleep mode (CPU stops so as to reduce the current consumption to approx. 1/3 of normal.)

Watch mode (operation except the watch prescaler stops so as to reduce the power comsumption to an extremely low level.)

Sub-clock mode

- · Watchdog timer reset

- I/O ports : Max 66 channels

### **■ PRODUCT LINEUP**

| Part number Parameter            | MB89498                                                                                                                                               | MB89F499                                                                                                 | MB89PV490                                        |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

| Classification                   | Mass production products (mask ROM product)                                                                                                           | FLASH                                                                                                    | Piggy-back<br>(For evaluation or<br>development) |  |  |  |

| ROM size                         | 48 K × 8-bit<br>(internal ROM)                                                                                                                        | 60 K × 8-bit<br>(internal FLASH)                                                                         | 60 K × 8-bit<br>(external ROM) *                 |  |  |  |

| RAM size                         | 2 K × 8-bit                                                                                                                                           | 2 K × 8-bit                                                                                              | 2 K × 8-bit                                      |  |  |  |

| CPU functions                    | Number of instructions Instruction bit length Instruction length Data bit length Minimum instruction execution time Minimum interrupt processing time | : 136<br>: 8-bit<br>: 1 to 3 bytes<br>: 1-bit, 8-bit, 16-bit<br>: 0.32 µs/12.5 MHz<br>: 2.88 µs/12.5 MHz |                                                  |  |  |  |

| Ports                            | General-purpose I/O ports (CMOS) : 56 pins Input ports (CMOS) : 2 pins N-channel open drain I/O ports : 8 pins Total : 66 pins                        |                                                                                                          |                                                  |  |  |  |

| 21-bit timebase timer            | Interrupt generation cycle (0.66 ms,                                                                                                                  | 2.6 ms, 21.0 ms, 335.5 ms                                                                                | s) at 12.5 MHz                                   |  |  |  |

| Watchdog timer                   | Reset generation cycle (167.8 ms to                                                                                                                   | 335.5 ms) at 12.5 MHz                                                                                    |                                                  |  |  |  |

| PWM timer 0, 1                   | 8-bit reload timer operation (supports 1 tinst, 8 tinst, 16 tinst, 64 tinst ) 8-bit accuracy PWM operation                                            | s square wave output and                                                                                 | operating clock period :                         |  |  |  |

| 8/16-bit timer/counter 00, 01    | Can be operated either as a 2-chanr with its own independent operating of In timer 00 or 16-bit timer/counter opinput and square wave output capab    | clock) , or as one 16-bit time<br>peration, event counter ope                                            | ner/counter.                                     |  |  |  |

| 8/16-bit timer/counter<br>10, 11 | Can be operated either as a 2-chanr with its own independent operating of In timer 10-bit or 16-bit timer/counter input and square wave output capab  | clock) , or as one 16-bit tim<br>operation, event counter o                                              | ner/counter.                                     |  |  |  |

| External interrupt 0 (edge)      | 8 independent channels (selectable edge, interrupt vector, request flag)                                                                              |                                                                                                          |                                                  |  |  |  |

| External interrupt 1 (level)     | 8 channels (low level interrupt)                                                                                                                      |                                                                                                          |                                                  |  |  |  |

| A/D converter                    | 10-bit accuracy × 8 channels<br>A/D conversion function (conversion time : 30 t <sub>inst</sub> )<br>Supports repeated activation by internal clock   |                                                                                                          |                                                  |  |  |  |

| LCD controller/driver            | Common output : 4 (Max) Segment output : 32 (Max) LCD driving power (bias) pins : 3 LCD display RAM size : 32 × 4 bits                                |                                                                                                          |                                                  |  |  |  |

| Part number Parameter   | MB89498                                                                                                                                                                                       | MB89F499                     | MB89PV490      |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|--|--|--|--|

| UART/SIO                | Synchronous/asynchronous data transfer capability<br>(Max baud rate : 97.656 Kbps at 12.5 MHz)<br>(7-bit and 8-bit with parity bit; 8-bit and 9-bit without parity bit)                       |                              |                |  |  |  |  |

| SIO                     | 8-bit serial I/O with LSB first/MSB first selectability 1 clock selectable from 4 operation clock (1 external shift clock and 3 internal shift clock: 0.64 μs, 2.56 μs, 10.24 μs at 12.5 MHz) |                              |                |  |  |  |  |

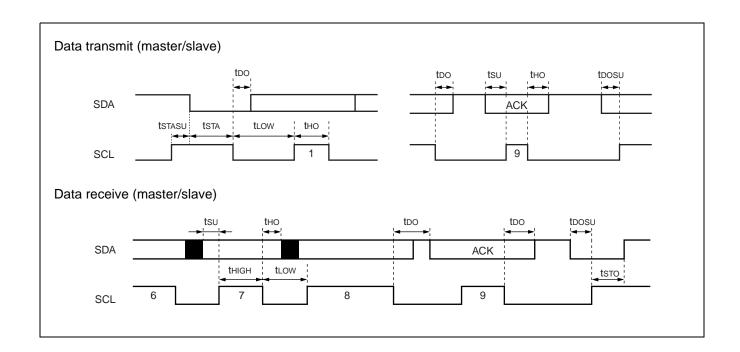

| I <sup>2</sup> C        | 1 channel<br>(Use a 2-wire protocol to cor                                                                                                                                                    | mmunicate with other device) |                |  |  |  |  |

| Remote receiver circuit | Selectable maximum noise width removal Reversible input polarity                                                                                                                              |                              |                |  |  |  |  |

| Standby mode            | Sleep mode, stop mode, watch mode and sub-clock mode                                                                                                                                          |                              |                |  |  |  |  |

| Process                 | CMOS                                                                                                                                                                                          |                              |                |  |  |  |  |

| Operating voltage       | 2.2 V to 3.6 V                                                                                                                                                                                | 2.7 V to 3.6 V               | 2.7 V to 3.6 V |  |  |  |  |

<sup>\*:</sup> Use MBM27C512 as the external ROM.

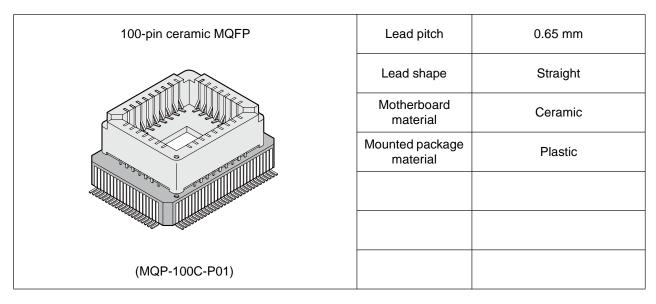

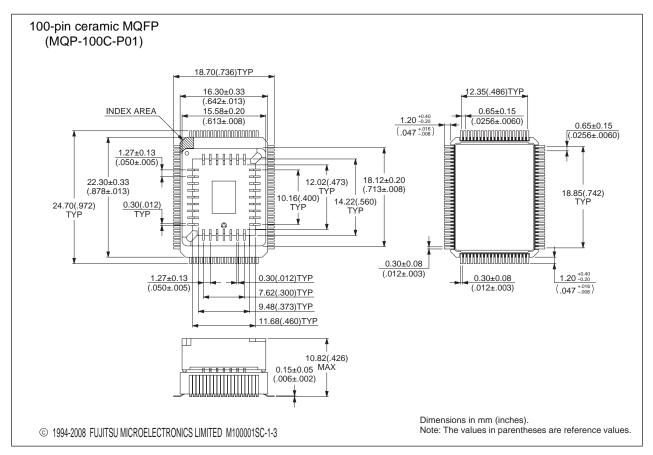

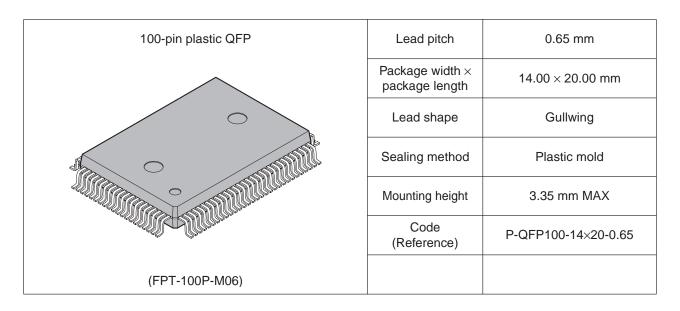

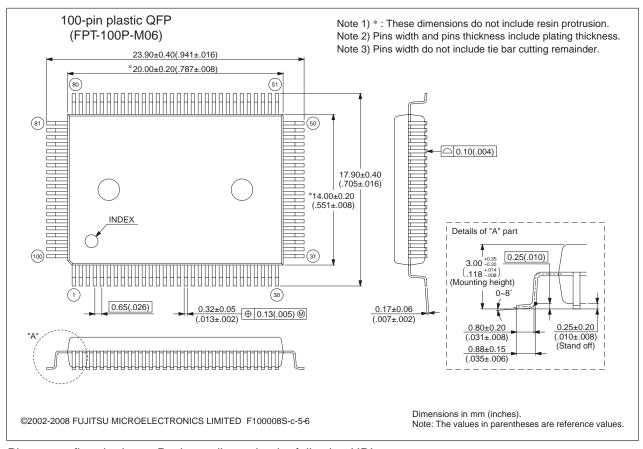

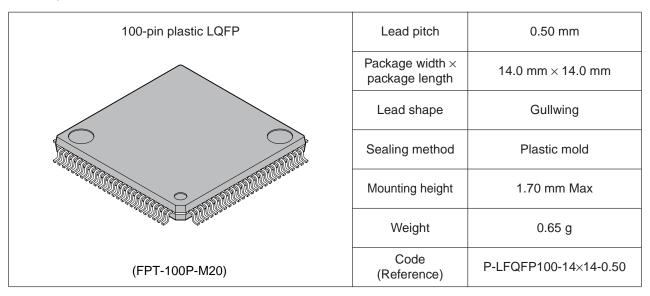

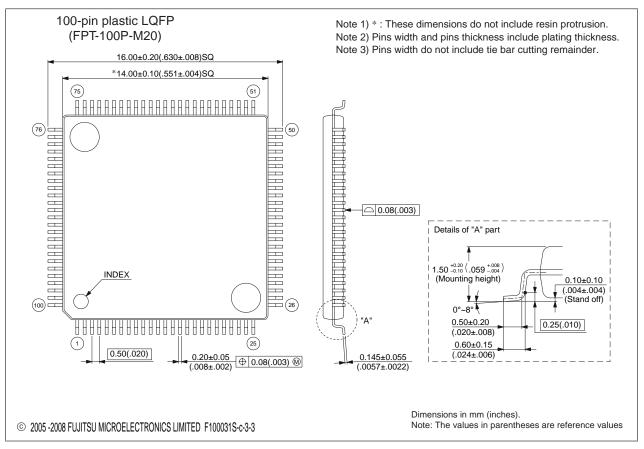

#### ■ PACKAGE AND CORRESPONDING PRODUCTS

| Part number Parameter | MB89498 | MB89F499 | MB89PV490 |

|-----------------------|---------|----------|-----------|

| FPT-100P-M06          | 0       | 0        | ×         |

| FPT-100P-M20          | 0       | 0        | ×         |

| MQP-100C-P01          | ×       | ×        | 0         |

O : Availabe × : Not available

#### **■ DIFFERENCES AMONG PRODUCTS**

#### 1. Memory Size

Before evaluating using the piggy-back product, verify its differences from the product that will be actually used. Take particular care on the following point: The stack area is set at the upper limit of the RAM.

#### 2. Current Consumption

- For the MB89PV490, add the current consumed by the EPROM mounted in the piggy-back socket.

- When operating at low speed, the current consumed by the FLASH product is greater than that for the mask ROM product. However, the current consumption is roughly the same in sleep and stop mode.

- For more information, see "■ ELECTRICAL CHARACTERISTICS".

#### 3. Oscillation Stabilization Wait Time after Power-on Reset

- For MB89PV490 and MB89F499, the power-on stabilization wait time cannot be selected after power-on reset.

- For MB89498, the power-on stabilization wait time can be selected after power-on reset.

- For more information, please refer to "■ MASK OPTIONS".

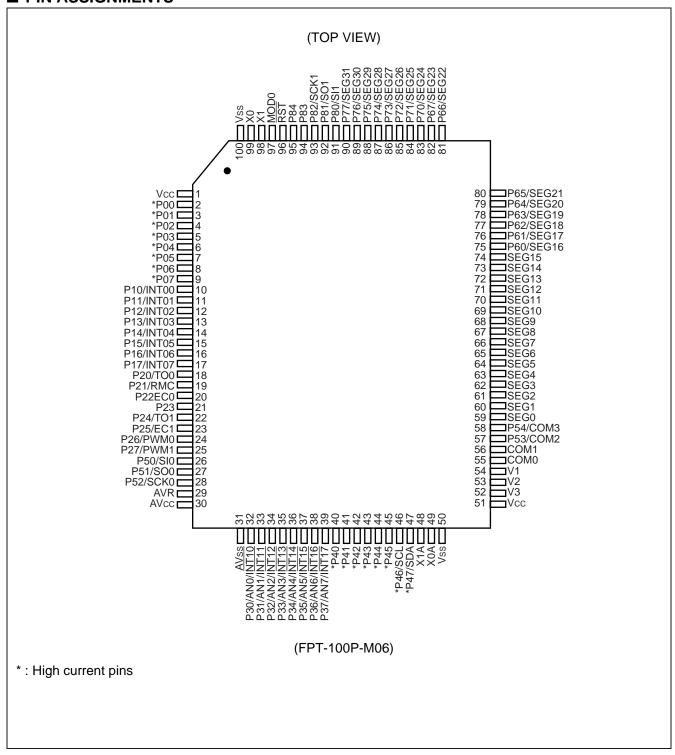

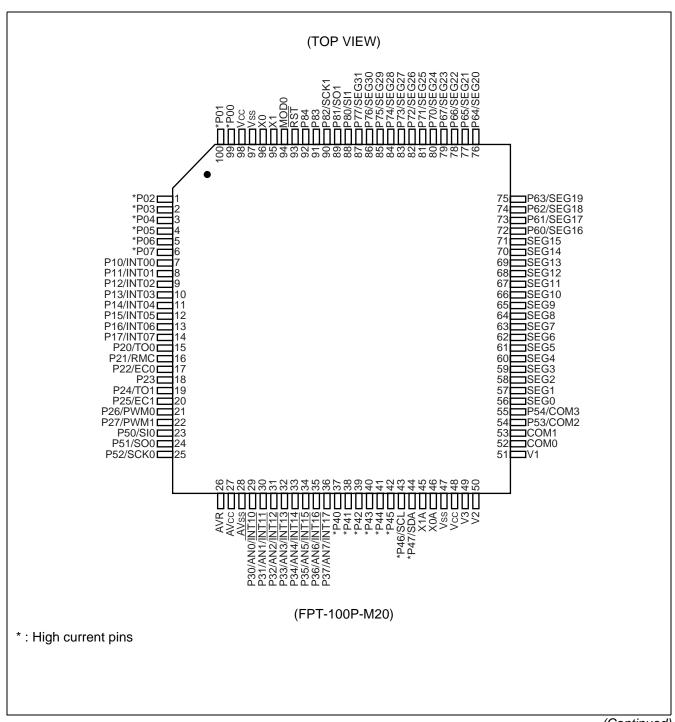

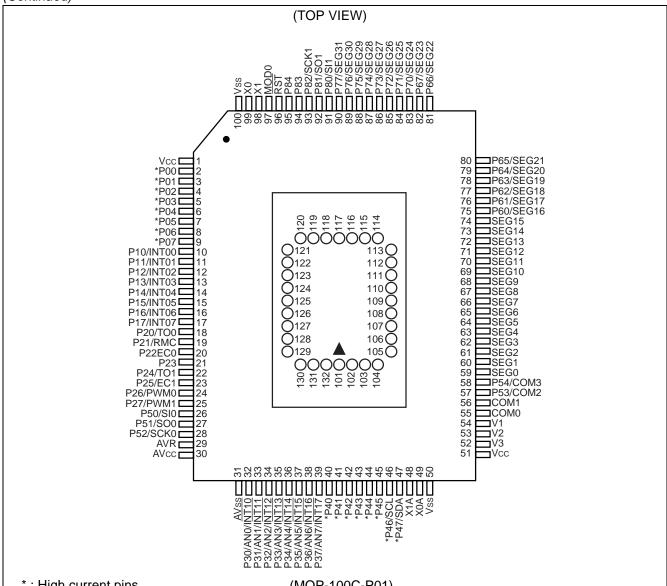

#### **■ PIN ASSIGNMENTS**

\*: High current pins

(MQP-100C-P01)

Pin assignment on package top (MB89PV490 only)

| Pin no. | Pin name |

|---------|----------|---------|----------|---------|----------|---------|----------|---------|----------|

| 101     | N.C.     | 108     | А3       | 115     | O3       | 122     | O8       | 129     | A8       |

| 102     | A15      | 109     | A2       | 116     | Vss      | 123     | CE       | 130     | A13      |

| 103     | A12      | 110     | A1       | 117     | N.C.     | 124     | A10      | 131     | A14      |

| 104     | A7       | 111     | A0       | 118     | O4       | 125     | ŌĒ       | 132     | Vcc      |

| 105     | A6       | 112     | N.C.     | 119     | O5       | 126     | N.C.     |         |          |

| 106     | A5       | 113     | 01       | 120     | O6       | 127     | A11      |         |          |

| 107     | A4       | 114     | O2       | 121     | 07       | 128     | A9       |         |          |

N.C.: As connected internally, do not use.

### **■ PIN DESCRIPTION**

| Pin nu           | ımber    |                                      |                     |                                                                                                                                                                                                                             |

|------------------|----------|--------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MQFP*1/<br>QFP*2 | LQFP*3   | Pin name                             | I/O circuit<br>type | Function                                                                                                                                                                                                                    |

| 99               | 96       | X0                                   |                     | Connection pins for a crystal or other oscillator circuit.                                                                                                                                                                  |

| 98               | 95       | X1                                   | А                   | An external clock can be connected to X0. In this case, leave X1 open.                                                                                                                                                      |

| 49               | 46       | X0A                                  |                     | Connection pins for a crystal or other oscillator circuit.                                                                                                                                                                  |

| 48               | 45       | X1A                                  | А                   | An external clock can be connected to X0A. In this case, leave X1A open.                                                                                                                                                    |

| 97               | 94       | MOD0                                 | В                   | Input pin for setting the memory access mode. Connect directly to Vss.                                                                                                                                                      |

| 95, 94           | 92, 91   | P84, P83                             | J                   | General-purpose CMOS input port.                                                                                                                                                                                            |

| 96               | 93       | RST                                  | С                   | Reset I/O pin. The pin is an N-ch open-drain type with pull-up resistor and hysteresis input. The pin outputs an "L" level when an internal reset request is present. Inputting an "L" level initializes internal circuits. |

| 2 to 9           | 99 to 6  | P00 to P07                           | D                   | General-purpose CMOS I/O port.                                                                                                                                                                                              |

| 10 to 17         | 7 to 14  | P10/INT00<br>to<br>P17/INT07         | E                   | General-purpose CMOS I/O port. The pin is shared with external interrupt 0 input.                                                                                                                                           |

| 18               | 15       | P20/TO0                              | F                   | General-purpose CMOS I/O port. The pin is shared with 8/16-bit timer/counter 00 and 01 output.                                                                                                                              |

| 19               | 16       | P21/RMC                              | E                   | General-purpose CMOS I/O port. The pin is shared with remote receiver input.                                                                                                                                                |

| 20               | 17       | P22/EC0                              | E                   | General-purpose CMOS I/O port. The pin is shared with 8/16-bit timer/counter 00 and 01 input.                                                                                                                               |

| 21               | 18       | P23                                  | F                   | General-purpose CMOS I/O port.                                                                                                                                                                                              |

| 22               | 19       | P24/TO1                              | F                   | General-purpose CMOS I/O port. The pin is shared with 8/16-bit timer/counter 10 and 11 output.                                                                                                                              |

| 23               | 20       | P25/EC1                              | E                   | General-purpose CMOS I/O port. The pin is shared with 8/16-bit timer/counter 10 and 11 input.                                                                                                                               |

| 24               | 21       | P26/PWM0                             | F                   | General-purpose CMOS I/O port. The pin is shared with PWM0 output.                                                                                                                                                          |

| 25               | 22       | P27/PWM1                             | F                   | General-purpose CMOS I/O port. The pin is shared with PWM1 output.                                                                                                                                                          |

| 32 to 39         | 29 to 36 | P30/AN0/INT10<br>to<br>P37/AN7/INT17 | G                   | General-purpose CMOS I/O port. The pin is shared with external interrupt 1 input and A/D converter input.                                                                                                                   |

| 40 to 45         | 37 to 42 | P40 to P45                           | Н                   | General-purpose N-ch open-drain I/O port.                                                                                                                                                                                   |

| 46               | 43       | P46/SCL                              | Н                   | General-purpose N-ch open-drain I/O port.<br>The pin is shared with I <sup>2</sup> C clock I/O.                                                                                                                             |

#### (Continued)

| Pin number       |               |                              | 1/O el ====!        |                                                                                             |  |  |

|------------------|---------------|------------------------------|---------------------|---------------------------------------------------------------------------------------------|--|--|

| MQFP*1/<br>QFP*2 | LQFP*3        | Pin name                     | I/O circuit<br>type | Function                                                                                    |  |  |

| 47               | 44            | P47/SDA                      | Н                   | General-purpose N-ch open-drain I/O port. The pin is shared with I <sup>2</sup> C data I/O. |  |  |

| 26               | 23            | P50/SI0                      | Е                   | General-purpose CMOS I/O port. The pin is shared with SIO data input.                       |  |  |

| 27               | 24            | P51/SO0                      | F                   | General-purpose CMOS I/O port. The pin is shared with SIO data output.                      |  |  |

| 28               | 25            | P52/SCK0                     | E                   | General-purpose CMOS I/O port. The pin is shared with SIO clock I/O.                        |  |  |

| 57               | 54            | P53/COM2                     | F/I                 | General-purpose CMOS I/O port. The pin is shared with the LCD common output.                |  |  |

| 58               | 55            | P54/COM3                     | F/I                 | General-purpose CMOS I/O port. The pin is shared with the LCD common output.                |  |  |

| 75 to 82         | 72 to 79      | P60/SEG16<br>to<br>P67/SEG23 | F/I                 | General-purpose CMOS I/O port. The pin is shared with LCD segment output.                   |  |  |

| 83 to 90         | 80 to 87      | P70/SEG24<br>to<br>P77/SEG31 | F/I                 | General-purpose CMOS I/O port. The pin is shared with LCD segment output.                   |  |  |

| 91               | 88            | P80/SI1                      | E                   | General-purpose CMOS I/O port. The pin is shared with UART/SIO data input.                  |  |  |

| 92               | 89            | P81/SO1                      | F                   | General-purpose CMOS I/O port. The pin is shared with UART/SIO data output.                 |  |  |

| 93               | 90            | P82/SCK1                     | E                   | General-purpose CMOS I/O port. The pin is shared with UART/SIO clock I/O.                   |  |  |

| 59 to 74         | 56 to 71      | SEG0 to<br>SEG15             | I                   | LCD segment output-only pin.                                                                |  |  |

| 55, 56           | 52, 53        | COM0,<br>COM1                | I                   | LCD common output-only pin.                                                                 |  |  |

| 54, 53,<br>52    | 51, 50,<br>49 | V1 to V3                     |                     | LCD driving power supply pin.                                                               |  |  |

| 1, 51            | 98, 48        | Vcc                          | _                   | Power supply pin.                                                                           |  |  |

| 50, 100          | 47, 97        | Vss                          | _                   | Power supply pin (GND) .                                                                    |  |  |

| 30               | 27            | AVcc                         | _                   | A/D converter power supply pin.                                                             |  |  |

| 29               | 26            | AVR                          |                     | A/D converter reference voltage input pin.                                                  |  |  |

| 31               | 28            | AVss                         | _                   | A/D converter power supply pin. Use at the same voltage level as Vss.                       |  |  |

\*1: MQP-100C-P01 \*2: FPT-100P-M06 \*3: FPT-100P-M20

#### • External EPROM Socket (MB89PV490 only)

| Pin number |          | 1/O |                                                             |  |  |  |

|------------|----------|-----|-------------------------------------------------------------|--|--|--|

| MQFP*      | Pin name | I/O | Function                                                    |  |  |  |

| 102        | A15      |     |                                                             |  |  |  |

| 131        | A14      |     |                                                             |  |  |  |

| 130        | A13      |     |                                                             |  |  |  |

| 103        | A12      |     |                                                             |  |  |  |

| 127        | A11      |     |                                                             |  |  |  |

| 124        | A10      |     |                                                             |  |  |  |

| 128        | A9       |     |                                                             |  |  |  |

| 129        | A8       | 0   | Address output pins.                                        |  |  |  |

| 104        | A7       | · · | Tradition output princi                                     |  |  |  |

| 105        | A6       |     |                                                             |  |  |  |

| 106        | A5       |     |                                                             |  |  |  |

| 107        | A4       |     |                                                             |  |  |  |

| 108        | A3       |     |                                                             |  |  |  |

| 109        | A2       |     |                                                             |  |  |  |

| 110        | A1       |     |                                                             |  |  |  |

| 111        | A0       |     |                                                             |  |  |  |

| 122        | O8       |     |                                                             |  |  |  |

| 121        | 07       |     |                                                             |  |  |  |

| 120        | 06       |     |                                                             |  |  |  |

| 119        | O5       | 1   | Data input pins.                                            |  |  |  |

| 118        | 04       | -   |                                                             |  |  |  |

| 115        | 03       |     |                                                             |  |  |  |

| 114        | 02       |     |                                                             |  |  |  |

| 113        | O1       |     |                                                             |  |  |  |

| 101        |          |     |                                                             |  |  |  |

| 112        | N.C.     |     | Internally connected pins. Always leave open.               |  |  |  |

| 117        | 14.0.    |     | Internally conflicted pills. Always leave open.             |  |  |  |

| 126        |          |     |                                                             |  |  |  |

| 116        | Vss      | 0   | Power supply pin (GND) .                                    |  |  |  |

| 123        | CE       | 0   | Chip enable pin for the EPROM. Outputs "H" in standby mode. |  |  |  |

| 125        | ŌĒ       | 0   | Output enable pin for the EPROM. Always outputs "L".        |  |  |  |

| 132        | Vcc      | 0   | Power supply pin for the EPROM.                             |  |  |  |

<sup>\*:</sup> MQP-100C-P01

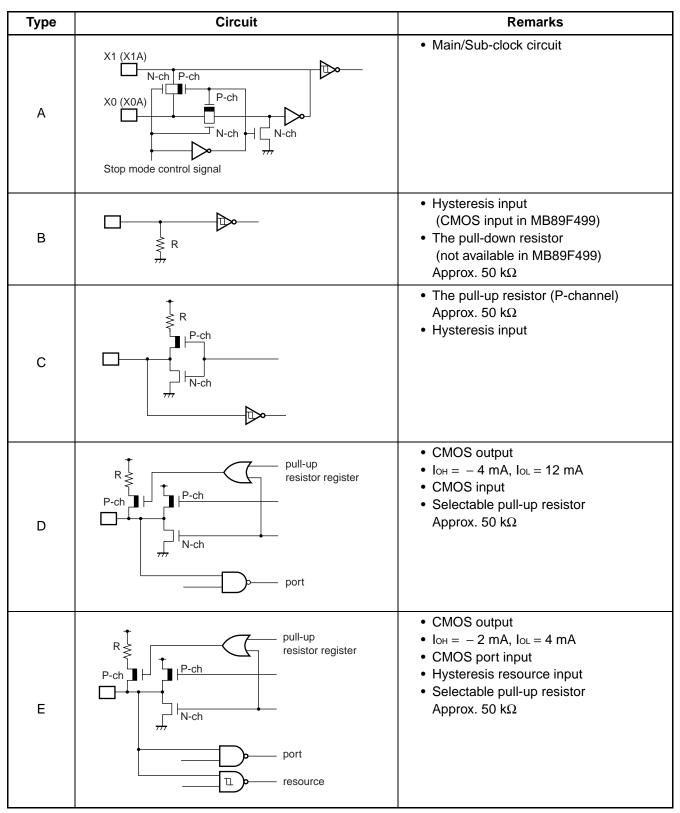

#### **■ I/O CIRCUIT TYPE**

| •    | Continued)                   |                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Type | Circuit                      | Remarks                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| F    | P-ch P-ch Port               | <ul> <li>CMOS output</li> <li>IoH = -2 mA, IoL = 4 mA</li> <li>CMOS input</li> <li>Selectable pull-up resistor<br/>Approx. 50 kΩ</li> </ul>                                                                                  |  |  |  |  |  |  |  |

| G    | P-ch port resource analog    | <ul> <li>CMOS output</li> <li>IOH = -2 mA, IOL = 4 mA</li> <li>CMOS port input</li> <li>VIH = 0.85 Vcc, VIL = 0.5 Vcc resource input</li> <li>Analog input</li> <li>Selectable pull-up resistor<br/>Approx. 50 kΩ</li> </ul> |  |  |  |  |  |  |  |

| Н    | N-ch port/resource           | <ul> <li>N-ch open-drain output</li> <li>IoL = 15 mA</li> <li>CMOS port input</li> <li>CMOS resource input</li> <li>5 V tolerance</li> </ul>                                                                                 |  |  |  |  |  |  |  |

| ı    | P-ch<br>N-ch<br>P-ch<br>N-ch | LCD segment output                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| J    |                              | CMOS input                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

#### **■ HANDLING DEVICES**

#### 1. Preventing Latch-up

Latch-up may occur on CMOS IC if voltage higher than V<sub>CC</sub> or lower than V<sub>SS</sub> is applied to input and output pins other than medium- to high-voltage pins or if higher than the voltage which shows on "1. Absolute Maximum Ratings" in "■ ELECTRICAL CHARACTERISTICS" is applied between V<sub>CC</sub> and V<sub>SS</sub>.

When latch-up occurs, power supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the maximum ratings.

Also, take care to prevent the analog power supply (AVcc and AVR) and analog input from exceeding the digital power supply (Vcc) when the analog system power supply is turned on and off.

#### 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistor.

#### 3. Treatment of Power Supply Pins on Microcontrollers with A/D

Connect to be AVcc = Vcc and AVss = AVR = Vss even if the A/D is not in use.

#### 4. Treatment of N.C. Pins

Be sure to leave (internally connected) N.C. pins open.

#### 5. Power Supply Voltage Stabilization

Although Vcc power supply voltage is assured to operate within the rated range, a rapid fluctuation of the voltage could cause malfunctions, even if it occurs within the rated range. As stabilization guidelines, it is recommended to control voltage fluctuation so that Vcc ripple fluctuations (P-P value) will be less than 10% of the standard Vcc value at the commercial frequency (50 Hz to 60 Hz) and the transient fluctuation rate will be less than 0.1 V/ms at the time of a momentary fluctuation such as when power is switched.

#### 6. Precautions when Using an External Clock

Even when an external clock is used, oscillation stabilization time is required for power-on reset and wake-up from stop mode.

#### 7. Treatment of Unused dedicated LCD pins

When dedicated LCD pins are not in use, keep them open.

#### ■ PROGRAMMING AND ERASING FLASH MEMORY ON THE MB89F499

#### 1. Flash Memory

The flash memory is located between 1000H and FFFFH in the CPU memory map and incorporates a flash memory interface circuit that allows read access and program access from the CPU to be performed in the same way as mask ROM. Programming and erasing flash memory is also performed via the flash memory interface circuit by executing instructions in the CPU. This enables the flash memory to be updated in place under the control of the internal CPU, providing an efficient method of updating program and data.

#### 2. Flash Memory Features

- 60K bytes × 8-bit configuration (16 K + 8 K + 8 K + 28 K sectors)

- Automatic algorithm (Embedded algorithm : Equivalent to MBM29LV200)

- Includes an erase pause and erase restart function

- Data polling and toggle bit for detection of program/erase completion

- Detection of program/erase completion via CPU interrupt

- Compatible with JEDEC-standard commands

- Sector Protection (sectors can be combined in any combination)

- No. of program/erase cycles: 10,000 (Min)

#### 3. Procedure for Programming and Erasing Flash Memory

Programming and reading flash memory cannot be performed at the same time. Accordingly, to program or erase data to the flash memory, the program must first be copied from flash memory to RAM so that programming can be performed without program access from flash memory.

#### 4. Flash Memory Register

Flash memory control status register (FMCS)

| Address | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3    | Bit 2    | Bit 1 | Bit 0    | Initial value |

|---------|-------|--------|-------|-------|----------|----------|-------|----------|---------------|

| 007Ан   | INTE  | RDYINT | WE    | RDY   | Reserved | Reserved | _     | Reserved | 000Х00-0в     |

|         | R/W   | R/W    | R/W   | R     | R/W      | R/W      | _     | R/W      |               |

|         |       |        |       |       |          |          |       |          |               |

#### 5. Sector Configuration

The table below shows the sector configuration of flash memory and lists the addresses of each sector during CPU access and a flash memory programming.

· Sector configuration of flash memory

| Flash Memory | CPU Address                            | Programmer Address* |

|--------------|----------------------------------------|---------------------|

| 16 K bytes   | FFFF <sub>H</sub> to C000 <sub>H</sub> | 1FFFFн to 1C000н    |

| 8 K bytes    | BFFF <sub>H</sub> to A000 <sub>H</sub> | 1BFFFн to 1A000н    |

| 8 K bytes    | 9FFFн to 8000н                         | 19FFFн to 18000н    |

| 28 K bytes   | 7FFFн to 1000н                         | 17FFFн to 11000н    |

<sup>\* :</sup> The programmer address is the address to be used instead of the CPU address when programming data from a parallel flash memory programmer. Use the programmer address on programming or erasing using a general-purpose programmer.

#### ■ PROGRAMMING TO THE EPROM WITH PIGGY-BACK/EVALUATION DEVICE

#### 1. EPROM for Use

MBM27C512-20TV

#### 2. Memory Space

Memory space corresponding to EPROM writer is shown in the diagram below.

#### 3. Programming to the EPROM

- (1) Set the EPROM programmer to the MBM27C512.

- (2) Load program data into the EPROM programmer at 1000<sub>H</sub> to FFFFH.

- (3) Program to 1000<sub>H</sub> to FFFF<sub>H</sub> with the EPROM programmer.

#### **■ BLOCK DIAGRAM**

#### **■ CPU CORE**

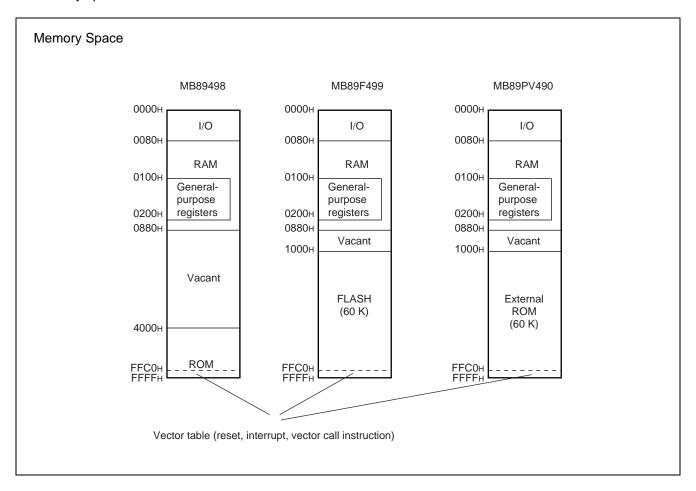

#### 1. Memory Space

The microcontrollers of the MB89490 series offer a memory space of 64K bytes for storing all of I/O, data, and program areas. The I/O area is located the lowest address. The data area is provided immediately above the I/O area. The data area can be divided into register, stack, and direct areas according to the application. The program area is located at exactly the opposite end, that is, near the highest address. Provide the tables of interrupt/reset vectors and vector call instructions toward the highest address within the program area. The memory space of the MB89490 series is structured as illustrated below.

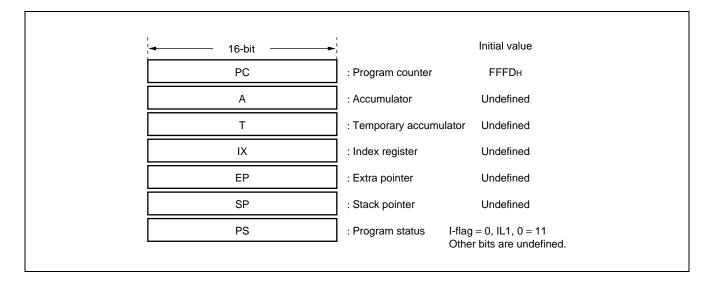

#### 2. Registers

The F<sup>2</sup>MC-8L family has 2 types of registers; dedicated registers in the CPU and general-purpose registers in the memory. The following registers are provided:

Program counter (PC) : A 16-bit register for indicating instruction storage positions.

Accumulator (A) : A 16-bit temporary register for storing arithmetic operations, etc. When the

instruction is an 8-bit data processing instruction, the lower byte is used.

Temporary accumulator (T): A 16-bit register for performing arithmetic operations with the accumulator.

When the instruction is an 8-bit data processing instruction, the lower byte is used.

Index register (IX) : A 16-bit register for index modification.

Extra pointer (EP) : A 16-bit pointer for indicating a memory address. Stack pointer (SP) : A 16-bit register for indicating a stack area.

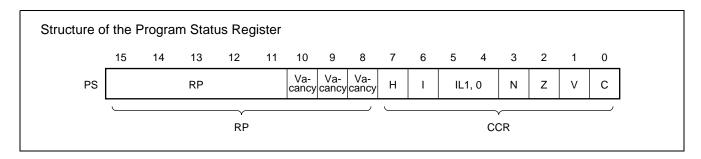

Program status (PS) : A 16-bit register for storing a register pointer and condition code.

The PS can further be divided into higher 8-bit for use as a register bank pointer (RP) and the lower 8-bit for use as a condition code register (CCR). (See the diagram below.)

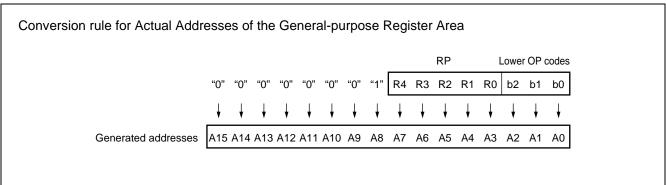

The RP indicates the address of the register bank currently in use. The relationship between the pointer contents and the actual address is based on the conversion rule illustrated below.

The CCR consists of bits indicating the results of arithmetic operations and the contents of transfer data and bits for controlling the CPU operations at the time of an interrupt.

H-flag: Set to "1" when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation. Clear to "0" otherwise. This flag is for decimal adjustment instructions.

I-flag: Interrupt is allowed when this flag is set to "1". Interrupt is prohibited when the flag is set to "0". Clear to "0" at reset.

IL1, 0: Indicates the level of the interrupt currently allowed. Processes an interrupt only if its request is higher than the value indicated by this bit.

| IL1 | IL0 | Interrupt level | High-low |

|-----|-----|-----------------|----------|

| 0   | 0   | 1               | High     |

| 0   | 1   | 1               | <b>↑</b> |

| 1   | 0   | 2               | <b>↓</b> |

| 1   | 1   | 3               | Low      |

N-flag: Set to "1" if the MSB is set to "1" as the result of an arithmetic operation. Clear to "0" otherwise.

Z-flag: Set to "1" when an arithmetic operation results in "0". Clear to "0" otherwise.

V-flag: Set to "1" if the complement on 2 overflows as a result of an arithmetic operation. Clear to "0" if the overflow does not occur.

C-flag: Set to "1" when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Clear to "0" otherwise. Set to the shift-out value in the case of a shift instruction.

The following general-purpose registers are provided:

General-purpose registers: An 8-bit register for storing data

The general-purpose registers are 8-bit and located in the register banks of the memory.

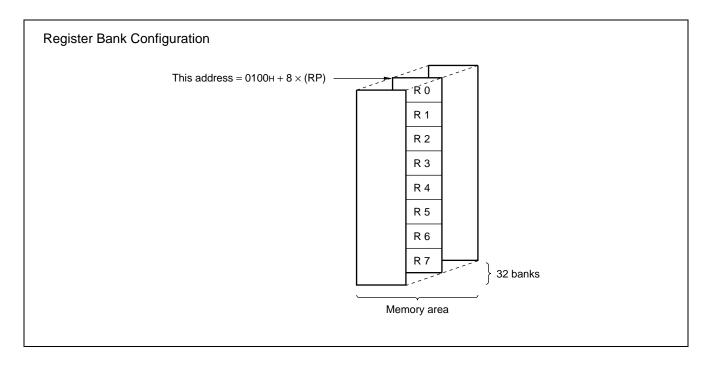

1 bank contains 8 registers. Up to a total of 32 banks can be used on the MB89490 series. The bank currently in use is indicated by the register bank pointer (RP) .

### ■ I/O MAP

| Address         | Register name | Register description                    | Read/Write | Initial value |

|-----------------|---------------|-----------------------------------------|------------|---------------|

| 00н             | PDR0          | Port 0 data register                    | R/W        | XXXXXXXXB     |

| 01н             | DDR0          | Port 0 direction register               | W*         | 0000000В      |

| 02н             | PDR1          | Port 1 data register                    | R/W        | XXXXXXXXB     |

| 03н             | DDR1          | Port 1 direction register               | W*         | 0000000в      |

| 04н             | PDR2          | Port 2 data register                    | R/W        | 0000000В      |

| 05н             |               | (Reserved)                              |            |               |

| 06н             | DDR2          | Port 2 direction register               | R/W        | 0000000в      |

| 07н             | SYCC          | System clock control register           | R/W        | Х-1ММ100в     |

| 08н             | STBC          | Standby control register                | R/W        | 00010XXXв     |

| 09н             | WDTC          | Watchdog timer control register         | W*         | 0XXXXв        |

| ОАн             | TBTC          | Timebase timer control register         | R/W        | 00000в        |

| 0Вн             | WPCR          | Watch prescaler control register        | R/W        | 000000в       |

| 0Сн             | PDR3          | Port 3 data register                    | R/W        | XXXXXXXXB     |

| 0Дн             | DDR3          | Port 3 direction register               | R/W        | 11111111в     |

| 0Ен             | RSFR          | Reset flag register                     | R          | ХХХХв         |

| 0Fн             | PDR4          | Port 4 data register                    | R/W        | 11111111в     |

| 10н             | PDR5          | Port 5 data register                    | R/W        | XXXXXB        |

| 11н             | DDR5          | Port 5 direction register               | R/W        | 00000в        |

| 12н             | PDR6          | Port 6 data register                    | R/W        | XXXXXXXXB     |

| 13н             | DDR6          | Port 6 direction register               | R/W        | 0000000в      |

| <b>14</b> H     | PDR7          | Port 7 data register                    | R/W        | XXXXXXXX      |

| 15н             | DDR7          | Port 7 direction register               | R/W        | 0000000в      |

| 16н             | PDR8          | Port 8 data register                    | R/W        | XXXXXB        |

| 17н             | DDR8          | Port 8 direction register               | R/W        | 00000в        |

| 18н             | EIC0          | External interrupt 0 control register 0 | R/W        | 0000000В      |

| 19н             | EIC1          | External interrupt 0 control register 1 | R/W        | 0000000в      |

| 1Ан             | EIC2          | External interrupt 0 control register 2 | R/W        | 0000000в      |

| 1Вн             | EIC3          | External interrupt 0 control register 3 | R/W        | 0000000в      |

| 1Сн             | EIE1          | External interrupt 1 enable register    | R/W        | 0000000в      |

| 1Dн             | EIF1          | External interrupt 1 flag register      | R/W        | Ов            |

| 1Ен             | SMR           | Serial mode register                    | R/W        | 0000000в      |

| 1F <sub>H</sub> | SDR           | Serial data register                    | R/W        | XXXXXXXXB     |

| 20н             | T01CR         | Timer 01 control register               | R/W        | 000000Х0в     |

| 21н             | T00CR         | Timer 00 control register               | R/W        | 000000Х0в     |

| 22н             | T01DR         | Timer 01 data register                  | R/W        | XXXXXXXXB     |

| Address    | Register name | Register description                    | Read/Write | Initial value         |

|------------|---------------|-----------------------------------------|------------|-----------------------|

| 23н        | T00DR         | Timer 00 data register                  | R/W        | XXXXXXXXB             |

| 24н        | T11CR         | Timer 11 control register               | R/W        | 000000Х0в             |

| 25н        | T10CR         | Timer 10 control register               | R/W        | 000000Х0в             |

| 26н        | T11DR         | Timer 11 data register                  | R/W        | XXXXXXXX              |

| 27н        | T10DR         | Timer 10 data register                  | R/W        | XXXXXXXX              |

| 28н        | ADER          | A/D input enable register               | R/W        | 11111111в             |

| 29н        | ADC0          | A/D control register 0                  | R/W        | -00000Х0в             |

| 2Ан        | ADC1          | A/D control register 1                  | R/W        | -000001в              |

| 2Вн        | ADDH          | A/D data register (Upper byte)          | R          | XX <sub>B</sub>       |

| 2Сн        | ADDL          | A/D data register (Lower byte)          | R          | XXXXXXXX              |

| 2Dн        | CNTR0         | PWM 0 timer control register            | R/W        | 0-000000в             |

| 2Ен        | COMR0         | PWM 0 timer compare register            | W*         | XXXXXXXXB             |

| 2Fн        | SMC0          | UART/SIO serial mode control register   | R/W        | 0000000в              |

| 30н        | SMC1          | UART/SIO serial mode control register   | R/W        | 0000000в              |

| 31н        | SSD           | UART/SIO serial status/data register    | R/W        | 00001в                |

| 32н        | SIDR/SODR     | UART/SIO serial data register           | R/W        | XXXXXXXXB             |

| 33н        | SRC           | UART/SIO serial rate control register   | R/W        | XXXXXXXX              |

| 34н        | CNTR1         | PWM 1 timer control register            | R/W        | 0-000000в             |

| 35н        | COMR1         | PWM 1 timer compare register            | W*         | XXXXXXXXB             |

| 36н        | IBSR          | I <sup>2</sup> C bus status register    | R          | 0000000В              |

| 37н        | IBCR          | I <sup>2</sup> C bus control register   | R/W        | 0000000В              |

| 38н        | ICCR          | I <sup>2</sup> C clock control register | R/W        | 000XXXXXB             |

| 39н        | IADR          | I <sup>2</sup> C address register       | R/W        | -XXXXXXX <sub>B</sub> |

| ЗАн        | IDAR          | I <sup>2</sup> C data register          | R/W        | XXXXXXXXB             |

| 3Вн        | PLLCR         | Sub PLL control register                | R/W        | 0000в                 |

| 3Cн to 3Fн |               | (Reserved)                              | -1         |                       |

| 40н        | RMN           | Remote control counter register         | R          | XXXXXXXXB             |

| 41н        | RMC           | Remote control control register         | R/W        | 0000000В              |

| 42н        | RMS           | Remote control status register          | R/W        | 0Х000001в             |

| 43н        | RMD           | Remote control FIFO data register       | R          | XXXX <sub>B</sub>     |

| 44н        | RMCD0         | Remote control compare register 0       | R/W        | 11111111в             |

| 45н        | RMCD1         | Remote control compare register 1       | R/W        | 11111111в             |

| 46н        | RMCD2         | Remote control compare register 2       | R/W        | 11111111в             |

| 47н        | RMCD3         | Remote control compare register 3       | R/W        | 11111111в             |

| 48н        | RMCD4         | Remote control compare register 4       | R/W        | 11111111в             |

#### (Continued)

| Address      | Register name | Register description                     | Read/Write | Initial value |

|--------------|---------------|------------------------------------------|------------|---------------|

| 49н          | RMCD5         | Remote control compare register 5        | R/W        | 11111111в     |

| 4Ан          | RMCI          | Remote interrupt register                | R/W        | 0000-000в     |

| 4Вн to 5Dн   |               | (Reserved)                               |            |               |

| 5Ен          | LOCR          | LCD controller output control register   | R/W        | -000000в      |

| 5 <b>F</b> н | LCR           | LCD controller control register          | R/W        | 00010000в     |

| 60н to 6Fн   | VRAM          | LCD data RAM                             | R/W        | XXXXXXXX      |

| 70н          | PUCR0         | Port 0 pull up resistor control register | R/W        | 11111111в     |

| 71н          | PUCR1         | Port 1 pull up resistor control register | R/W        | 11111111в     |

| 72н          | PUCR2         | Port 2 pull up resistor control register | R/W        | 11111111в     |

| 73н          | PUCR3         | Port 3 pull up resistor control register | R/W        | 11111111в     |

| 74н          | PUCR5         | Port 5 pull up resistor control register | R/W        | 11111в        |

| 75н          | PUCR6         | Port 6 pull up resistor control register | R/W        | 11111111в     |

| 76н          | PUCR7         | Port 7 pull up resistor control register | R/W        | 11111111в     |

| 77н          | PUCR8         | Port 8 pull up resistor control register | R/W        | 111в          |

| 78н to 79н   |               | (Reserved)                               |            |               |

| 7Ан          | FMCS          | Flash memory control status registger    | R/W        | 000Х00-0в     |

| 7Вн          | ILR1          | Interrupt level setting register 1       | W*         | 11111111в     |

| 7Сн          | ILR2          | Interrupt level setting register 2       | W*         | 11111111в     |

| 7Dн          | ILR3          | Interrupt level setting register 3       | W*         | 11111111в     |

| <b>7</b> Ен  | ILR4          | Interrupt level setting register 4       | W*         | 11111111в     |

| <b>7</b> Fн  |               | (Reserved)                               |            |               |

<sup>\*:</sup> Bit manipulation instruction cannot be used.

#### • Read/write access symbols

R/W: Readable and writable

R: Read-only W: Write-only

#### • Initial value symbols

0: The initial value of this bit is "0".

1: The initial value of this bit is "1".

X: The initial value of this bit is undefined.

- : Unused bit.

M: The initial value of this bit is determined by mask option.

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. Absolute Maximum Ratings

| Parameter                              | Symbol             | Rat       | ing         | Unit | Remarks                                            |

|----------------------------------------|--------------------|-----------|-------------|------|----------------------------------------------------|

| rarameter                              | Symbol             | Min       | Max         | Onic | Remarks                                            |

| Power supply voltage*1                 | Vcc<br>AVcc        | Vss - 0.3 | Vss + 4.0   | V    | AVcc must be equal to Vcc                          |

|                                        | AVR                | Vss - 0.3 | Vss + 4.0   | V    |                                                    |

| LCD power supply voltage               | V1 to V3           | Vss - 0.3 | Vcc         | V    |                                                    |

|                                        |                    | Vss - 0.3 | Vcc + 0.3   | V    | Except P40 to P47                                  |

| Input voltage *1                       | Vı                 | Vss - 0.3 | Vss + 6.0   | V    | P40 to P47 in MB89PV490 and MB89498                |

|                                        |                    | Vss - 0.3 | Vss + 5.5   | V    | P40 to P47 in MB89F499                             |

| Output voltage*1                       | Vo                 | Vss - 0.3 | Vcc + 0.3   | V    |                                                    |

| Maximum clamp current                  | <b>I</b> CLAMP     | - 2.0     | + 2.0       | mA   | *2                                                 |

| Total maximum clamp current            | $\Sigma  I_CLAMP $ | _         | 20          | mA   | *2                                                 |

| "L" level maximum output current       | loL                | _         | 15          | mA   |                                                    |

| "L" level average output current       | Iolav              |           | 4           | mA   | Average value (operating current × operating rate) |

| "L" level total maximum output current | ΣΙοι               | _         | 100         | mA   |                                                    |

| "L" level total average output current | $\Sigma$ lolav     | _         | 40          | mA   | Average value (operating current × operating rate) |

| "H" level maximum output current       | Іон                | _         | <b>– 15</b> | mA   |                                                    |

| "H" level average output current       | Іонач              | _         | - 4         | mA   | Average value (operating current× operating rate)  |

| "H" level total maximum output current | ΣІон               | _         | - 50        | mA   |                                                    |

| "H" level total average output current | ΣΙομαν             | _         | - 20        | mA   | Average value (operating current × operating rate) |

| Power consumption                      | PD                 | _         | 300         | mW   |                                                    |

| Operating temperature                  | ТА                 | - 40      | + 85        | °C   |                                                    |

| Storage temperature                    | Tstg               | - 55      | + 150       | °C   |                                                    |

<sup>\*1 :</sup> The parameter is based on AVss = Vss = 0.0 V.

- Use within recommended operating conditions.

- Use at DC voltage (current) .

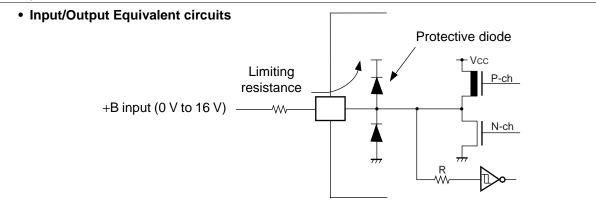

- The +B signal should always be applied with a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

<sup>\*2: •</sup> Applicable to pins: P00 to P07, P10 to P17, P20 to P27, P30 to P37, P50 to P52, P80 to P82

#### (Continued)

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller current is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on result.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits :

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### 2. Recommended Operating Conditions

(AVss = Vss = 0.0 V)

| Parameter                | Symbol      | Value |     | Unit | Remarks                            |                        |  |  |

|--------------------------|-------------|-------|-----|------|------------------------------------|------------------------|--|--|

| rarameter                | Syllibol    | Min   | Max | 0111 | ixemarks                           |                        |  |  |

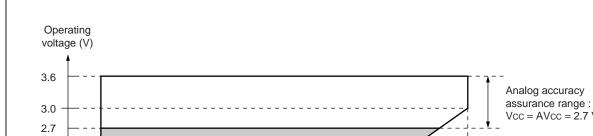

| Power supply voltage     | Vcc<br>AVcc | 2.7*  | 3.6 | ٧    | Normal operation assurance range   | MB89PV490 and MB89F499 |  |  |

|                          |             | 2.2*  | 3.6 | V    | Normal operation assurance range   | MB89498                |  |  |

|                          |             | 1.5   | 3.6 | V    | Retains the RAM state in stop mode |                        |  |  |

|                          | AVR         | 2.7   | 3.6 | V    |                                    |                        |  |  |

| LCD power supply voltage | V1 to V3    | Vss   | Vcc | V    |                                    |                        |  |  |

| Operating temperature    | TA          | -40   | +85 | °C   |                                    |                        |  |  |

<sup>\*:</sup> These values depend on the operating conditions and the analog assurance range. See Figure 1, 2 and "5. A/D Converter Electrical Characteristics".

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

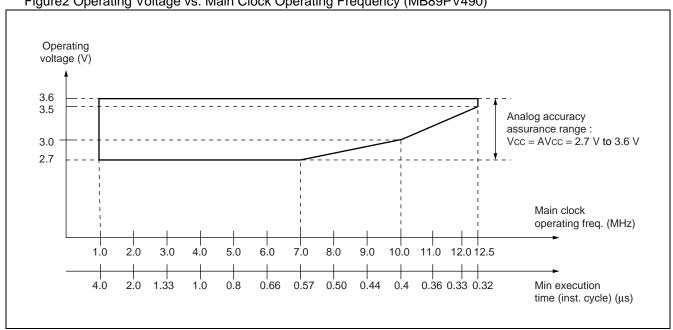

Figure 1 Operating Voltage vs. Main Clock Operating Frequency (MB89F499/498)

Vcc = AVcc = 2.7 V to 3.6 V2.2 2.0 Main clock operating freq. (MHz) 7.0 1.0 2.0 3.0 4.0 5.0 6.0 8.0 9.0 10.0 11.0 12.0 12.5 0.44 0.4 0.36 0.33 0.32 4.0 2.0 1.33 1.0 0.8 0.66 0.57 0.50 Min execution time (inst. cycle) (µs) Note: The shaded area is not assured for MB89F499

Figure 2 Operating Voltage vs. Main Clock Operating Frequency (MB89PV490)

Figure 1 and 2 indicate the operating frequency of the external oscillator at an instruction cycle of 4/Fch.

Since the operating voltage range is dependent on the instruction cycle, see figure 1 and 2 if the operating speed is switched using a gear.

#### 3. DC Characteristics

(AVcc = Vcc = 3.0 V, AVss = Vss = 0.0 V,  $T_A$  = -40 °C to +85 °C)

| Doromotor                            | Cumbal | Pin                                                                                                                                              | Condition |          | Value |           | Unit | Remarks  |

|--------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-------|-----------|------|----------|

| Parameter                            | Symbol | Pin                                                                                                                                              | Condition | Min      | Тур   | Max       | Unit | Remarks  |

| "H" level                            | Vін    | P00 to P07,<br>P10 to P17,<br>P20 to P27,<br>P30 to P37,<br>P50 to P54,<br>P60 to P67,<br>P70 to P77,<br>P80 to P84,<br>SCL, SDA,                |           | 0.7 Vcc  |       | Vcc + 0.3 | V    |          |

| input voltage                        |        | P40 to P47                                                                                                                                       | _         | 0.7 Vcc  |       | Vss + 6.0 | V    | MB89498  |

|                                      |        |                                                                                                                                                  | _         | 0.7 Vcc  |       | Vss + 5.5 | V    | MB89F499 |

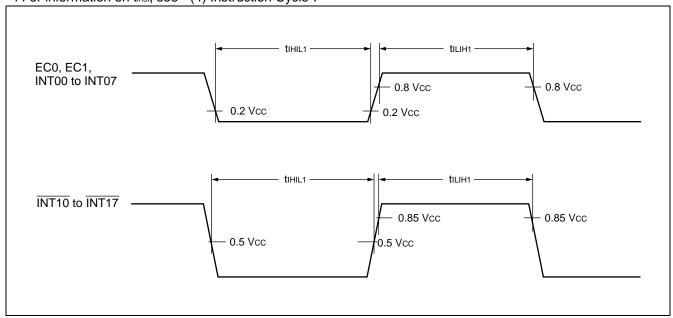

|                                      | Vihs   | RST, MOD0, EC0,<br>EC1, SCK0, SI0,<br>SCK1, SI1, RMC,<br>INT00 to INT07                                                                          | _         | 0.8 Vcc  |       | Vcc + 0.3 | V    |          |

|                                      | VIHA   | INT10 to INT17                                                                                                                                   | _         | 0.85 Vcc |       | Vcc + 0.3 | V    |          |

| "L" level input voltage              | VıL    | P00 to P07,<br>P10 to P17,<br>P20 to P27,<br>P30 to P37,<br>P40 to P47,<br>P50 to P54,<br>P60 to P67,<br>P70 to P77,<br>P80 to P84,<br>SCL, SDA, |           | Vss-0.3  |       | 0.3 Vcc   | V    |          |

|                                      | Vils   | RST, MOD0, EC0,<br>EC1, SCK0, SI0,<br>SCK1, SI1, RMC,<br>INT00 to INT07                                                                          | _         | Vss-0.3  |       | 0.2 Vcc   | V    |          |

|                                      | VILA   | INT10 to INT17                                                                                                                                   |           | Vss-0.3  |       | 0.5 Vcc   | V    |          |

| Open-drain                           |        |                                                                                                                                                  | _         | Vss-0.3  | _     | Vss + 6.0 | V    | MB89498  |

| output pin<br>application<br>voltage | VD     | P40 to P47                                                                                                                                       | _         | Vss-0.3  | —     | Vss + 5.5 | V    | MB89F499 |

(AVcc = Vcc = 3.0 V, AVss = Vss = 0.0 V,  $T_A$  = -40 °C to +85 °C)

|                                   |        |                                                                                                                                    | ,                          | •   | Value | · · · · |      |                                                |

|-----------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-------|---------|------|------------------------------------------------|

| Parameter                         | Symbol | Pin                                                                                                                                | Condition                  | Min | Тур   | Max     | Unit | Remarks                                        |

| "H" level<br>output voltage       | Vон    | P10 to P17,<br>P20 to P27,<br>P30 to P37,<br>P50 to P54,<br>P60 to P67,<br>P70 to P77,<br>P80 to P82                               | lон = −2.0 mA              | 2.2 | _     | _       | V    |                                                |

|                                   |        | P00 to P07                                                                                                                         | $I_{OH} = -4.0 \text{ mA}$ | 2.2 |       | _       | V    |                                                |

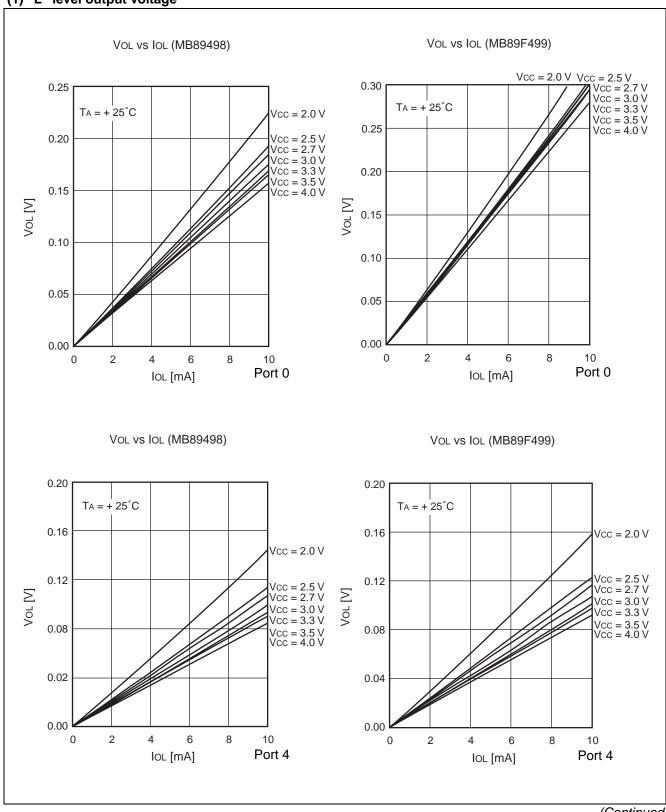

| "L" level output voltage          | Vol    | P10 to P17,<br>P20 to P27,<br>P30 to P37,<br>P50 to P54,<br>P60 to P67,<br>P70 to P77,<br>P80 to P82, RST                          | IoL = 4.0 mA               | _   | _     | 0.4     | V    |                                                |

|                                   |        | P00 to P07                                                                                                                         | IoL = 12.0 mA              |     |       | 0.4     | V    |                                                |

|                                   |        | P40 to P47                                                                                                                         | IoL = 15.0 mA              | _   |       | 0.4     | V    |                                                |

| Input leakage<br>current          | lu     | P00 to P07,<br>P10 to P17,<br>P20 to P27,<br>P30 to P37,<br>P40 to P47,<br>P50 to P54,<br>P60 to P67,<br>P70 to P77,<br>P80 to P84 | 0.45 V < Vı < Vcc          | -5  |       | +5      | μА   | Without<br>pull-up<br>resistor                 |

| Open-drain output leakage current | ILOD   | P40 to P47                                                                                                                         | 0.0 V < Vı < Vcc           | -5  | _     | +5      | μΑ   |                                                |

| Pull-down resistance              | Roown  | MOD0                                                                                                                               | Vı = Vcc                   | 25  | 50    | 100     | kΩ   | Except<br>MB89F499                             |

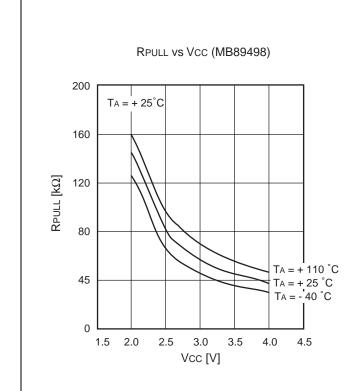

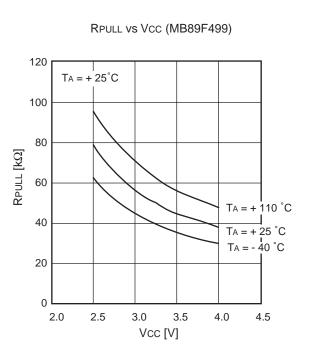

| Pull-up<br>resistance             | RPULL  | P00 to P07,<br>P10 to P17,<br>P20 to P27,<br>P30 to P37,<br>P50 to P54,<br>P60 to P67,<br>P70 to P77,<br>P80 to P82,<br>RST        | V <sub>I</sub> = 0.0 V     | 25  | 50    | 100     | kΩ   | When pull-up resistor is selected (except RST) |

| Common output impedance           | Rvсом  | COM0 to COM3                                                                                                                       | V1 to V3 = +3.0 V          | _   | _     | 2.5     | kΩ   |                                                |

(AVcc = Vcc = 3.0 V, AVss = Vss = 0.0 V, T\_A = -40  $^{\circ}C$  to +85  $^{\circ}C)$

| Devemeter                                          | Cumab al          | D:-                                         | Condition                                                                                             |     | Value |       | 11:4:4 | Remarks             |

|----------------------------------------------------|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-------|-------|--------|---------------------|

| Parameter                                          | Symbol            | Pin                                         | Condition                                                                                             | Min | Тур   | Max   | Unit   | Remarks             |

| Segment<br>output<br>impedance                     | Rvseg             | SEG0 to SEG31                               | V1 to V3 = +3.0 V                                                                                     | _   | _     | 15    | kΩ     |                     |

| LCD divided resistance                             | RLCD              | _                                           | Between Vcc and Vss                                                                                   | 300 | 500   | 750   | kΩ     |                     |

| LCD<br>controller/<br>driver<br>leakage<br>current | ILCDL             | V1 to V3,<br>COM0 to COM3,<br>SEG0 to SEG31 | _                                                                                                     | -1  | _     | +1    | μΑ     |                     |

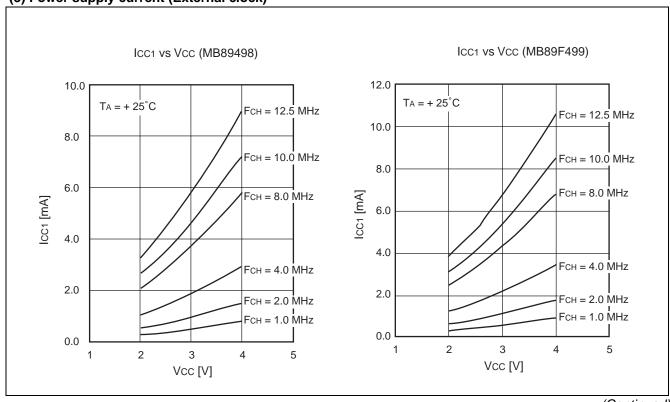

|                                                    | Icc <sub>1</sub>  |                                             | $F_{CH} = 12.5 \text{ MHz}$<br>$t_{inst} = 0.33 \mu\text{s}$                                          |     | 8.0   | 12    | mA     | MB89F499            |

|                                                    | ICC1              |                                             | Main clock run mode                                                                                   | _   | 7.0   | 12.0  | mΑ     | MB89498             |

|                                                    | Icc2              |                                             | F <sub>CH</sub> = 12.5 MHz<br>t <sub>inst</sub> = 5.33 μs<br>Main clock run mode                      |     | 1.0   | 3.0   | mA     | MB89F499<br>MB89498 |

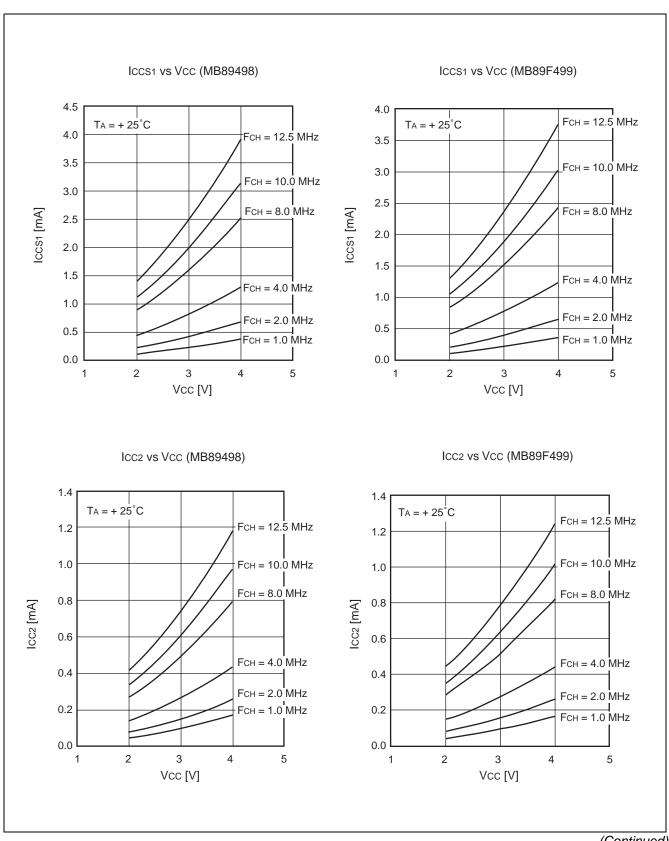

|                                                    | Iccs <sub>1</sub> |                                             | F <sub>CH</sub> = 12.5 MHz<br>t <sub>inst</sub> = 0.33 μs<br>Main clock sleep<br>mode                 | _   | 3.0   | 5.0   | mA     | MB89F499<br>MB89498 |

|                                                    | Iccs2             |                                             | F <sub>CH</sub> = 12.5 MHz<br>t <sub>inst</sub> = 5.33 μs<br>Main clock sleep<br>mode                 | _   | 0.6   | 2.0   | mA     | MB89F499<br>MB89498 |

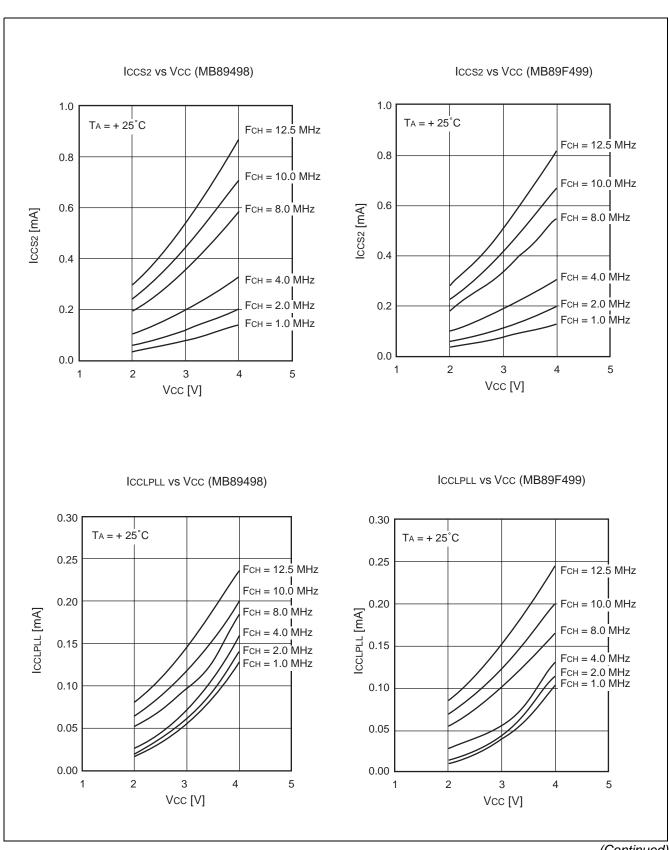

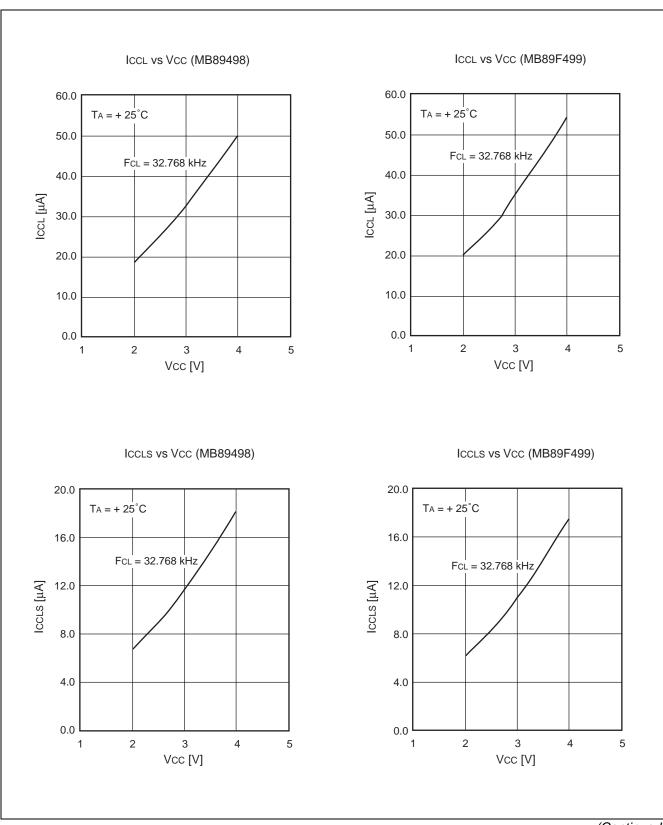

| Power supply current                               | IccL              | Vcc                                         | FcL = 32.768 kHz<br>Sub-clock mode<br>TA = +25 °C                                                     | _   | 40.0  | 60.0  | μΑ     | MB89F499<br>MB89498 |

|                                                    | ICCLPLL           |                                             | $F_{CL} = 32.768 \text{ kHz}$<br>Sub-clock mode<br>$T_A = +25 ^{\circ}\text{C}$<br>sub PLL $\times$ 4 | _   | 180.0 | 250.0 | μА     | MB89F499<br>MB89498 |

|                                                    | Iccls             |                                             | Fcl = 32.768 kHz<br>Sub-clock sleep<br>mode<br>TA = +25 °C                                            |     | 14.0  | 30.0  | μΑ     | MB89F499<br>MB89498 |

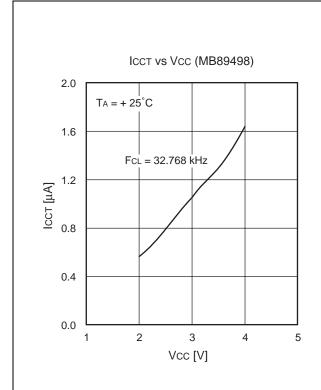

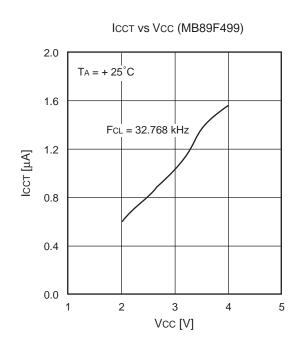

|                                                    | Ісст              |                                             | FcL = 32.768 kHz<br>Watch mode<br>Main clock stop<br>mode<br>TA = +25 °C                              | _   | 1.5   | 13.0  | μΑ     | MB89F499<br>MB89498 |

#### (Continued)

(AVcc = Vcc = 3.0 V, AVss = Vss = 0.0 V, T\_A = -40  $^{\circ}C$  to +85  $^{\circ}C)$

| Parameter            | Symbol | Pin                                    | Condition                                      |     | Value |     | Unit  | Remarks             |

|----------------------|--------|----------------------------------------|------------------------------------------------|-----|-------|-----|-------|---------------------|

| raiametei            |        |                                        | Condition                                      | Min | Тур   | Max | Oilit |                     |

|                      | Іссн   | Vcc                                    | T <sub>A</sub> = +25 °C<br>Sub-clock stop mode | _   | 0.8   | 4.0 | μА    | MB89F499<br>MB89498 |

| Power supply current | IA     | AVcc                                   | AVcc = 3.0  V,<br>$T_A = +25 ^{\circ}\text{C}$ | _   | 1.2   | 4.4 | mA    | A/D<br>converting   |

|                      | Іан    |                                        | T <sub>A</sub> = +25 °C                        | _   | 0.8   | 4.0 | μΑ    | A/D stop            |

| Input capacitance    | Cin    | Except<br>Vcc, Vss, AVcc,<br>AVss, AVR | f = 1 MHz                                      | _   | 10.0  | _   | pF    |                     |

#### 4. AC Characteristics

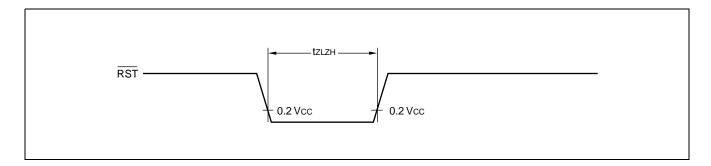

#### (1) Reset Timing

$$(AVcc = Vcc = 3.0 \text{ V}, AVss = Vss = 0.0 \text{ V}, T_A = -40 ^{\circ}C \text{ to } +85 ^{\circ}C)$$

| Parameter           | Symbol        | Symbol Condition - |          | ıe  | Unit  | Remarks |

|---------------------|---------------|--------------------|----------|-----|-------|---------|

| Farameter           | Syllibol      | Condition          | Min      | Max | Oilit | Nemarks |

| RST "L" pulse width | <b>t</b> zlzh | _                  | 48 theyl | _   | ns    |         |

Note: they is the oscillation cycle (1/Fch) to input to the X0 pin.

The MCU operation is not guaranteed when the "L" pulse width is shorter than tzlzh.

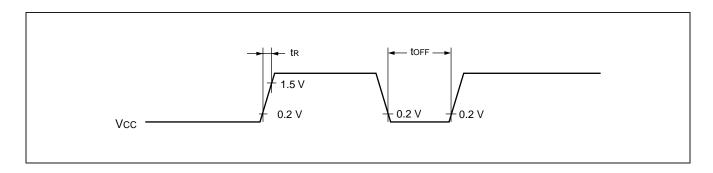

#### (2) Power-on Reset

$$(AV_{SS} = V_{SS} = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$$

| Parameter                 | Symbol     | Condition | Val | ue  | Unit  | Remarks                    |  |

|---------------------------|------------|-----------|-----|-----|-------|----------------------------|--|

| raiailletei               | Syllibol   | Condition | Min | Max | Oilit | Nemarks                    |  |

| Power supply rising time  | <b>t</b> R |           | _   | 50  | ms    |                            |  |

| Power supply cut-off time | toff       |           | 1   |     | ms    | Due to repeated operations |  |

Note: Make sure that power supply rises within the selected oscillation stabilization time.

Rapid changes in power supply voltage may cause a power-on reset. If power supply voltage needs to be varied in the course of operation, a smooth voltage rise is recommended.

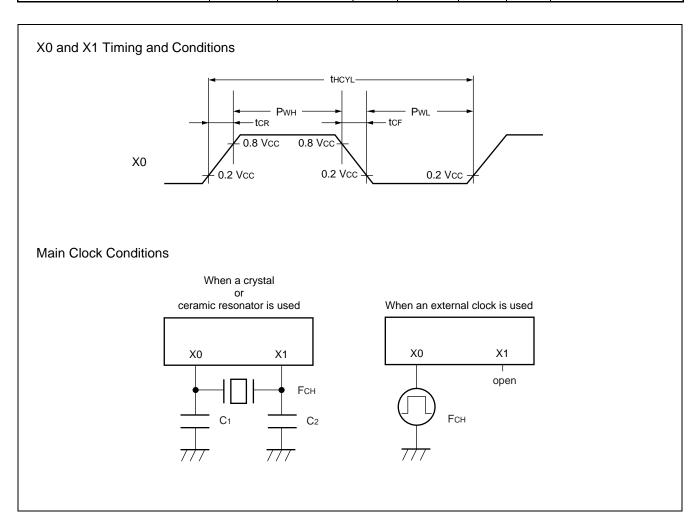

#### (3) Clock Timing

(AVss = Vss = 0.0 V,

$$T_A = -40$$

°C to +85 °C)

| Parameter                       | Symbol                               | Pin      |      | Value  |      | Unit  | Remarks        |  |

|---------------------------------|--------------------------------------|----------|------|--------|------|-------|----------------|--|

| Farameter                       | Syllibol Pill                        |          | Min  | Тур    | Max  | Offic | Remarks        |  |

| Clock frequency                 | Fсн                                  | X0, X1   | 1    | _      | 12.5 | MHz   |                |  |

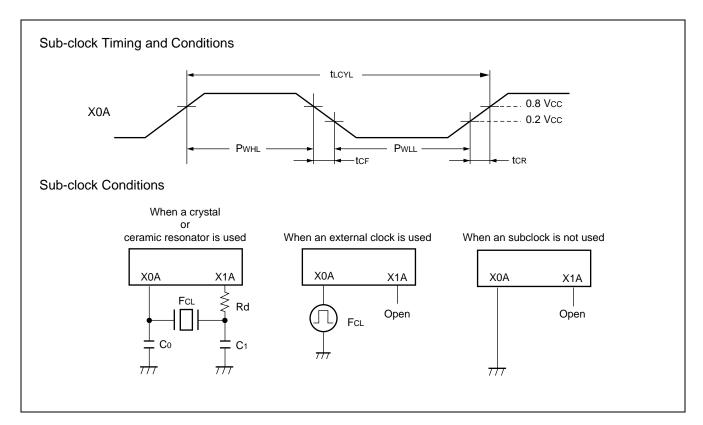

| Clock frequency                 | FcL                                  | X0A, X1A | _    | 32.768 | 75   | kHz   |                |  |

| Clock cycle time                | <b>t</b> HCYL                        | X0, X1   | 80   | _      | 1000 | ns    |                |  |

| Clock cycle time                | <b>t</b> LCYL                        | X0A, X1A | 13.3 | 30.5   | _    | μs    |                |  |

| Input clock pulse width         | P <sub>WH</sub><br>P <sub>WL</sub>   | X0       | 20   |        | _    | ns    |                |  |

| Imput clock pulse width         | P <sub>WHL</sub><br>P <sub>WLL</sub> | X0A      | _    | 15.2   | _    | μs    | External clock |  |

| Input clock rising/falling time | tcr<br>tcr                           | X0, X0A  | _    | _      | 10   | ns    |                |  |

#### (4) Instruction Cycle

| Parameter                | Symbol | Value (typical)              | Unit | Remarks                                                              |

|--------------------------|--------|------------------------------|------|----------------------------------------------------------------------|

| Instruction cycle        | tinst  | 4/Гсн, 8/Гсн, 16/Гсн, 64/Гсн | μs   | (4/FcH) $t_{inst} = 0.32~\mu s$ when operating at FcH = 12.5 MHz     |

| (minimum execution time) | tinst  | 2/FcL, 1/2FcL                | μs   | (2/FcL) $t_{inst} = 61.036 \mu s$ when operating at FcL = 32.768 kHz |

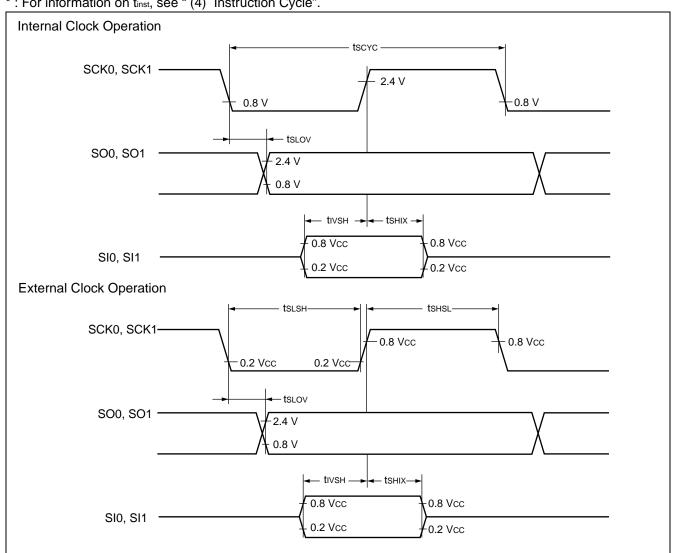

### (5) Serial I/O Timing

(AVcc = Vcc = 3.0 V, AVss = Vss = 0.0 V,  $T_A = -40$  °C to +85 °C)

| Parameter                                     | Symbol        | Pin                  | Condition            | Valu             | Unit |      |  |

|-----------------------------------------------|---------------|----------------------|----------------------|------------------|------|------|--|

| Parameter                                     | Syllibol      | FIII                 | Condition            | Min              | Max  | Oill |  |

| Serial clock cycle time                       | tscyc         | SCK0, SCK1           |                      | 2 tinst*         | _    | μs   |  |

| $SCK \downarrow \to SO$ time                  | tslov         | SCK0, SCK1, SO0, SO1 | Internal shift clock | -200             | 200  | ns   |  |

| Valid SI → SCK $\uparrow$                     | tivsh         | SI0, SI1, SCK0, SCK1 | mode                 | 1/2 tinst*       | _    | μs   |  |

| $SCK \uparrow \rightarrow valid SI hold time$ | <b>t</b> shix | SCK0, SCK1, SI0, SI1 |                      | 1/2 tinst*       | _    | μs   |  |

| Serial clock "H" pulse width                  | <b>t</b> shsl | SCK0, SCK1           |                      | 1 <b>t</b> inst* | _    | μs   |  |

| Serial clock "L" pulse width                  | <b>t</b> slsh | JONO, JON            | External             | 1 <b>t</b> inst* | _    | μs   |  |