# TLV2541, TLV2542, TLV2545 2.7 V TO 5.5 V, LOW POWER, 12-BIT, 200 KSPS, SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245 -MARCH 2000

- Maximum Throughput ... 200 KSPS

- Built-In Conversion Clock

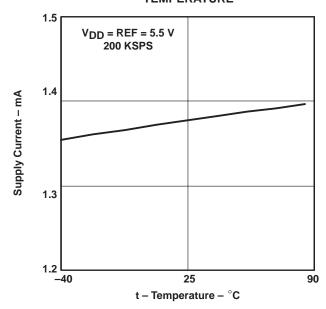

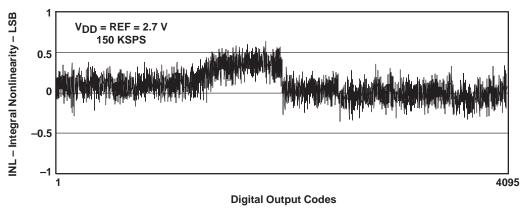

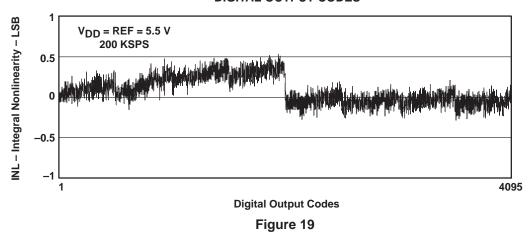

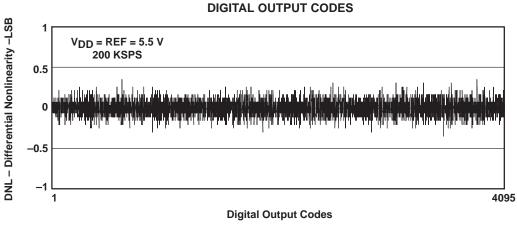

- INL/DNL: ±1 LSB Max, SINAD: 72 dB, f<sub>i</sub> = 20 kHz, SFDR: 85 dB, f<sub>i</sub> = 20 kHz

- SPI/DSP-Compatible Serial Interfaces With SCLK up to 20 MHz

- Single Supply 2.7 Vdc to 5.5 Vdc

- Rail-to-Rail Analog Input With 500 kHz BW

- Three Options Available:

- TLV2541 Single Channel Input

- TLV2542 Dual Channels With Autosweep

- TLV2545 Single Channel With Pseudo-Differential Input

- Optimized DSP Mode Requires FS Only

- Low Power With Autopower Down

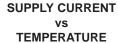

- Operating Current : 1 mA at 2.7 V, 1.5 mA at 5 V

Autopower Down: 2  $\mu\text{A}$  at 2.7 V, 5  $\mu\text{A}$  at 5 V

Small 8-Pin MSOP and SOIC Packages

| PAC                 | CAGE TOP<br>TLV2541 | VIEW                                    |                    | TL | V2542 |           |                    | Т | LV2545       |                    |

|---------------------|---------------------|-----------------------------------------|--------------------|----|-------|-----------|--------------------|---|--------------|--------------------|

| CS [1               | (J)                 | 8] SDO                                  | CS/FS              | 1  | 8     | SDO       | CS/FS [            | 1 | $\leftarrow$ | B] SDO             |

| V <sub>REF</sub> [2 |                     | 7 🛮 FS                                  | V <sub>REF</sub> [ | 2  | 7     | ] SCLK    | V <sub>REF</sub> [ | 2 |              | 7 SCLK             |

| GND [3              |                     | 6 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | GND [              | 3  | 6     | $]V_{DD}$ | GND [              | 3 | (            | 6 DV <sub>DD</sub> |

| AIN [ 4             |                     | 5 SCLK                                  | AIN0               | 4  | 5     | ] AIN1    | AIN(+) [           | 4 |              | 5 AIN(-)           |

#### description

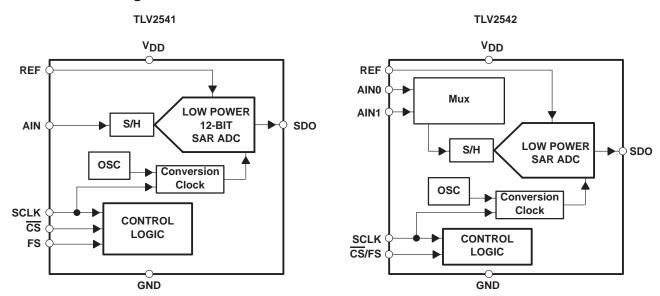

The TLV2541/2542/2545 are a family of high performance, 12-bit, low power, miniature 3.6  $\mu$ s, CMOS analog-to-digital converters (ADC). The TLV254x family operates from a single 2.7 V to 5.5 V. Devices are available with single, dual, or single pseudo-differential inputs. The TLV2541 has a 3-state output chip select ( $\overline{CS}$ ), serial output clock (SCLK), and serial data output (SDO) that provides a direct 3-wire interface to the serial port of most popular host microprocessors (SPI interface). When interfaced with a DSP, a frame sync signal (FS) is used to indicate the start of a serial data frame. The TLV2542/45 have a shared  $\overline{CS}$ /FS terminal.

TLV2541/2/5 are designed to operate with very low power consumption. The power saving feature is further enhanced with an autopower-down mode. This product family features a high-speed serial link to modern host processors with SCLK up to 20 MHz. TLV254x family uses the built in oscillator as conversion clock, providing a 3.6 μs conversion time.

#### **AVAILABLE OPTIONS**

|               | PACKAGED DEVICES |               |  |  |  |

|---------------|------------------|---------------|--|--|--|

| TA            | 8-MSOP<br>(DGK)  | 8-SOIC<br>(D) |  |  |  |

|               | TLV2541CDGK      |               |  |  |  |

| 0°C to 70°C   | TLV2542CDGK      |               |  |  |  |

|               | TLV2545CDGK      |               |  |  |  |

|               | TLV2541IDGK      | TLV2541ID     |  |  |  |

| -40°C to 85°C | TLV2542IDGK      | TLV2542ID     |  |  |  |

|               | TLV2545IDGK      | TLV2545ID     |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# functional block diagram

#### **Terminal Functions**

#### **TLV2541**

| TERMINA  | ٩L  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                     |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                     |

| AIN      | 4   | I   | Analog input channel                                                                                                                                                                                                                                                                                            |

| CS       | 1   | Ι   | Chip select. A high-to-low transition on the $\overline{\text{CS}}$ input removes SDO from 3-state within a maximum setup time. $\overline{\text{CS}}$ can be used as the FS pin when a dedicated serial port is used. If TLV2541 is attached to a dedicated DSP serial port, this terminal can be grounded.    |

| FS       | 7   | I   | DSP frame sync input. Indication of the start of a serial data frame. Tie this terminal to V <sub>DD</sub> if not used.                                                                                                                                                                                         |

| GND      | 3   | I   | Ground return for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                                                             |

| SCLK     | 5   | I   | Output serial clock. This terminal receives the serial SCLK from the host processor.                                                                                                                                                                                                                            |

| SDO      | 8   | 0   | The 3-state serial output for the A/D conversion result. SDO is kept in the high-impedance state until CS falling edge. The output format is MSB first.                                                                                                                                                         |

|          |     |     | When FS is not used (FS = 1 at the falling edge of $\overline{\text{CS}}$ ): The MSB is presented to the SDO pin after $\overline{\text{CS}}$ falling edge and output data is valid on the falling edge of SCLK.                                                                                                |

|          |     |     | When FS is used (FS = $0$ at the falling edge of $\overline{CS}$ ): The MSB is presented to the SDO pin after the falling edge of FS or the falling edge of $\overline{CS}$ (whichever happens first). Output data is valid on the falling edge of SCLK. (This is typically used with an active FS from a DSP). |

| $V_{DD}$ | 6   | I   | Positive supply voltage                                                                                                                                                                                                                                                                                         |

| VREF     | 2   | Ī   | External reference input                                                                                                                                                                                                                                                                                        |

#### TLV2542/45

| TERMINA          | L   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                               |

| AIN0 /AIN(+)     | 4   | I   | Analog input channel 0. (positive input for TLV2545)                                                                                                                                                                                                                                                                                                                                                      |

| AIN1/AIN (-)     | 5   | I   | Analog input channel 1 (inverted input for TLV2545)                                                                                                                                                                                                                                                                                                                                                       |

| CS/FS            | 1   | I   | Chip select/frame sync. A high-to-low transition on the $\overline{\text{CS}}/\text{FS}$ removes SDO from 3-state within a maximum delay time.                                                                                                                                                                                                                                                            |

| GND              | 3   | I   | Ground return for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                                                                                                                                                       |

| SCLK             | 7   | I   | Output serial clock. This terminal receives the serial SCLK from the host processor.                                                                                                                                                                                                                                                                                                                      |

| SDO              | 8   | 0   | The 3-state serial output for the A/D conversion result. SDO is kept in the high-impedance state when $\overline{\text{CS}}/\text{FS}$ is high and presents output data after the $\overline{\text{CS}}/\text{FS}$ falling edge until the LSB is presented. The output format is MSB first. SDO returns to the Hi-Z state after the 16 <sup>th</sup> SCLK. Output data is valid on the falling SCLK edge. |

| $V_{DD}$         | 6   | I   | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REF</sub> | 2   | I   | External reference input                                                                                                                                                                                                                                                                                                                                                                                  |

# detailed description

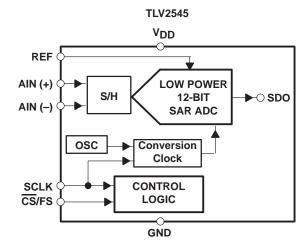

The TLV2541/2/5 are successive approximation (SAR) ADCs utilizing a charge redistribution DAC. Figure 1 shows a simplified version of the ADC.

The sampling capacitor acquires the signal on AIN during the sampling period. When the conversion process starts, the SAR control logic and charge redistribution DAC are used to add and subtract fixed amounts of charge from the sampling capacitor to bring the comparator into a balanced condition. When the comparator is balanced, the conversion is complete and the ADC output code is generated.

### detailed description (continued)

SLAS245 -MARCH 2000

Figure 1. Simplified SAR Circuit

#### serial interface

| OUTPUT DATA FORMAT           |            |  |  |  |

|------------------------------|------------|--|--|--|

| MSB                          | LSB        |  |  |  |

| D15-D4                       | D3-D0      |  |  |  |

| Conversion result (OD11-OD0) | Don't care |  |  |  |

The output data format is binary (unipolar straight binary).

#### binary

Zero scale code = 000h, Vcode = GND Full scale code = FFFh, Vcode = VREFP – 1 LSB

#### pseudo-differential inputs

The TLV2545 operates in pseudo-differential mode. The inverted input is available on pin 5. It can have a maximum input ripple of  $\pm 0.2$  V. This is normally used for ground noise rejection.

#### control and timing

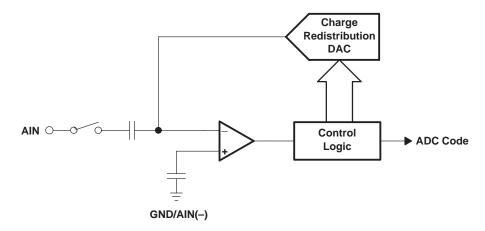

### start of the cycle

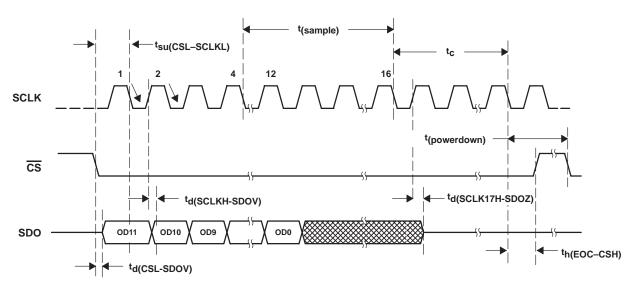

#### **TLV2541**

- When FS is not used (FS = 1 at the falling edge of \(\overline{CS}\)), the falling edge of \(\overline{CS}\) is the start of the cycle. Output data changes on the rising edge of SCLK. This is typically used for a microcontroller with SPI interface, although it can also be used for a DSP. The microcontroller SPI interface should be programmed for CPOL=0 (serial clock referenced to ground) and CPHA=1 (data is valid on the falling edge of serial clock).

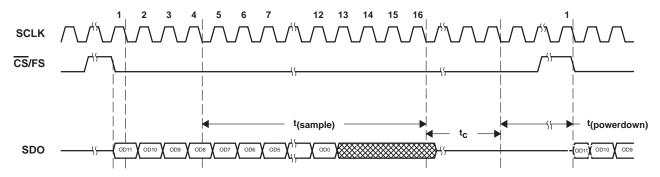

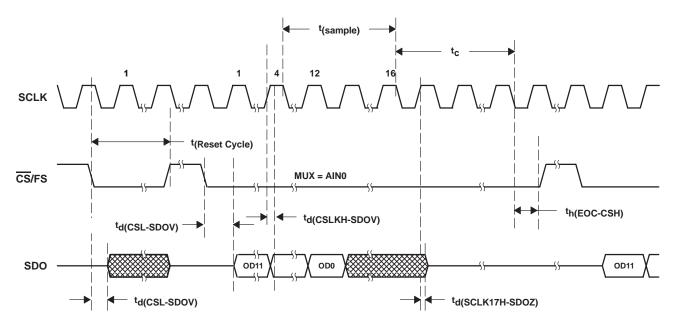

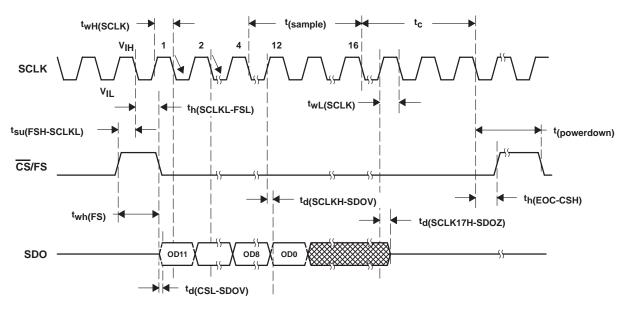

# TLV2542/5

The  $\overline{\text{CS}}$  and FS inputs are accessed via the same pin (pin 1) on the TLV2542 and TLV2545. The cycle is started by the falling edge transition provided by either a  $\overline{\text{CS}}$  (interfacing with SPI microcontroller) signal or FS (interfacing with TMS320 DSP) signal. Timing for the TLV2545 is much like the TLV2541, with the exception of the  $\overline{\text{CS}}/\text{FS}$  line.

# TLV2541, TLV2542, TLV2545 2.7 V TO 5.5 V, LOW POWER, 12-BIT, 200 KSPS, SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245 -MARCH 2000

### detailed description (continued)

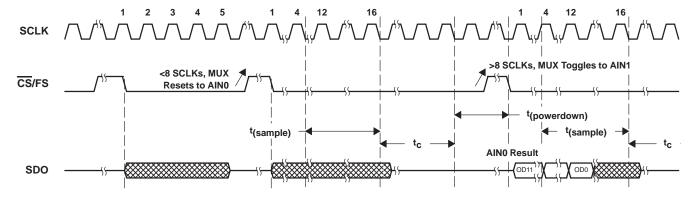

#### TLV2542 channel MUX reset cycle

The TLV2542 uses  $\overline{CS}/FS$  to reset the AIN multiplexer. A short active  $\overline{CS}/FS$  cycle (4 to 7 SCLKs) resets the MUX to AINO. If the  $\overline{CS}/FS$  cycle is sufficient to complete the conversion (16 SCLKs plus maximum conversion time), the MUX toggles to the next channel (see Figure 4 for timing).

#### sampling

The converter sample time is 12 SCLKs in duration, beginning on the 5<sup>th</sup> SCLK received after the converter has received an active  $\overline{\text{CS}}$  or FS signal ( $\overline{\text{CS}}$ /FS for the TLV2542/5).

#### conversion

The TLV2541 completes conversion in the following manner. The conversion is started after the 16th SCLK edge. The conversion takes  $3.5 \,\mu s$  plus  $0.1 \,\mu s$  overhead. Enough time (for conversion) should be allowed before a rising  $\overline{CS}/FS$  edge so that no conversion is terminated prematurely.

TLV2542 input channel selection is toggled on each rising  $\overline{\text{CS}}$  /FS edge. The MUX channel can be reset to AIN0 via  $\overline{\text{CS}}$  /FS as described in the earlier section and in Figure 5. The input is sampled for 12 SCLKs, converted, and the result is presented on SDO during the next cycle. Care should also be taken to allow enough time between samples to avoid prematurely terminating the conversion, which occurs on a rising  $\overline{\text{CS}}$  /FS transition if the conversion is not complete.

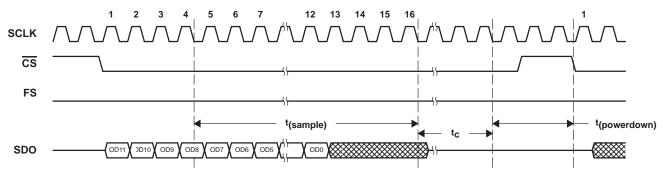

# timing diagrams/conversion cycles

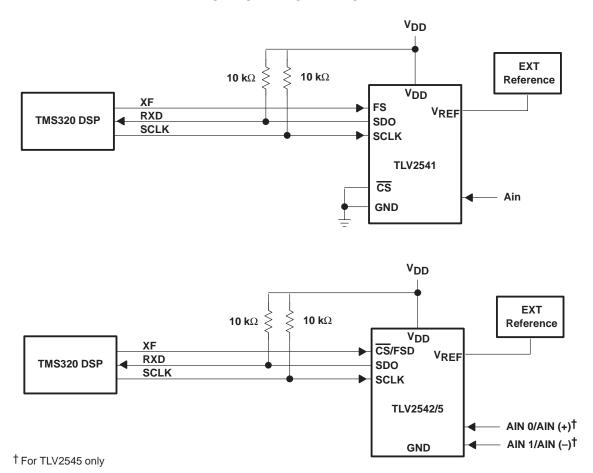

# **DSP Interface**

Figure 2. TLV2541 DSP Mode/FS Active

# $\mu$ P Interface

Figure 3. TLV2541 Microcontroller Mode/FS (SPI, CPOL = 0, CPHA = 1)

Figure 4. TLV2542 Timing

## timing diagrams/conversion cycles (continued)

Figure 5. TLV2545 Timing

# use CS as FS input

When interfacing the TLV2541 with the TMS320 DSP, the FSR signal from the DSP may be connected to the  $\overline{\text{CS}}$  input if this is the only device on the serial port. This will save one output terminal from the DSP. (Output data changes on the falling edge of SCLK. Default for TLV2542 and TLV2545).

# SCLK and conversion speed

The minimum onboard oscillator frequency for the TLV2541/2/5 is 4 MHz, and it takes 14 conversion clocks to complete the conversion. This leads to a 3.5  $\mu$ s conversion time plus 0.1  $\mu$ s overhead. These devices can operate with an SCLK up to 20 MHz for the supply voltage range specified. The total conversion time is 14× (1/f<sub>OSC</sub>). For a 20 MHz SCLK, the minimum total cycle time is given by: 14× (1/4M) +16× (1/20M)+ 0.1  $\mu$ s = 4.4  $\mu$ s for the TLV254x devices. This is the minimum cycle time for an active  $\overline{CS}$  or  $\overline{CS}$ /FS signal. If violated, the conversion will terminate, invalidating the next data output cycle.

#### reference voltage

An external reference is applied via VREF. The voltage level applied to this pin establishes the upper limit of the analog inputs to produce a full-scale reading. The value of  $V_{REF}$  and the analog input should not exceed the positive supply or be less than GND, consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than  $V_{REF}$  and at zero when the input signal is equal to or lower than GND.

#### powerdown and powerup initialization

Autopower down is built in to the devices in order to reduce power consumption. The wake-up time is fast enough to provide power down between each cycle. The power-down state is initiated at the end of conversion and wakes up upon a falling edge on  $\overline{CS}$  or FS.

# TLV2541, TLV2542, TLV2545 2.7 V TO 5.5 V, LOW POWER, 12-BIT, 200 KSPS, SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245 -MARCH 2000

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)

| Supply voltage range, GND to V <sub>DD</sub>                 |                                  |

|--------------------------------------------------------------|----------------------------------|

| Analog input voltage range                                   | 0.3 V to V <sub>DD</sub> + 0.3 V |

| Reference input voltage                                      | V <sub>DD</sub> + 0.3 V          |

| Digital input voltage range                                  |                                  |

| Operating virtual junction temperature range, T <sub>J</sub> | 40°C to 150°C                    |

| Operating free-air temperature range, T <sub>A</sub> : C     | 0°C to 70°C                      |

| L                                                            | –40°C to 85°C                    |

| Storage temperature range, T <sub>stq</sub>                  | 65°C to 150°C                    |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

|                                                                                                                               |                                                              | MIN      | NOM  | MAX             | UNIT  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|------|-----------------|-------|

| Supply voltage, V <sub>DD</sub>                                                                                               |                                                              | 2.7      | 3.3  | 5.5             | V     |

| Positive external reference voltage input, VREFP (see Note 1)                                                                 |                                                              | 2        |      | V <sub>DD</sub> | V     |

| Analog input voltage (see Note 1)                                                                                             |                                                              | 0        |      | $V_{DD}$        | V     |

| High level control input voltage, VIH                                                                                         |                                                              | 2.1      |      |                 | V     |

| Low-level control input voltage, V <sub>IL</sub>                                                                              |                                                              |          |      | 0.6             | V     |

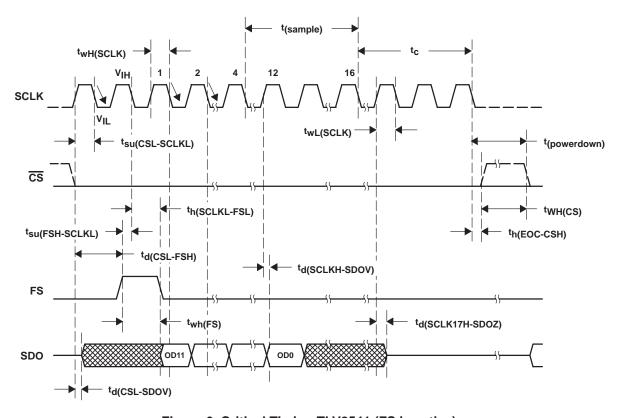

| Setup time, CS falling edge (2541) or CS/FS falling edge (2542/45) before first SCLK falling edge, t <sub>SU(CSL-SCLKL)</sub> | V <sub>DD</sub> = REF = 5 V<br>V <sub>DD</sub> = REF = 2.7 V | 40<br>70 |      |                 | ns    |

| Hold time, CS rising edge after SCLK falling edge, th(SCLKL-CSH)                                                              |                                                              | 5        |      |                 | ns    |

| Delay time, delay from CS falling edge to FS rising edge (td(CSL-F.                                                           | SH)                                                          | 0.5      |      | 7               | SCLKs |

| Setup time, FS rising edge before SCLK falling edge, t <sub>SU(FSH-SCL</sub>                                                  | KL)                                                          | 0.35     |      |                 | SCLKs |

| Hold time, FS hold high after SCLK falling edge, th(SCLKL-FSL)                                                                |                                                              |          | 0.65 |                 | SCLKs |

| Pulse width CS high time, t <sub>WH(CS)</sub>                                                                                 |                                                              | 100      |      |                 | ns    |

| Pulse width FS high time, t <sub>WH(FS)</sub>                                                                                 |                                                              | 0.75     |      |                 | SCLKs |

| SCLK cycle time, $V_{DD} = 3.6-2.7 \text{ V}$ , $t_{C(SCLK)}$                                                                 |                                                              | 67       |      | 10000           | ns    |

| SCLK cycle time, V <sub>DD</sub> = 5.5–4.5 V, t <sub>C</sub> (SCLK)                                                           |                                                              | 50       |      | 10000           | ns    |

| Pulse width low time, twL(SCLK)                                                                                               |                                                              | 0.4      |      | 0.6             | SCLK  |

| Pulse width high time, t <sub>wH</sub> (SCLK)                                                                                 |                                                              | 0.4      |      | 0.6             | SCLK  |

| Hold time, hold from end of conversion to CS high, $t_{h(EOC\text{-CSH})}$ (Econversion time, $t_{c}$ )                       | EOC is internal, indicates end of                            | 0.1      |      |                 | μs    |

| Active CS/FS cycle time to reset internal MUX to AIN0, reset cycle                                                            | TLV2542 only                                                 | 4        |      | 7               | SCLKs |

| Operating free-air temperature, T <sub>A</sub>                                                                                | TLV2541/2/5C                                                 | 0        |      | 70              | °C    |

| operating need an temperature, 14                                                                                             | TLV2541/2/5I                                                 | -40      |      | 85              | O     |

- NOTES: 1. Analog input voltages greater than that applied to VREF convert as all ones (11111111111), while input voltages less than that applied to GND convert as all zeros(000000000000).

- 2. This is the time required for the clock input signal to fall from VIH max or to rise from VIL max to VIHmin. In the vicinity of normal room temperature, the devices function with input clock transition time as slow as 1 µs for remote data-acquisition applications where the sensor and A/D converter are placed several feet away from the controlling microprocessor.

# TLV2541, TLV2542, TLV2545 2.7 V TO 5.5 V, LOW POWER, 12-BIT, 200 KSPS, SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245 -MARCH 2000

# electrical characteristics over recommended operating free-air temperature range, $V_{DD} = V_{REF} = 2.7 \text{ V}$ to 5.5 V, SCLK frequency = 20 MHz at 5 V, 15 MHz at 3 V (unless otherwise noted)

|                       | PARAMETER                                           | TEST CON                                                                                                     | DITIONS                         | MIN                  | TYP    | MAX  | UNIT |

|-----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|--------|------|------|

|                       |                                                     | $V_{DD} = 5.5 \text{ V}, I_{OH} = -0.2 \text{ I}$                                                            | mA at 30 pF load                | 2.4                  |        |      |      |

| VOH                   | High-level output voltage                           | V <sub>DD</sub> = 2.7 V, I <sub>OH</sub> = -20 μ                                                             | A at 30 pF load                 | V <sub>DD</sub> -0.2 |        |      | V    |

| .,                    |                                                     | $V_{DD} = 5.5 \text{ V}, I_{OL} = 0.8 \text{ m}$                                                             | A at 30 pF load                 |                      |        | 0.4  | .,   |

| V <sub>OL</sub>       | Low-level output voltage                            | V <sub>DD</sub> = 2.7 V, I <sub>OL</sub> = 20 μA                                                             | at 30 pF load                   |                      |        | 0.1  | V    |

|                       | Off-state output current                            | $V_O = V_{DD}$                                                                                               | <u></u>                         | 1 2.5                |        |      |      |

| loz                   | (high-impedance-state)                              | V <sub>O</sub> = 0                                                                                           | CS = V <sub>DD</sub>            |                      | -1     | -2.5 | μΑ   |

| I <sub>IH</sub>       | High-level input current                            | $V_I = V_{DD}$                                                                                               | •                               |                      | 0.005  | 2.5  | μΑ   |

| I <sub>IL</sub>       | Low-level input current                             | V <sub>I</sub> = 0 V                                                                                         |                                 |                      | -0.005 | 2.5  | μΑ   |

|                       |                                                     |                                                                                                              | V <sub>DD</sub> = 4.5 V ~ 5.5 V |                      | 1.3    | 1.5  |      |

| ICC                   | Operating supply current                            | CS at 0 V,                                                                                                   | V <sub>DD</sub> = 2.7 V ~ 3.3 V |                      | 0.85   | 0.95 | mA   |

|                       | Autopower-down current (0.5 μs inactive)            | For all digital inputs, $0 \le V_1 \le 0.3 \text{ V or } V_1 \ge V_{DD}$ SCLK = 0, $V_{DD}$ = 4.5 V to       |                                 |                      |        | 5    | μΑ   |

|                       |                                                     | $V_{DD} = 2.7 \text{ V to } 3.3 \text{ V},  \text{E}$                                                        | xt ref                          |                      |        | 2    |      |

| ICC(AUTOPWDN)         | Autopower-down current (5 μs inactive)              | For all digital inputs,<br>$0 \le V_I \le 0.3 \text{ V or } V_I \ge V_{DD}$<br>SCLK = 0, $V_{DD}$ = 4.5 V to |                                 |                      |        | 1    | μΑ   |

|                       |                                                     | V <sub>DD</sub> = 2.7 V to 3.3 V                                                                             |                                 |                      |        | 1    |      |

|                       | Selected analog input channel leakage               | Selected channel at V <sub>DD</sub>                                                                          |                                 |                      | 1      | μΑ   |      |

|                       | current                                             | Selected channel at 0 V                                                                                      |                                 |                      |        |      | -1   |

|                       |                                                     | Analog inputs                                                                                                |                                 | 20                   | 45     | 50   |      |

| Ci                    | Input capacitance                                   | Control Inputs                                                                                               |                                 |                      | 5      | 25   | pF   |

|                       |                                                     | V <sub>DD</sub> = 5.5 V                                                                                      |                                 |                      |        | 500  |      |

|                       | Input on resistance                                 | V <sub>DD</sub> = 2.7 V                                                                                      |                                 |                      |        | 600  | Ω    |

|                       | Delay time, delay from CS falling edge to           | V <sub>DD</sub> = REF = 5.5 V, 30 pl                                                                         | F load                          |                      |        | 40   |      |

|                       | SDO valid, t <sub>d(CSL-SDOV)</sub>                 | V <sub>DD</sub> = REF = 2.7 V, 30 pl                                                                         | Fload                           |                      |        | 70   | ns   |

|                       | Delay time, delay from FS falling edge to           | V <sub>DD</sub> = REF = 5.5 V, 30 pl                                                                         | Fload                           |                      |        | 1    |      |

|                       | SDO valid, t <sub>d</sub> (FSL-SDOV)                | V <sub>DD</sub> = REF = 2.7 V, 30 pl                                                                         | Fload                           |                      |        | 1    | ns   |

|                       | Delay time, delay from SCLK rising edge             | V <sub>DD</sub> = REF = 5.5 V, 30 pl                                                                         | Fload                           |                      |        | 11   |      |

|                       | to SDO valid, t <sub>d</sub> (SCLKH-SDOV)           | V <sub>DD</sub> = REF = 2.7 V, 30 pl                                                                         | Fload                           |                      |        | 21   | ns   |

|                       | Delay time, delay from 17 <sup>th</sup> SCLK rising | V <sub>DD</sub> = REF = 5.5 V, 30 pl                                                                         | Fload                           |                      |        | 30   |      |

|                       | edge to SDO 3-state, t <sub>d</sub> (SCLK17H-SDOZ)  | V <sub>DD</sub> = REF = 2.7 V, 30 pl                                                                         | Fload                           |                      |        | 60   | ns   |

| t <sub>C</sub>        | Conversion time                                     | Conversion clock = intern                                                                                    | al oscillator                   | 2.1                  | 2.6    | 3.5  | μs   |

| <sup>t</sup> (sample) | Sampling time                                       | See Note 3                                                                                                   |                                 | 300                  |        |      | ns   |

|                       | Action time                                         | I <sub>CC</sub> start to decrease                                                                            |                                 |                      | 0.5    |      | SCLK |

| Autopower down        | Wakeup time                                         | ICC down to MIN [ICC(AL                                                                                      |                                 | 1                    | 2      | ms   |      |

|                       | Autopower down                                      |                                                                                                              |                                 |                      | 0.5    |      | SCLK |

<sup>†</sup> All typical values are at  $V_{DD} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

NOTE 3: Minimal  $t_{(sample)}$  is given by  $0.9 \times 50$  pF  $\times$  (RS + 0.6 kW), where RS is the source output impedance.

# TLV2541, TLV2542, TLV2545 2.7 V TO 5.5 V, LOW POWER, 12-BIT, 200 KSPS, SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245 -MARCH 2000

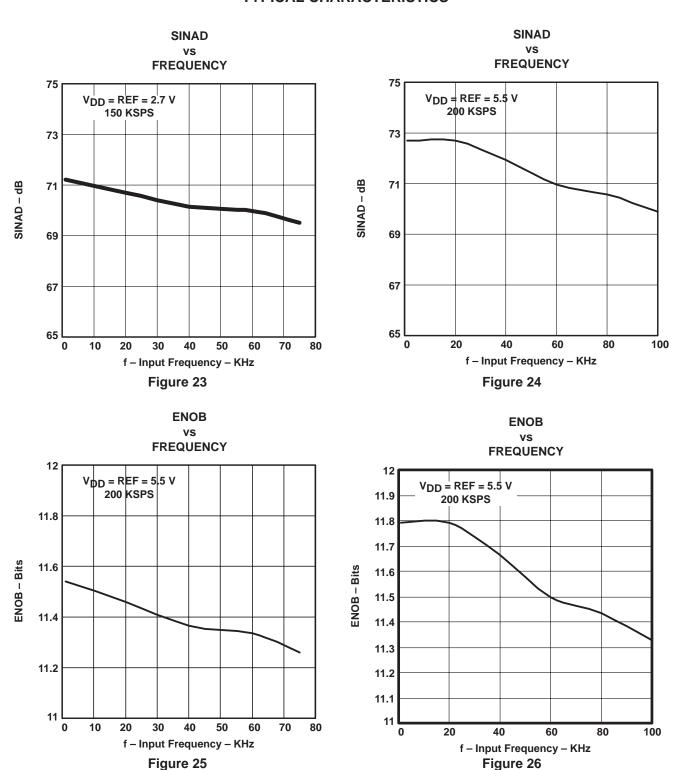

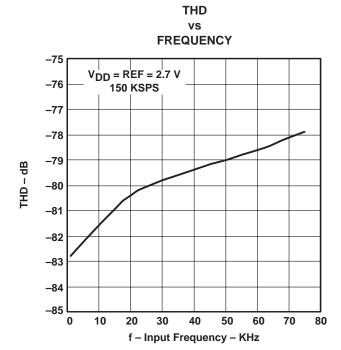

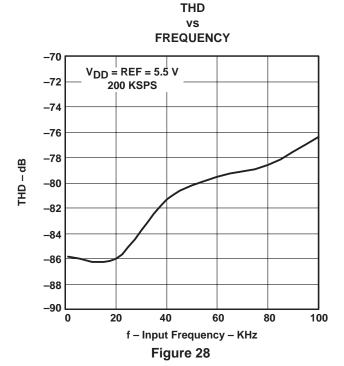

# ac specifications (f<sub>i</sub> = 20 kHz)

|        | PARAMETER                         | TEST CONDITIONS                                      | MIN | TYP  | MAX | UNIT |

|--------|-----------------------------------|------------------------------------------------------|-----|------|-----|------|

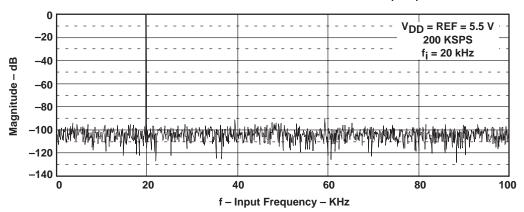

| SINAD  | Signal-to-noise ratio +distortion | 200 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 5.5 V | 70  | 72   |     | dB   |

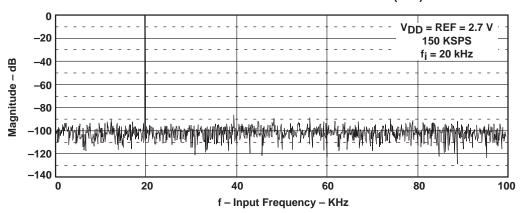

| SINAD  | Signal-to-noise ratio +distortion | 150 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 2.7 V | 68  | 71   |     | uБ   |

| THD    | Total harmonic distortion         | 200 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 5.5 V |     | -84  | -80 | dB   |

| וחט    | Total Harmonic distortion         | 150 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 2.7 V |     | -84  | -80 | uБ   |

| ENOB   | Effective number of bits          | 200 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 5.5 V |     | 11.8 |     | Bits |

| ENOB   | Effective number of bits          | 150 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 2.7 V |     | 11.6 |     | DIIS |

| SFDR   | Spurious free dynamic range       | 200 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 5.5 V |     | -84  | -80 | dB   |

| SFDK   | Spurious nee dynamic range        | 150 KSPS, V <sub>DD</sub> = V <sub>REF</sub> = 2.7 V |     | -84  | -80 | uБ   |

| Analog | Input                             |                                                      |     |      |     |      |

|        | Full power bandwidth, –3 dB       |                                                      |     | 1    |     | MHz  |

|        | Full-power bandwidth, –1 dB       |                                                      |     | 500  |     | kHz  |

# external reference specifications

|      | PARAMETER TEST CONDITIONS   |                                            |                                            | MIN | TYP | MAX      | UNIT |

|------|-----------------------------|--------------------------------------------|--------------------------------------------|-----|-----|----------|------|

|      | Reference input voltage     | V <sub>DD</sub> = =2.7 V ~ 5.5 V           |                                            |     |     | $V_{DD}$ | V    |

|      |                             | V <sub>DD</sub> = 5.5 V                    | CS = 1, SCLK = 0                           | 100 |     |          | МΩ   |

|      | Reference input impedance   | VDD = 5.5 V                                | CS = 0, SCLK = 20 MHz                      | 20  | 25  |          | kΩ   |

|      |                             | V <sub>DD</sub> = 2.7 V                    | CS = 1, SCLK = 0                           | 100 |     |          | МΩ   |

|      |                             | V <sub>DD</sub> = 2.7 V                    | $\overline{\text{CS}} = 0$ , SCLK = 20 MHz | 20  | 25  |          | kΩ   |

|      | Potoronoo gurront           | $V_{DD} = V_{REF} = 5.5 V,$                | CS = 0, SCLK = 20 MHz                      |     | 100 | 400      |      |

|      | Reference current           | V <sub>DD</sub> = V <sub>REF</sub> =2.7 V, | CS = 0, SCLK = 20 MHz                      |     | 50  | 200      | μΑ   |

|      |                             | V <sub>DD</sub> = V <sub>REF</sub> = 5.5 V | CS = 1, SCLK = 0                           | 5   |     | 15       | pF   |

|      | Defendant involved          |                                            | CS = 0, SCLK = 20 MHz                      | 20  | 45  | 50       |      |

|      | Reference input capacitance | ., ., ., ., .,                             | CS = 1, SCLK = 0                           | 5   |     | 15       |      |

|      |                             | V <sub>DD</sub> = V <sub>REF</sub> =2.7 V  | CS = 0, SCLK = 20 MHz                      | 20  | 45  | 50       |      |

| VREF | Reference voltage           | $V_{DD} = =2.7 V - 5.5 V$                  |                                            |     |     | $V_{DD}$ | V    |

# dc specification, $V_{DD} = V_{REF} = 2.7 \text{ V}$ to 5.5 V, SCLK frequency = 20 MHz at 5 V, 15 MHz at 3 V (unless otherwise noted)

|     | PARAMETER                             | TEST C     | ONDITIONS  | MIN | NOM  | MAX  | UNIT |

|-----|---------------------------------------|------------|------------|-----|------|------|------|

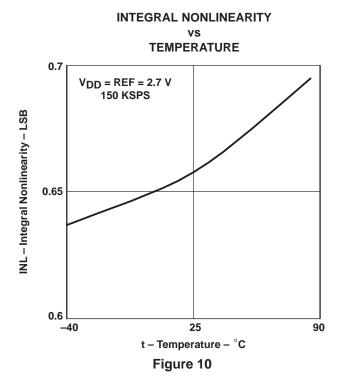

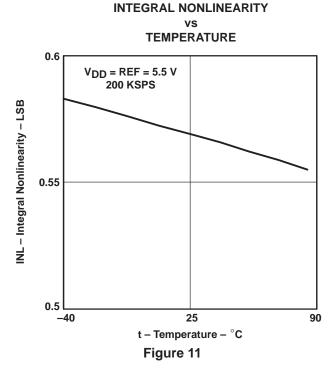

| INL | Integral linearity error (see Note 5) |            |            |     | ±0.6 | ±1   | LSB  |

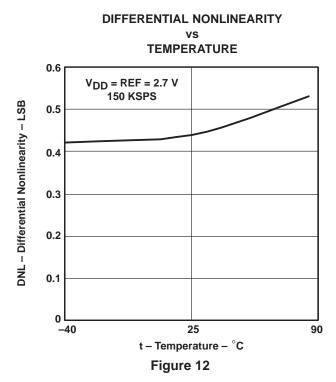

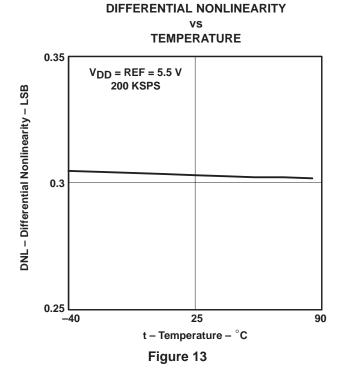

| DNL | Differential linearity error          | See Note 4 |            |     | ±0.5 | ±1   | LSB  |

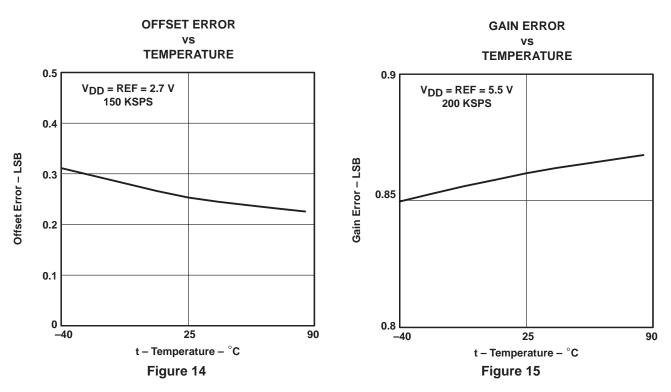

| F   | Officet owner (see Note C)            | Coo Note 4 | TLV2541/42 |     |      | ±1.5 | LSB  |

| EO  | Offset error (see Note 6)             | See Note 4 | TLV2545    |     |      | ±2.5 | LOD  |

|     | Coin array (and Note 6)               | Coo Note 4 | TLV2541/42 |     |      | ±2   | LSB  |

| EG  | Gain error (see Note 6)               | See Note 4 | TLV2545    |     |      | ±5   | LOD  |

| E.  | Total unadjusted array (and Note 7)   | See Note 4 | TLV2541/42 |     |      | ±2   | LSB  |

| Et  | Total unadjusted error (see Note 7)   | See Note 4 | TLV2545    |     |      | ±5   | LOD  |

NOTES: 4. Analog input voltages greater than that applied to REFP convert as all ones (11111111111), while input voltages less than that applied to REFM convert as all zeros (0000000000).

- 5. Linear error is the maximum deviation from the best straight line through the A/D transfer characteristics.

- 6. Zero error is the difference between 000000000000 and the converted output for zero input voltage: full-scale error is the difference between 111111111111 and the converted output for full-scale input voltage.

- 7. Total unadjusted error comprises linearity, zero, and full-scale errors.

#### PARAMETER MEASUREMENT INFORMATION

Figure 6. Critical Timing TLV2541 (FS is active)

Figure 7. Critical Timing TLV2541 (FS = 1)

#### PARAMETER MEASUREMENT INFORMATION

Figure 8. Critical Timing TLV2542 Reset Cycle

Figure 9. Critical Timing TLV2545 Power-Down Cycle

# TYPICAL CHARACTERISTICS

Figure 16

# Fast Fourier Transform (FFT) PLOT

Figure 17

# Fast Fourier Transform (FFT) PLOT

Figure 18

# INTEGRAL NONLINEARITY ERROR vs DIGITAL OUTPUT CODES

# DIFFERENTIAL NONLINEARITY ERROR VS

Figure 20

#### 2048 POINTS FAST FOURIER TRANSFORM (FFT)

Figure 21

# 2048 POINTS FAST FOURIER TRANSFORM (FFT)

Figure 22

#### **TYPICAL CHARACTERISTICS**

Figure 27

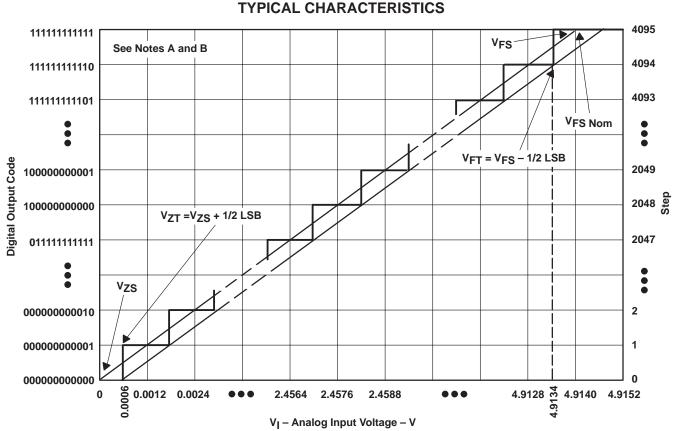

- NOTES: A. This curve is based on the assumption that  $V_{ref+}$  and  $V_{ref-}$  have been adjusted so that the voltage at the transition from digital 0 to 1 ( $V_{ZT}$ ) is 0.0006 V, and the transition to full scale ( $V_{FT}$ ) is 4.9134 V, 1 LSB = 1.2 mV.

- B. The full scale value (VFS) is the step whose nominal midstep value has the highest absolute value. The zero-scale value (VZS) is the step whose nominal midstep value equals zero.

Figure 29. Ideal 12-Bit ADC Conversion Characteristics

#### **APPLICATION INFORMATION**

Figure 30. Typical Interface to a TMS320 DSP

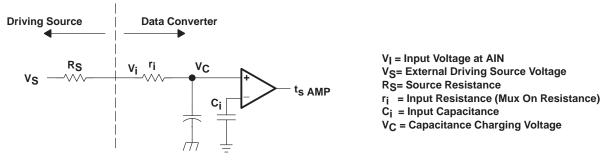

#### simplified analog input analysis

Using the equivalent circuit in Figure 31, the time required to charge the analog input capacitance from 0 to Vs within 1/2 LSB can be derived as follows.

The capacitance charging voltage is given by:

$$Vc = Vs\left(1 - EXP\left(\frac{-tch}{Rt \times Ci}\right)\right)$$

(1)

Where:

The input impedance Zi is 0.5 k $\Omega$  at 5 V, and is higher (~ 0.6 k $\Omega$ ) at 2.7 V. The final voltage to 1/2 LSB is given by:

$$Vc (1/2 LSB) = Vs - \left(\frac{Vs}{8192}\right)$$

(2)

#### **APPLICATION INFORMATION**

# simplified analog input analysis (continued)

Equating equation 1 to equation 2 and solving for cycle time t<sub>c</sub> gives:

$$Vs - \left(\frac{Vs}{8192}\right) = Vs \left(1 - EXP\left(\frac{-tch}{Rt \times Ci}\right)\right)$$

(3)

and time to change to 1/2 LSB (equal to minimum sampling time) is:

$$tch (1/2 LSB) = Rt \times Ci \times In(8192) = Min[t(sample)]$$

Where:

$$ln(8192) = 9.011$$

Therefore, with the values given, the time for the analog input signal to settle is:

$$tch (1/2 LSB) = (Rs + 0.5 k\Omega) \times Ci \times In(8192)$$

(4)

This time must be less than the converter sample time shown in the timing diagrams. This is 12× SCLKs.

$$t_{(sample)} = 12 \times \frac{1}{f(SCLK)} \ge Min \left[ t_{(sample)} \right] = tch \left( \frac{1}{2} LSB \right)$$

(5)

Therefore the maximum SCLK frequency is:

$$\max \left[ f_{(SCLK)} \right] = \frac{12}{tch \ (1/2 \ LSB)} = \frac{12}{[ln(8192) \times Rt \times Ci]}$$

(6)

#### maximum conversion throughput

For a supply voltage of 5 V, if the source impedance is less than 1 k $\Omega$ , and the ADC analog input capacitance Ci is less than 50 pF, this equates to a minimum sampling time tch  $\left(\frac{1}{2} \ LSB\right)$  of 0.676  $\mu$ s (<1  $\mu$ s). Since the sampling time requires 12 SCLKs, the fastest SCLK frequency is 12/tch  $\left(\frac{1}{2} \ LSB\right)$  = 18 MHz for R<sub>S</sub>  $\leq$  1 k $\Omega$ .

The minimal total cycle time, t<sub>(cycle)</sub>, is given as:

$$t_{(cycle)} = t_{(sample)} + tc + t_{(overhead)} = \frac{16}{Max [f(SCLK)]} + 3.5 \ \mu s + 0.1 \ \mu s = 4.5 \ \mu s$$

This is equivalent to a maximum throughput, max[fs] of 222 KSPS.

The throughput can be even higher with a smaller source impedance. When source impedance is 100  $\Omega$ , the minimum sampling time becomes:

$$tch (1/2 LSB) = Rt \times Ci \times In(8192) = 0.27 \ \mu s$$

#### APPLICATION INFORMATION

# maximum conversion throughput (continued)

The maximum SCLK frequency possible is 12/tch  $\left(\frac{1}{2} LSB\right)$  = 44 MHz. Then a 20 MHz clock (maximum SCLK frequency allowed for the internal comparator can be used. The minimum total cycle time is then reduced to:

$$t_{(cycle)} = t_{(sample)} + t_{C} + t_{(overhead)} = \frac{16}{max \left[f(SCLK)\right]} + 3.5 \ \mu s + 0.1 \ \mu s = 4.4 \ \mu s$$

The maximum throughput is  $1/4.4 \,\mu s = 227 \, KSPS$  for this case.

#### **Driving Source Requirements:**

NOTE: Noise and distortion must for the source be equivalent to the resolution of the converter.

R<sub>S</sub> must be real at the input frequency.

Figure 31. Equivalent Input Circuit Including the Driving Source

#### power down calculations

Total power consumption at different conversion rate  $f_s$ ,  $(f_s \le MAX [f_s])$  can be calculated by:

$$V_{DD} \times i(AVERAGE) = V_{DD} [(f_S/MAX [f_S]) \times i(ON) + (1-f_S/MAX [f_S]) \times i(OFF)]$$

If  $V_{DD} = 2.7 \text{ V}$  for TLV2541, and the sampling rate  $f_S = 10 \text{ kHz}$ , the maximum sampling rate  $f_{(SMAX)} = 200 \text{ kHz}$

then i(ON) = ~1 mA operating current and i(OFF) = ~2  $\mu$ A autopower-down current so V<sub>DD</sub> × i(AVERAGE) = 2.7 × (0.05 × 1000  $\mu$ A + 0.95 × 2  $\mu$ A) = (2.7 × 51.9)  $\mu$ W = 140  $\mu$ W

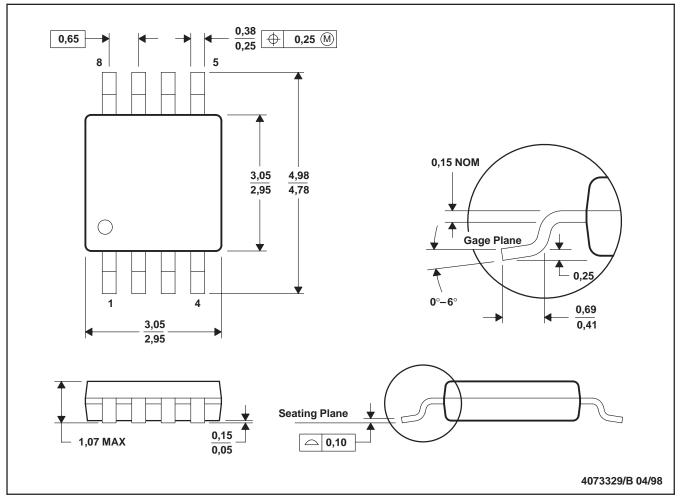

#### **MECHANICAL DATA**

# DGK (R-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-187

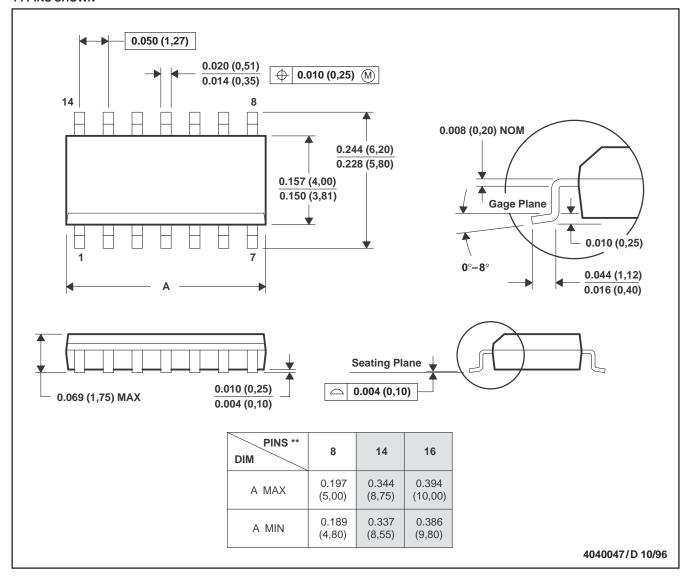

#### **MECHANICAL DATA**

# D (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PINS SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-012

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated