- High Speed

- 180 MHz Bandwidth (G = 1, -3 dB)

- 400 V/µs Slew Rate

- 40-ns Settling Time (0.1%)

- High Output Drive, I<sub>O</sub> = 115 mA (typ)

- Excellent Video Performance

- 75 MHz 0.1 dB Bandwidth (G = 1)

- 0.02% Differential Gain

- 0.02° Differential Phase

- Very Low Distortion

- THD = -72 dBc at f = 1 MHz

- Wide Range of Power Supplies

- $V_{CC} = \pm 5 \text{ V to } \pm 15 \text{ V}$

- Available in Standard SOIC, MSOP PowerPAD™, JG, or FK Package

- Evaluation Module Available

#### description

The THS4061 and THS4062 are generalpurpose, single/dual, high-speed voltage feedback amplifiers ideal for a wide range of applications including video, communication, and imaging. The devices offer very good ac performance with 180-MHz bandwidth, 400-V/µs slew rate, and 40-ns settling time (0.1%). The THS4061/2 are stable at all gains for both inverting and noninverting configurations. These amplifiers have a high output drive capability of 115 mA and draw only 7.8 mA supply current per channel. Excellent professional video results can be obtained with the low differential gain/phase errors of 0.02%/0.02° and wide 0.1 db flatness to 75 MHz. For applications requiring low distortion, the THS4061/2 is ideally suited with total harmonic distortion of -72 dBc at f = 1 MHz.

THS4061

CAUTION: The THS4061 and THS4062 provide ESD protection circuitry. However, permanent damage can still occur if this device is subjected to high-energy electrostatic discharges. Proper ESD precautions are recommended to avoid any performance degradation or loss of functionality

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Insruments Incorporated.

|           | RELATED DEVICES                              |

|-----------|----------------------------------------------|

| DEVICE    | DESCRIPTION                                  |

| THS4011/2 | 290-MHz Low Distortion High-Speed Amplifiers |

| THS4031/2 | 100-MHz Low Noise High Speed-Amplifiers      |

| THS4061/2 | 180-MHz High-Speed Amplifiers                |

#### **AVAILABLE OPTIONS**

| TA                | NUMBER OF<br>CHANNELS | PLASTIC<br>SMALL<br>OUTLINE†<br>(D) | PLASTIC<br>MSOP <sup>†</sup><br>(DGN) | CERAMIC<br>DIP<br>(JG) | CHIP<br>CARRIER<br>(FK) | MSOP<br>SYMBOL | EVALUATION<br>MODULES |

|-------------------|-----------------------|-------------------------------------|---------------------------------------|------------------------|-------------------------|----------------|-----------------------|

| 0°C to            | 1                     | THS4061CD                           | THS4061CDGN                           | _                      | _                       | TIABS          | THS4061EVM            |

| 70°C              | 2                     | THS4062CD                           | THS4062CDGN                           | _                      | _                       | TIABM          | THS4062EVM            |

| –40°C to          | 1                     | THS4061ID                           | THS4061IDGN                           | _                      | _                       | TIABT          | _                     |

| 85°C              | 2                     | THS4062ID                           | THS4062IDGN                           | _                      | _                       | TIABN          | _                     |

| –55°C to<br>125°C | 1                     | _                                   | _                                     | THS4061MJG             | THS4061MFK              | _              | _                     |

<sup>†</sup> The D and DGN packages are available taped and reeled. Add an R suffix to the device type (i.e., THS4061CDGNR).

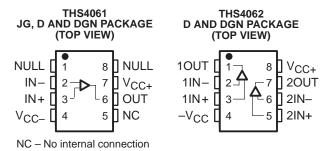

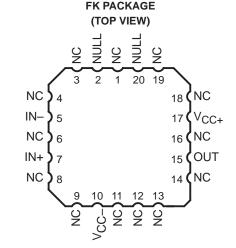

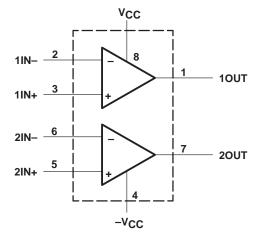

# functional block diagram

Figure 1. THS4061 - Single Channel

Figure 2. THS4062 - Dual Channel

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub> + to V <sub>CC</sub> |                                          | 33 V                         |

|------------------------------------------------------|------------------------------------------|------------------------------|

| Input voltage, V <sub>I</sub>                        |                                          | ±V <sub>CC</sub>             |

| Output current, IO                                   |                                          | 150 mA                       |

| Differential input voltage, V <sub>IO</sub>          |                                          | ±4 V                         |

| Continuous total power dissipation                   |                                          | See Dissipation Rating Table |

| Maximum junction temperature, T <sub>J</sub>         |                                          | 150°C                        |

| Operating free-air temperature, T <sub>A</sub> :     | C-suffix                                 | 0°C to 70°C                  |

|                                                      | I-suffix                                 | –40°C to 85°C                |

|                                                      | M-suffix                                 | –55°C to 125°C               |

| Storage temperature, T <sub>sta</sub>                |                                          | 65°C to 150°C                |

|                                                      | h) from case for 10 seconds, D and DGN p |                              |

| Lead temperature 1,6 mm (1/16 incl                   | h) from case for 60 seconds, JG package  | 300°C                        |

| Case temperature for 60 seconds, F                   | FK package                               | 260°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE          | T <sub>A</sub> ≤ 25°C<br>POWER RATING | ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, |        | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|------------------|---------------------------------------|----------------------------------------|--------|---------------------------------------|----------------------------------------|

| D                | 740 mW                                | 6 mW/°C                                | 475 mW | 385 mW                                | _                                      |

| DGN <sup>‡</sup> | 2.14 W                                | 17.1 mW/°C                             | 1.37 W | 1.11 W                                | _                                      |

| JG               | 1057 mW                               | 8.4 mW/°C                              | 627 mW | 546 mW                                | 210 mW                                 |

| FK               | 1375 mW                               | 11 mW/°C                               | 880 mW | 715 mW                                | 275 mW                                 |

<sup>&</sup>lt;sup>‡</sup> The DGN package incorporates a PowerPAD on the underside of the device. This acts as a heatsink and must be connected to a thermal dissipation plane for proper power dissipation. Failure to do so can result in exceeding the maximum specified junction temperature, which could permanently damage the device.

# recommended operating conditions

|                                                         |               | MIN  | NOM MAX | UNIT |

|---------------------------------------------------------|---------------|------|---------|------|

| Supply voltage Vee Land Vee                             | Dual supply   | ±4.5 | ±16     | V    |

| Supply voltage, V <sub>CC</sub> + and V <sub>CC</sub> - | Single supply | 9    | 32      | ]    |

|                                                         | C-suffix      | 0    | 70      |      |

| Operating free-air temperature, TA                      | I-suffix      | -40  | 85      | °C   |

|                                                         | M-suffix      | -55  | 125     | ]    |

# electrical characteristics at T<sub>A</sub> = 25°C, V<sub>CC</sub> = $\pm 15$ V, R<sub>L</sub> = 150 $\Omega$ (unless otherwise noted)

# dynamic performance

|                | PARAMETER                                          | TEST CONDITIONS <sup>†</sup>                                                 | TEST CONDITIONS <sup>†</sup> |         |     | UNIT    |  |

|----------------|----------------------------------------------------|------------------------------------------------------------------------------|------------------------------|---------|-----|---------|--|

|                |                                                    |                                                                              |                              | MIN TYP | MAX |         |  |

|                |                                                    | V <sub>CC</sub> = ±5 V                                                       | Gain = 1                     | 180     |     | MHz     |  |

|                | Dynamic performance small-signal bandwidth (–3 dB) | V <sub>CC</sub> = ±15 V                                                      | Gain = -1                    | 50      |     | MHz     |  |

| BW             |                                                    | $V_{CC} = \pm 5 \text{ V}$                                                   | Gairr = -1                   | 50      |     | IVITZ   |  |

|                | Bandwidth for 0.1 dB flatness                      | $V_{CC} = \pm 15 \text{ V}$                                                  | Gain = 1                     | 75      | MHz |         |  |

|                | Bandwidth for 0.1 dB flatness                      | V <sub>CC</sub> = ±5 V                                                       | Gaiii = 1                    | 20      |     | 1711172 |  |

| SR             | Slew rate                                          | $V_{CC} = \pm 15 \text{ V}$                                                  | Gain = -1                    | 400     |     | V/μs    |  |

| J SK           | Siew rate                                          | V <sub>CC</sub> = ±5 V                                                       | Gaiii = -1                   | 350     |     |         |  |

|                | Settling time to 0.1%                              | $V_{CC} = \pm 15 \text{ V},  5-\text{V step } (0 \text{ V to } 5 \text{ V})$ | Gain = -1                    | 40      |     | ns      |  |

| <b> </b> .     | Settling time to 0.1%                              | $V_{CC} = \pm 5 \text{ V}, \qquad V_{O} = -2.5 \text{ V to } 2.5 \text{ V},$ | Gairr = -1                   | 40      |     |         |  |

| t <sub>S</sub> | Settling time to 0.01%                             | $V_{CC} = \pm 15 \text{ V},  5-\text{V step } (0 \text{ V to } 5 \text{ V})$ | Gain = -1                    | 140     |     |         |  |

|                | Setting time to 0.01%                              | $V_{CC} = \pm 5 \text{ V}, \qquad V_{O} = -2.5 \text{ V to } 2.5 \text{ V},$ | ] Gaiii = -1                 | 150     |     | ns      |  |

<sup>†</sup> Full range = 0°C to 70°C for C suffix and -40°C to 85°C for I suffix

# noise/distortion performance

|     | PARAMETER                                   | TEST CONDITIONS <sup>†</sup> |                                                 |                            | THS4061C/I,<br>THS4062C/I |           |     | UNIT   |

|-----|---------------------------------------------|------------------------------|-------------------------------------------------|----------------------------|---------------------------|-----------|-----|--------|

|     |                                             |                              |                                                 |                            |                           |           | MAX |        |

| THD | Total harmonic distortion                   | f = 1 MHz                    |                                                 |                            |                           | -72       |     | dBc    |

| ٧n  | Input voltage noise                         | f = 10 kHz,                  | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ |                            |                           | 14.5      |     | nV/√Hz |

| In  | Input current noise                         | f = 10 kHz,                  | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ |                            |                           | 1.6       |     | pA/√Hz |

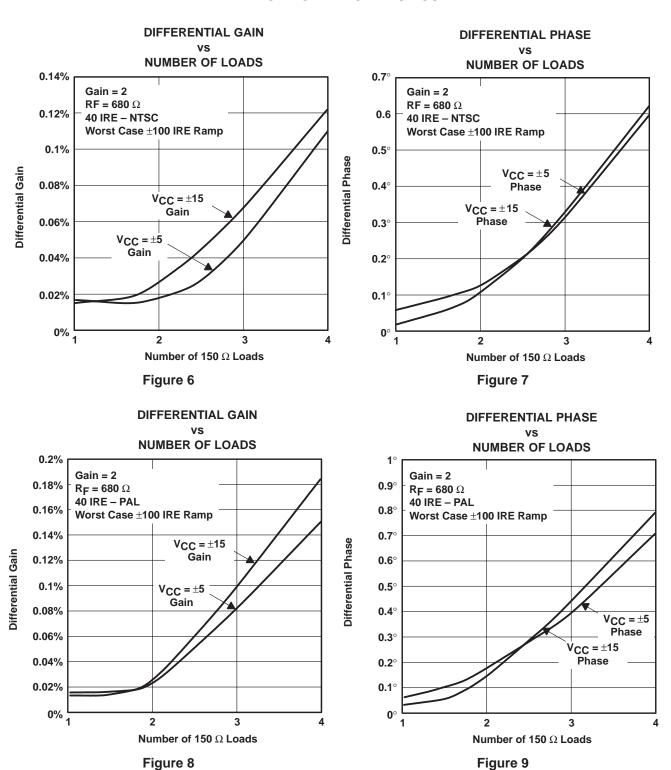

|     | Differential raise array                    | Onin 0                       | NTCC 40 IDF are dislosted                       | V <sub>CC</sub> = ±15 V    |                           | 0.02<br>% |     |        |

|     | Differential gain error                     | Gain = 2,                    | NTSC, 40 IRE modulation                         | V <sub>CC</sub> = ±5 V     |                           | 0.02<br>% |     |        |

|     | Differential above some                     | Cain 0                       | NITCO 40 IDE modulation                         | V <sub>CC</sub> = ±15 V    |                           | 0.02°     |     |        |

|     | Differential phase error                    | Gain = 2,                    | NTSC, 40 IRE modulation                         | $V_{CC} = \pm 5 \text{ V}$ |                           | 0.06°     |     |        |

|     | Channel-to-channel crosstalk (THS4062 only) | $V_{CC} = \pm 5 \text{ V c}$ | or ±15 V, f = 1 MHz                             |                            |                           | 65        |     | dB     |

<sup>†</sup> Full range = 0°C to 70°C for C suffix and -40°C to 85°C for I suffix

# dc performance

|                 | PARAMETER            | TEST CONDITIONS†                                                                         |                             |     | THS4061C/I,<br>THS4062C/I |     |        |

|-----------------|----------------------|------------------------------------------------------------------------------------------|-----------------------------|-----|---------------------------|-----|--------|

|                 |                      |                                                                                          |                             |     |                           | MAX |        |

|                 | Open loop gain       | $IVCC = \pm 15 V$ , $VC = \pm 10 V$ , $R_1 = 1 K\Omega$                                  | T <sub>A</sub> = 25°C       | 5   | 15                        |     | V/mV   |

|                 |                      |                                                                                          | T <sub>A</sub> = full range | 4   |                           |     | V/IIIV |

|                 | Open loop gain       | Voc = +5 V Vo = +2 5 V Pr = 1 k0                                                         | T <sub>A</sub> = 25°C       | 2.5 | 8                         |     | V/mV   |

|                 |                      | $V_{CC} = \pm 5 \text{ V}, \qquad V_{O} = \pm 2.5 \text{ V},  R_{L} = 1 \text{ k}\Omega$ | T <sub>A</sub> = full range | 2   |                           |     |        |

| \/00            | Input offset voltage | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                          | Ta - full rongo             |     | 2.5                       | 8   | mV     |

| Vos             | Offset drift         | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                          | T <sub>A</sub> = full range |     | 15                        |     | μV/°C  |

| I <sub>IB</sub> | Input bias current   | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                          | T <sub>A</sub> = full range |     | 3                         | 6   | μΑ     |

| los             | Input offset current | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                          | T <sub>A</sub> = full range |     | 75                        | 250 | nA     |

|                 | Offset current drift | T <sub>A</sub> = full range                                                              |                             |     | 0.3                       |     | nA/°C  |

<sup>†</sup> Full range = 0°C to 70°C for C suffix and -40°C to 85°C for I suffix

# electrical characteristics at T\_A = 25 °C, V\_{CC} = $\pm 15$ V, R\_L = 150 $\Omega$ (unless otherwise noted) (continued)

# input characteristics

|                | PARAMETER                       |                              | TEST CONDITIONS <sup>†</sup> |                             |       | THS4061C/I,<br>THS4062C/I |     |    |

|----------------|---------------------------------|------------------------------|------------------------------|-----------------------------|-------|---------------------------|-----|----|

|                |                                 |                              |                              |                             | MIN   | TYP                       | MAX |    |

| V. 0.5         | Common mode input voltage range | V <sub>CC</sub> = ±15 V      |                              |                             | ±13.8 | ±14.1                     |     | V  |

| VICR           | Common-mode input voltage range | V <sub>CC</sub> = ±5 V       |                              |                             | ±3.8  | ±4.3                      |     | ]  |

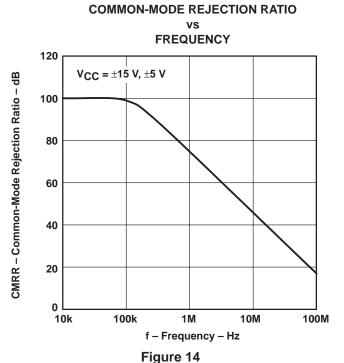

| CMRR           | Common mode rejection ratio     | $V_{CC} = \pm 15 \text{ V},$ | $V_{ICR} = \pm 12 V$         | T <sub>A</sub> = full range | 70    | 110                       |     | dB |

| CIVIRR         | Common mode rejection ratio     | $V_{CC} = \pm 5 \text{ V},$  | V <sub>ICR</sub> = ±2.5 V    |                             | 70    | 95                        |     |    |

| R <sub>I</sub> | Input resistance                |                              | •                            |                             |       | 1                         |     | МΩ |

| Ci             | Input capacitance               |                              |                              |                             |       | 2                         |     | pF |

<sup>†</sup> Full range = 0°C to 70°C for C suffix and -40°C to 85°C for I suffix

#### output characteristics

| PARAMETER |                       | TEST CONDITIONS†            |                         |       | THS4061C/I,<br>THS4062C/I |     |     |

|-----------|-----------------------|-----------------------------|-------------------------|-------|---------------------------|-----|-----|

|           |                       |                             |                         | MIN   | TYP                       | MAX | 1   |

| Va        |                       | V <sub>CC</sub> = ±15 V     | R <sub>L</sub> = 250 Ω  | ±11.5 | ±12.5                     |     | V   |

|           | Output voltage owing  | $V_{CC} = \pm 5 \text{ V}$  | R <sub>L</sub> = 150 Ω  | ±3.2  | ±3.5                      |     | v v |

| Vo        | Output voltage swing  | $V_{CC} = \pm 15 \text{ V}$ | - R <sub>L</sub> = 1 kΩ | ±13   | ±13.5                     |     | V   |

|           |                       | $V_{CC} = \pm 5 \text{ V}$  |                         | ±3.5  | ±3.7                      |     |     |

|           | Output oursent        | V <sub>CC</sub> = ±15 V     | B. 20.0                 | 80    | 115                       |     | A   |

| Ю         | Output current        | V <sub>CC</sub> = ±5 V      | $R_L = 20 \Omega$       | 50    | 75                        |     | mA  |

| ISC       | Short-circuit current | V <sub>CC</sub> = ±15 V     |                         |       | 150                       |     | mA  |

| RO        | Output resistance     | Open loop                   |                         |       | 12                        |     | Ω   |

<sup>†</sup> Full range = 0°C to 70°C for C suffix and -40°C to 85°C for I suffix

#### power supply

|          | PARAMETER                          | TEST CONDITIONS <sup>†</sup>                    |                             |     | THS4061C/I,<br>THS4062C/I |       |    |  |

|----------|------------------------------------|-------------------------------------------------|-----------------------------|-----|---------------------------|-------|----|--|

|          |                                    |                                                 |                             | MIN | TYP                       | MAX   |    |  |

| \/       | Voc Supply voltage energting range | Dual supply                                     |                             |     |                           | ±16.5 | V  |  |

| VCC      | Supply voltage operating range     | Single supply                                   |                             |     |                           | 33    | V  |  |

|          | Ovicement ourset (nor emplifier)   | V <sub>CC</sub> = ±15 V                         | T. full ronge               |     | 7.8                       | 10.5  | A  |  |

| lcc      | Quiescent current (per amplifier)  | V <sub>CC</sub> = ±5 V                          | T <sub>A</sub> = full range |     | 7.3                       | 10    | mA |  |

| PSRR     | Dower cumply rejection ratio       | V 15 V - 145 V                                  | T <sub>A</sub> = 25°C       | 70  | 78                        |       | dB |  |

| PSRR POW | Power supply rejection ratio       | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ | T <sub>A</sub> = full range | 68  |                           |       | ub |  |

<sup>†</sup> Full range = 0°C to 70°C for C suffix and -40°C to 85°C for I suffix

SLOS234D – DECEMBER 1998 – REVISED FEBRUARY 2000

# electrical characteristics at T<sub>A</sub> = 25°C, V<sub>CC</sub> = $\pm 15$ V, R<sub>L</sub> = 150 $\Omega$ (unless otherwise noted)

# dynamic performance

|                | PARAMETER                        |                              |                                           |                             | THS4061M |     |     | UNIT    |  |

|----------------|----------------------------------|------------------------------|-------------------------------------------|-----------------------------|----------|-----|-----|---------|--|

|                | PARAMETER                        |                              | TEST CONDITIONS†                          |                             |          | TYP | MAX | UNIT    |  |

|                | Unity-gain bandwidth             | Closed loop,                 | $R_L = 1 k\Omega$                         | $V_{CC} = \pm 15 \text{ V}$ | *140     | 180 |     | MHz     |  |

| BW             |                                  | $V_{CC} = \pm 15 \text{ V}$  |                                           | Gain = 1                    |          | 180 |     | MHz     |  |

|                | Dynamic performance small-signal | $V_{CC} = \pm 5 \text{ V}$   |                                           | Gairr = 1                   |          | 180 |     | IVIHZ   |  |

|                | bandwidth (-3 dB)                | $V_{CC} = \pm 15 \text{ V}$  |                                           | Gain = -1                   |          | 50  |     | MHz     |  |

|                |                                  | $V_{CC} = \pm 5 \text{ V}$   |                                           | Gairr = -1                  |          | 50  |     | ] IVITZ |  |

|                | Denoted the for 0.4 dD flaters   | V <sub>CC</sub> = ±15 V      |                                           | Gain = 1                    |          | 75  |     | MHz     |  |

|                | Bandwidth for 0.1 dB flatness    | $V_{CC} = \pm 5 \text{ V}$   |                                           | Gain = 1                    |          | 20  |     |         |  |

| SR             | Slew rate                        | V <sub>CC</sub> = ±15 V      | $R_L = 1 k\Omega$                         |                             | *400     | 500 |     | V/μs    |  |

|                | Cottling time to 0.40/           | $V_{CC} = \pm 15 \text{ V},$ | 5-V step (0 V to 5 V)                     | Gain = -1                   |          | 40  |     | ns      |  |

| ١.             | Settling time to 0.1%            | $V_{CC} = \pm 5 \text{ V},$  | $V_0 = -2.5 \text{ V to } 2.5 \text{ V},$ | Gain = -1                   |          | 40  |     |         |  |

| t <sub>S</sub> | Sattling time to 0.019/          | $V_{CC} = \pm 15 \text{ V},$ | 5-V step (0 V to 5 V)                     | Gain = -1                   |          | 140 |     | ns      |  |

|                | Settling time to 0.01%           | $V_{CC} = \pm 5 \text{ V},$  | $V_0 = -2.5 \text{ V to } 2.5 \text{ V},$ | Gaiii = -1                  |          | 150 |     |         |  |

<sup>†</sup> Full range =  $-55^{\circ}$ C to 125°C for M suffix

## noise/distortion performance

| PARAMETER TEST CONDITIONS |                           |                                   | TEST CONDITIONS <sup>†</sup>                                                                         |                         | THS4061M                |       |      | UNIT               |   |

|---------------------------|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|------|--------------------|---|

| FARAMETER                 |                           | TEST CONDITIONS†                  |                                                                                                      |                         | MIN                     | TYP   | MAX  | ONIT               |   |

| THD                       | Total harmonic distortion | f = 1 MHz                         |                                                                                                      |                         |                         | -72   |      | dBc                |   |

| ٧n                        | Input voltage noise       | f = 10 kHz,                       | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                                      |                         |                         | 14.5  |      | nV/√ <del>Hz</del> |   |

| In                        | Input current noise       | f = 10 kHz,                       | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                                      |                         |                         | 1.6   |      | pA/√Hz             |   |

|                           | Differential gain array   | Coin 2 Ni                         | ntial gain error Gain = 2, NTSC, 40 IRE Modulation $\frac{\text{VCC} = \pm 15 \text{ V}}{\text{CC}}$ | V(                      | V <sub>CC</sub> = ±15 V |       | 0.02 |                    | % |

|                           | Differential gain error   | $V_{CC} = \pm 5 \text{ V}$        |                                                                                                      | V <sub>CC</sub> = ±5 V  | 0.02                    |       |      | 70                 |   |

|                           | Differential phase array  | Ocio 2 NITCO 40 IDE Modulation    |                                                                                                      | V <sub>CC</sub> = ±15 V |                         | 0.02° |      |                    |   |

|                           | Differential phase error  | Gain = 2, NTSC, 40 IRE Modulation | V <sub>CC</sub> = ±5 V                                                                               |                         | 0.06°                   |       |      |                    |   |

<sup>†</sup> Full range =  $-55^{\circ}$ C to 125°C for M suffix

#### dc performance

| PARAMETER       |                      | TEST CONDITIONS†                                                                     |                         |                             | THS4061M |     |     | UNIT   |

|-----------------|----------------------|--------------------------------------------------------------------------------------|-------------------------|-----------------------------|----------|-----|-----|--------|

|                 |                      |                                                                                      |                         |                             | MIN      | TYP | MAX | UNIT   |

| Open loop gain  |                      | $V_{CC} = \pm 15 \text{ V},  V_{O} = \pm 10 \text{ V}$                               | $V$ , $R_L = 1 k\Omega$ | Ta - full rongo             | 5        | 9   |     | V/mV   |

|                 |                      | $V_{CC} = \pm 5 \text{ V}, \qquad V_O = \pm 2.5 \text{ V},  R_L = 1 \text{ k}\Omega$ |                         | T <sub>A</sub> = full range | 2.5      | 6   |     | V/IIIV |

|                 | Input offset voltage | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$ R                                    | P. – 1 kO               | T <sub>A</sub> = 25°C       |          | 2.5 | 8   | mV     |

| V <sub>IO</sub> |                      |                                                                                      | $R_L = 1 k\Omega$       | T <sub>A</sub> = full range |          |     | 9   | mV     |

|                 | Offset drift         | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                      | $R_L = 1 k\Omega$       | T <sub>A</sub> = full range |          | 15  |     | μV/°C  |

| $I_{IB}$        | Input bias current   | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                      | $R_L = 1 k\Omega$       | T <sub>A</sub> = full range |          | 3   | 6   | μΑ     |

| IIO             | Input offset current | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                      | $R_L = 1 k\Omega$       | T <sub>A</sub> = full range |          | 75  | 250 | nA     |

|                 | Offset current drift | $V_{CC} = \pm 5 \text{ V or } \pm 15 \text{ V}$                                      | $R_L = 1 k\Omega$       | T <sub>A</sub> = full range |          | 0.3 |     | nA/°C  |

<sup>†</sup> Full range =  $-55^{\circ}$ C to 125°C for M suffix

<sup>\*</sup>This parameter is not tested.

# electrical characteristics at $T_A$ = full range, $V_{CC}$ = $\pm 15$ V, $R_L$ = 1 k $\Omega$ (unless otherwise noted) (continued)

# input characteristics

|                | PARAMETER                       | TEST COMPLICACT                                                |       | THS4061M |     |      |

|----------------|---------------------------------|----------------------------------------------------------------|-------|----------|-----|------|

|                | PARAINETER                      | TEST CONDITIONS <sup>†</sup>                                   | MIN   | TYP      | MAX | UNIT |

| VICR           | Common-mode input voltage range | $V_{CC} = \pm 15 \text{ V}$                                    | ±13.8 | ±14.1    |     | V    |

|                |                                 | $V_{CC} = \pm 5 V$                                             | ±3.8  | ±4.3     |     |      |

| CMRR           | Common mode rejection ratio     | $V_{CC} = \pm 15 \text{ V}, \qquad V_{ICR} = \pm 12 \text{ V}$ | 70    | 86       |     | dB   |

| CIVIKK         | Common mode rejection ratio     | $V_{CC} = \pm 5 \text{ V}, \qquad V_{ICR} = \pm 2.5 \text{ V}$ | 80    | 90       |     | uБ   |

| R <sub>I</sub> | Input resistance                |                                                                |       | 1        |     | МΩ   |

| Ci             | Input capacitance               |                                                                |       | 2        |     | pF   |

<sup>†</sup> Full range =  $-55^{\circ}$ C to 125°C for M suffix

## output characteristics

| PARAMETER      |                       | TEST CONDITIONS <sup>†</sup> |                       | THS4061M |       |     | UNIT  |

|----------------|-----------------------|------------------------------|-----------------------|----------|-------|-----|-------|

|                |                       |                              |                       | MIN      | TYP   | MAX | CIVIT |

|                |                       | V <sub>CC</sub> = ±15 V      | $R_L = 250 \Omega$    | ±12      | ±13.1 |     | V     |

| v <sub>O</sub> | Output voltage ewing  | V <sub>CC</sub> = ±5 V       | $R_L = 150 \Omega$    | ±3.2     | ±3.5  |     | V     |

|                | Output voltage swing  | V <sub>CC</sub> = ±15 V      | R <sub>L</sub> = 1 kΩ | ±13      | ±13.5 |     | V     |

|                |                       | V <sub>CC</sub> = ±5 V       |                       | ±3.5     | ±3.7  |     |       |

| 1              | Output oursest        | V <sub>CC</sub> = ±15 V      | R <sub>L</sub> = 20 Ω | 70       | 115   |     | mA    |

| 10             | Output current        | V <sub>CC</sub> = ±5 V       |                       | 50       | 75    |     |       |

| ISC            | Short-circuit current | V <sub>CC</sub> = ±15 V      | T <sub>A</sub> = 25°C |          | 150   |     | mA    |

| RO             | Output resistance     | Open loop                    |                       |          | 12    |     | Ω     |

<sup>†</sup> Full range = -55°C to 125°C for M suffix

## power supply

| PARAMETER |                                | TEST SOMBITIONS!                |                             | THS4061M |     |       | UNIT |

|-----------|--------------------------------|---------------------------------|-----------------------------|----------|-----|-------|------|

|           | PARAMETER                      | TEST CONDITIONS†                |                             | MIN      | TYP | MAX   | UNIT |

| Vac       | Supply voltage operating range | Dual supply                     |                             | ±4.5     |     | ±16.5 | V    |

| VCC       | Supply voltage operating range | Single supply                   |                             | 9        |     | 33    | ľ    |

|           | Quiescent current              | $V_{CC} = \pm 15 \text{ V}$     | 1A = 25°C                   |          | 7.8 | 9     | mA   |

|           |                                | $V_{CC} = \pm 5 \text{ V}$      |                             |          | 7.3 | 8.5   |      |

| ICC       |                                | V <sub>CC</sub> = ±15 V         |                             |          |     | 11    | IIIA |

|           |                                | $V_{CC} = \pm 5 \text{ V}$      | T <sub>A</sub> = full range |          |     | 10.5  |      |

| PSRR      | Power supply rejection ratio   | V <sub>CC</sub> = ±5 V or ±15 V | T <sub>A</sub> = 25°C       | 76       | 80  |       | dB   |

| PSKK      |                                |                                 | T <sub>A</sub> = full range | 74       | 78  |       | ub   |

<sup>†</sup> Full range =  $-55^{\circ}$ C to 125°C for M suffix

# **TYPICAL CHARACTERISTICS**

|                    |                              |                         | FIGURE |

|--------------------|------------------------------|-------------------------|--------|

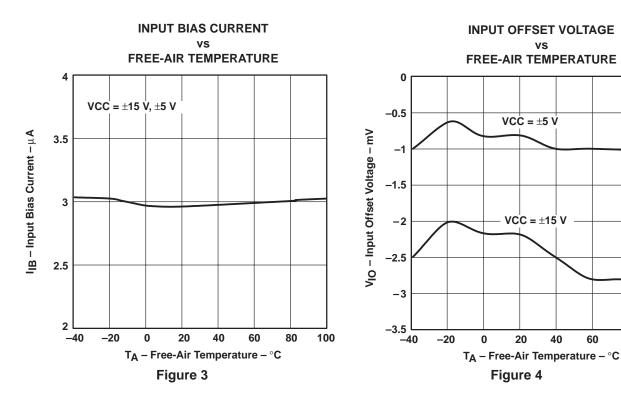

| l <sub>IB</sub>    | Input bias current           | vs Free-air temperature | 3      |

| VIO                | Input offset voltage         | vs Free-air temperature | 4      |

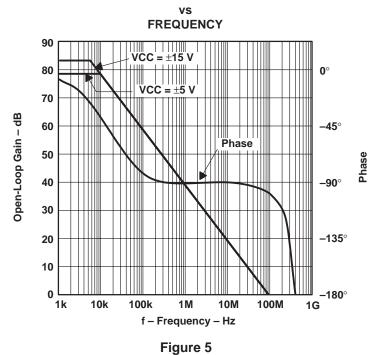

|                    | Open-loop gain               | vs Frequency            | 5      |

|                    | Phase                        | vs Frequency            | 5      |

|                    | Differential gain            | vs Number of loads      | 6, 8   |

|                    | Differential phase           | vs Number of loads      | 7, 9   |

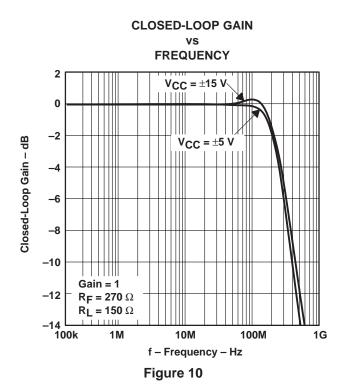

|                    | Closed-loop gain             | vs Frequency            | 10, 11 |

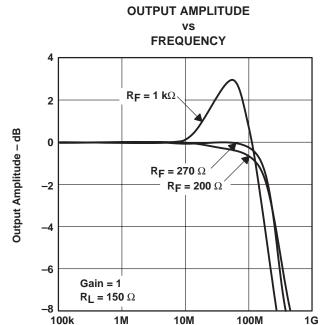

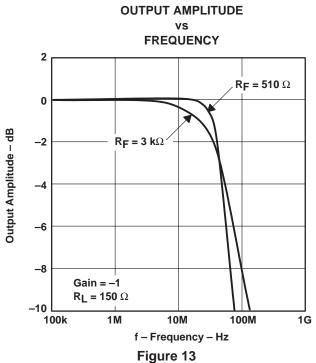

|                    | Output Amplitude             | vs Frequency            | 12, 13 |

| CMRR               | Common-mode rejection ratio  | vs Frequency            | 14     |

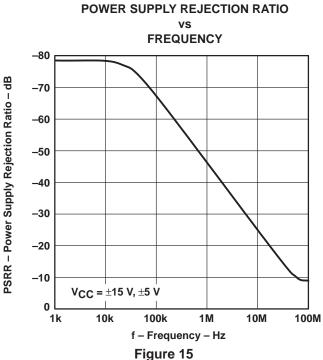

| PSRR               | Dower cumby rejection retio  | vs Frequency            | 15     |

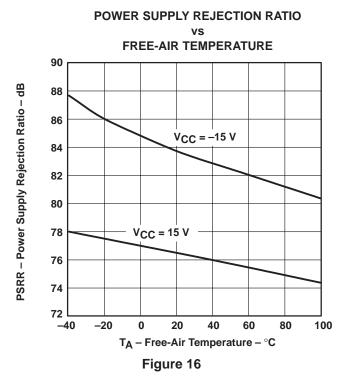

| PSKK               | Power-supply rejection ratio | vs Free-air temperature | 16     |

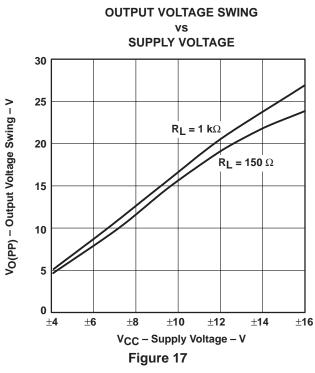

| V <sub>O(PP)</sub> | Output voltage swing         | vs Supply voltage       | 17     |

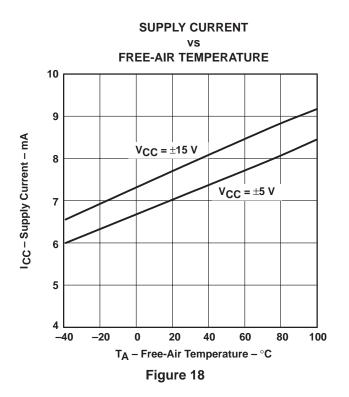

| Icc                | Supply current               | vs Free-air temperature | 18     |

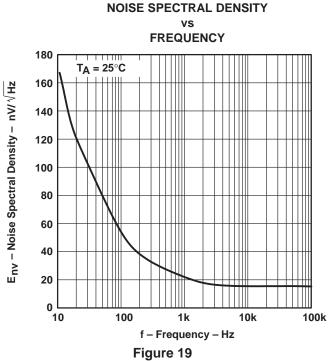

| Env                | Noise spectral density       | vs Frequency            | 19     |

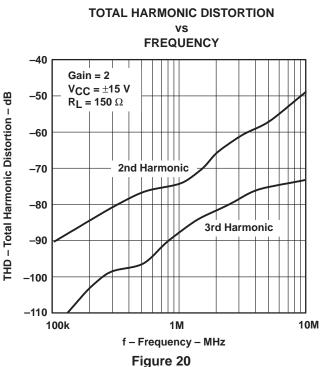

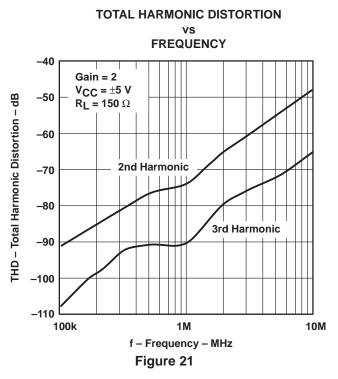

| THD                | Total harmonic distortion    | vs Frequency            | 20, 21 |

80

100

# **TYPICAL CHARACTERISTICS**

#### **OPEN-LOOP GAIN AND PHASE**

#### TYPICAL CHARACTERISTICS

**CLOSED-LOOP GAIN**

**FREQUENCY**

#### **TYPICAL CHARACTERISTICS**

5

0 Closed-Loop Gain - dB -5 -10 $V_{CC} = \pm 15 \text{ V}, \pm 5 \text{ V}$ Gain = -1 -15  $R_F = 510 \Omega$  $R_L = 150 \Omega$ -20 100k 1M 10M 100M 1G f - Frequency - Hz Figure 11

f - Frequency - Hz

Figure 12

#### TYPICAL CHARACTERISTICS

#### TYPICAL CHARACTERISTICS

# theory of operation

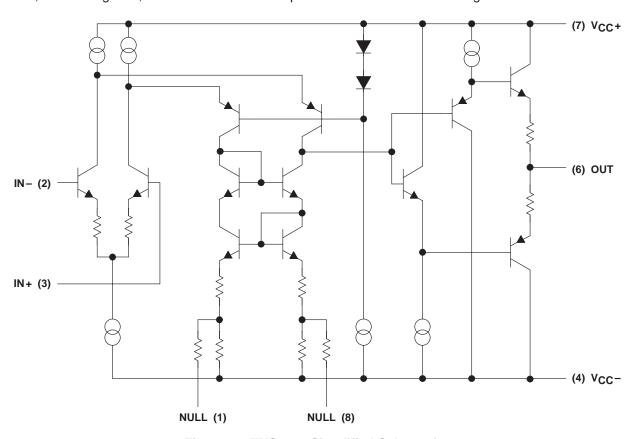

The THS406x is a high speed, operational amplifier configured in a voltage feedback architecture. It is built using a 30-V, dielectrically isolated, complementary bipolar process with NPN and PNP transistors possessing  $f_{TS}$  of several GHz. This results in an exceptionally high performance amplifier that has a wide bandwidth, high slew rate, fast settling time, and low distortion. A simplified schematic is shown in Figure 22.

Figure 22. THS4061 Simplified Schematic

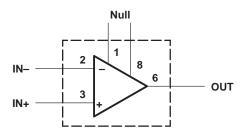

# offset nulling

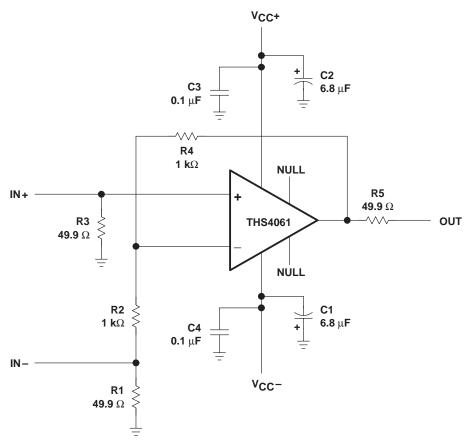

The THS4061 has very low input offset voltage for a high-speed amplifier. However, if additional correction is required, an offset nulling function has been provided. By placing a potentiometer between terminals 1 and 8 and tying the wiper to the negative supply, the input offset can be adjusted. This is shown in Figure 23.

Figure 23. Offset Nulling Schematic

#### optimizing unity gain response

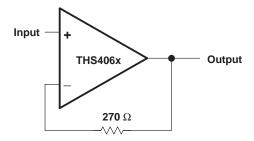

Internal frequency compensation of the THS406x was selected to provide very wideband performance yet still maintain stability when operated in a noninverting unity gain configuration. When amplifiers are compensated in this manner there is usually peaking in the closed loop response and some ringing in the step response for very fast input edges, depending upon the application. This is because a minimum phase margin is maintained for the G=+1 configuration. For optimum settling time and minimum ringing, a feedback resistor of  $270\,\Omega$  should be used as shown in Figure 24. Additional capacitance can also be used in parallel with the feedback resistance if even finer optimization is required.

Figure 24. Noninverting, Unity Gain Schematic

#### driving a capacitive load

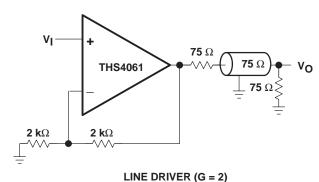

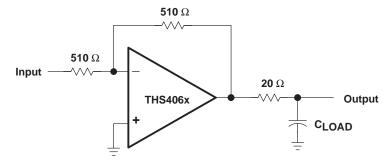

Driving capacitive loads with high performance amplifiers is not a problem as long as certain precautions are taken. The first is to realize that the THS406x has been internally compensated to maximize its bandwidth and slew rate performance. When the amplifier is compensated in this manner, capacitive loading directly on the output will decrease the device's phase margin leading to high frequency ringing or oscillations. Therefore, for capacitive loads of greater than 10 pF, it is recommended that a resistor be placed in series with the output of the amplifier, as shown in Figure 25. A minimum value of 20  $\Omega$  should work well for most applications. For example, in 75- $\Omega$  transmission systems, setting the series resistor value to 75  $\Omega$  both isolates any capacitance loading and provides the proper line impedance matching at the source end.

Figure 25. Driving a Capacitive Load

## circuit layout considerations

In order to achieve the levels of high frequency performance of the THS406x, it is essential that proper printed-circuit board high frequency design techniques be followed. A general set of guidelines is given below. In addition, a THS406x evaluation board is available to use as a guide for layout or for evaluating the device performance.

- Ground planes It is highly recommended that a ground plane be used on the board to provide all

components with a low inductive ground connection. However, in the areas of the amplifier inputs and

output, the ground plane can be removed to minimize the stray capacitance.

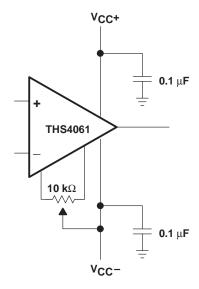

- Proper power supply decoupling Use a 6.8-μF tantalum capacitor in parallel with a 0.1-μF ceramic capacitor on each supply terminal. It may be possible to share the tantalum among several amplifiers depending on the application, but a 0.1-μF ceramic capacitor should always be used on the supply terminal of every amplifier. In addition, the 0.1-μF capacitor should be placed as close as possible to the supply terminal. As this distances increases, the inductance in the connecting trace makes the capacitor less effective. The designer should strive for distances of less than 0.1 inches between the device power terminals and the ceramic capacitors.

- Sockets Sockets are not recommended for high-speed operational amplifiers. The additional lead inductance in the socket pins will often lead to stability problems. Surface-mount packages soldered directly to the printed-circuit board is the best implementation.

- Short trace runs/compact part placements Optimum high frequency performance is achieved when stray series inductance has been minimized. To realize this, the circuit layout should be made as compact as possible thereby minimizing the length of all trace runs. Particular attention should be paid to the inverting input of the amplifier. Its length should be kept as short as possible. This will help to minimize stray capacitance at the input of the amplifier.

#### circuit layout considerations (continued)

Surface-mount passive components – Using surface-mount passive components is recommended for high-frequency amplifier circuits for several reasons. First, because of the extremely low lead inductance of surface-mount components, the problem with stray series inductance is greatly reduced. Second, the small size of surface-mount components naturally leads to a more compact layout, thereby minimizing both stray inductance and capacitance. If leaded components are used, it is recommended that the lead lengths be kept as short as possible.

#### evaluation board

An evaluation board is available for the THS4061 (literature number SLOP226) and THS4062 (literaure number SLOP235). This board has been configured for very low parasitic capacitance in order to realize the full performance of the amplifier. A schematic of the evaluation board is shown in Figure 26. The circuitry has been designed so that the amplifier may be used in either an inverting or noninverting configuration. To order the evaluation board contact your local TI sales office or distributor. For more detailed information, refer to the THS4061 EVM User's Manual (literature number SLOU038) or the THS4062 EVM User's Manual (literature number SLOU040)

Figure 26. THS4061 Evaluation Board Schematic

SLOS234D - DECEMBER 1998 - REVISED FEBRUARY 2000

#### **MECHANICAL INFORMATION**

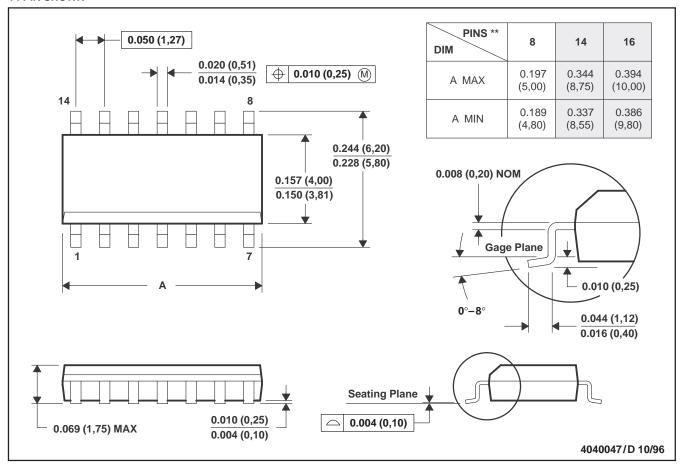

## D (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012

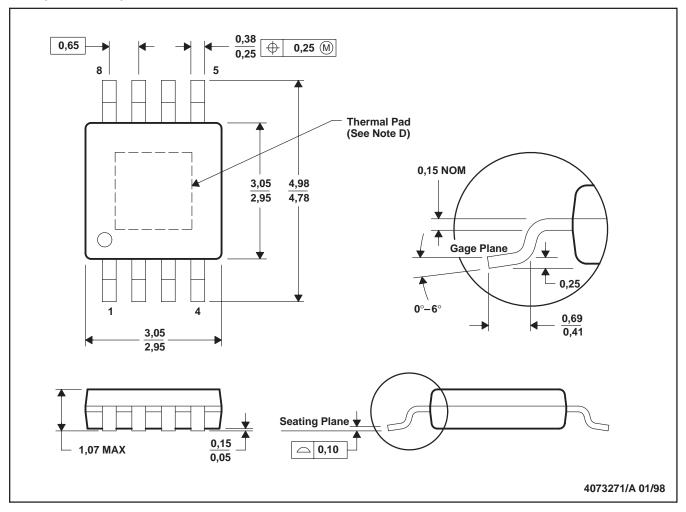

#### **MECHANICAL INFORMATION**

## DGN (S-PDSO-G8)

#### PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions include mold flash or protrusions.

- D. The package thermal performance may be enhanced by attaching an external heat sink to the thermal pad. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-187

PowerPAD is a trademark of Texas Instruments Incorporated.

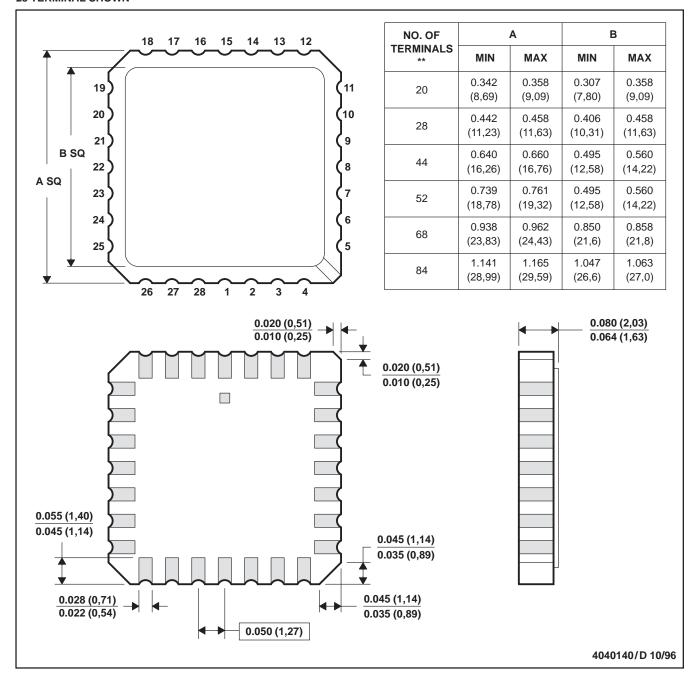

#### **MECHANICAL INFORMATION**

## FK (S-CQCC-N\*\*)

#### 28 TERMINAL SHOWN

#### LEADLESS CERAMIC CHIP CARRIER

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within JEDEC MS-004

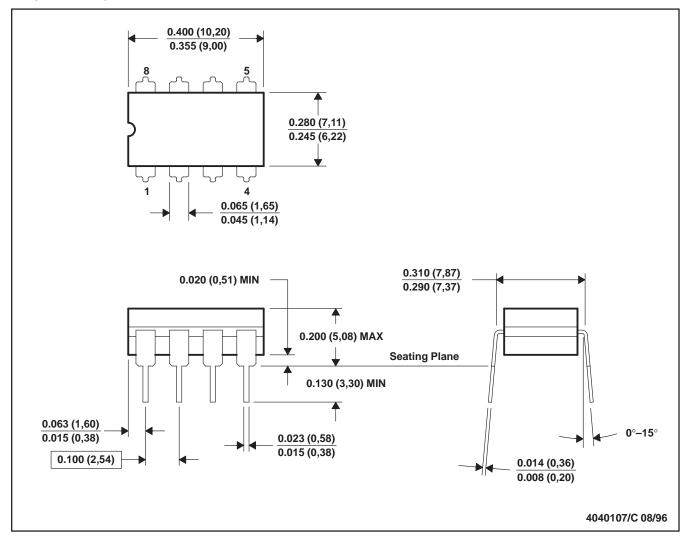

#### **MECHANICAL INFORMATION**

## JG (R-GDIP-T8)

#### **CERAMIC DUAL-IN-LINE PACKAGE**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL-STD-1835 GDIP1-T8

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated