# **APPLICATION NOTE**

# TEA2028 - TEA2029

By : J-M. MERVAL & B. D'HALLUIN

# SUMMARY

# Page

| <b>TEA202</b>                                                                                                   | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| I                                                                                                               | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                             |

| П                                                                                                               | MAIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                                                             |

| 111                                                                                                             | <b>PIN CONNECTION</b> (TEA2028B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                             |

| IV                                                                                                              | INTERNAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                             |

| v                                                                                                               | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                             |

| V.1                                                                                                             | INTERNAL VOLTAGE AND CURRENT REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                             |

| V.1.1<br>V.1.1.1<br>V.1.2                                                                                       | 1.26V Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6<br>6                                                        |

| V.1.2<br>V.2                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                             |

| v.2<br>V.2.1                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>7                                                        |

| V.2.1.1<br>V.2.2                                                                                                | Black Level Locking<br>Application<br>Memorizing the Sync Pulse 50% Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7<br>8                                                        |

| V.2.2.1                                                                                                         | Lc Ratio calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                             |

| V.2.3                                                                                                           | Sync Pulse Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                             |

| V.3                                                                                                             | FIRST PHASE LOCKED-LOOP STAGE "\01"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                             |

| V.3.1<br>V.3.2<br>V.3.2.1<br>V.3.2.2<br>V.3.2.3<br>V.3.2.4<br>V.3.3<br>V.3.3.1<br>V.3.3.2<br>V.3.3.2<br>V.3.3.3 | Phase Locked-loop "φ1" Block Diagram         Functional Duty of Individual Blocks         Phase comparator         Low-pass filter         VCO centered on 500kHz         Divider stage         Functional Description of Building Blocks         Phase comparator "φ1"         Low-pass filter         VCO (Voltage Controlled Oscillator)         a. 503kHz Ceramic Filter                                                                                                                                                                                      | 9<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>11<br>11<br>11 |

| V.3.4<br>V.3.5<br>V.3.5.1<br>V.3.6<br>V.3.6.1<br>V.3.6.2<br>V.3.7                                               | <ul> <li>b. Simplified Block Diagram of VCO .</li> <li>c. Characteristics of the External Filter .</li> <li>d. Study of the Internal Amplifier .</li> <li>e. Characteristics of the non-linear Amplifier "A4".</li> <li>f. Voltage-frequency transfer characteristics of VCO .</li> <li>"\phi1" Time Constant Switching .</li> <li>Video Identification Stage .</li> <li>Block diagram .</li> <li>Characteristics of Loop \phi1.</li> <li>Locking accuracy.</li> <li>Dynamic study.</li> <li>a. Long time constant .</li> <li>b. Short time constant .</li> </ul> | 12<br>13<br>14<br>14<br>15<br>15<br>15<br>16<br>16<br>17      |

| V.4                | LINE SAW-TOOTH GENERATOR                                       | 18       |

|--------------------|----------------------------------------------------------------|----------|

| V.5                | SECOND PHASE LOCKED LOOP "\p2"                                 | 19       |

| V.5.1              | Duty of Different Building Blocks.                             | 20       |

| V.5.1.1            | " <tr " %                                                      | 20       |

| V.5.1.2            | Low-pass filter                                                | 20       |

| V.5.1.3            | Phase modulator                                                | 20       |

| V.5.1.4            |                                                                | 20       |

| V.5.1.5            | Output stage                                                   | 20<br>20 |

| V.5.1.6<br>V.5.2   | Line deflection stage                                          | 20<br>20 |

| v.5.2<br>V.5.2.1   | Phase comparator "\overlag"                                    | 20       |

| V.5.2.1            | Low-pass filter f(p).                                          | 20       |

| V.5.2.3            | Phase modulator                                                | 21       |

| V.5.2.4            | Line flip-flop (TEA2028 only)                                  | 21       |

|                    | a. Block Diagram                                               | 22       |

|                    | b. T10 Calculation                                             | 22       |

|                    | c. 16ms Window                                                 | 22       |

|                    | d. Auto-set to "1"e. Maximum "T10" value as a function of "C1" | 22       |

|                    | e. Maximum "110" value as a function of "C1"                   | 22       |

| V.5.2.5            | Line output stage & inhibitions                                | 22       |

|                    | a. Inhibition at start-up.                                     | 23<br>23 |

|                    | b. Inhibition during line flybackcccccccc                      | 23<br>23 |

| V.5.2.6            | Line deflection stage                                          | 23       |

| V.5.3              | Characteristics of Loop "\overlage"                            | 25       |

| V.5.3.1            | Study of the static error                                      | 25       |

|                    | a. Phase shift error in case of no adjustment                  | 25       |

|                    | b. Study of shift adjustment                                   | 26       |

| V.6                | VERTICAL DEFLECTION DRIVER STAGE                               | 26       |

| V.6.1              | Frame Sync Extraction                                          | 27       |

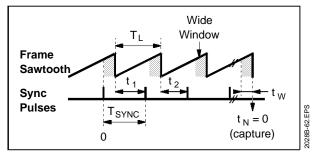

| V.6.2              | Frame Saw-tooth Generator.                                     | 27       |

| V.6.2.1            | 60Hz standard switching                                        | 28       |

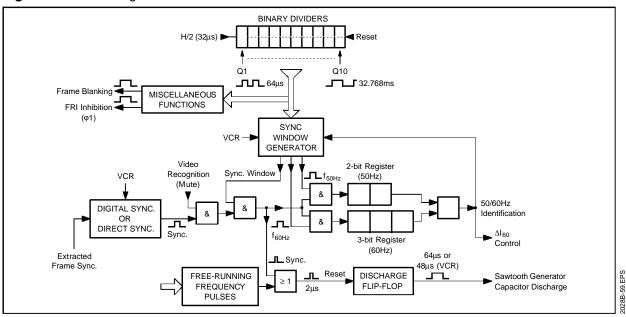

| V.6.3              | Functions of Frame Logic Block                                 | 28       |

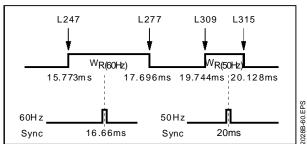

| V.6.3.1            | 50/60Hz standard recognition.                                  | 29       |

|                    | a. 50Hz Standard Recognition                                   | 29       |

| V C 2 2            | b. 60Hz Standard Recognition                                   | 29<br>29 |

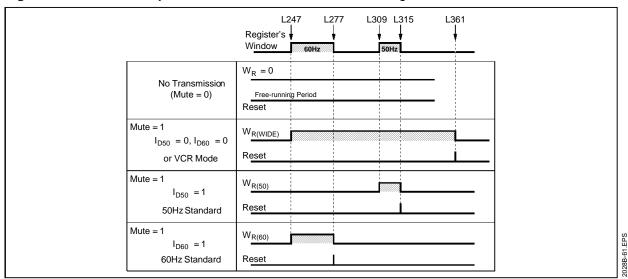

| V.6.3.2<br>V.6.3.3 | Vertical synchronization window - Free-running period          | 29<br>30 |

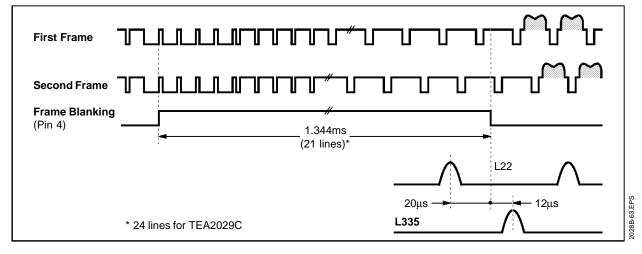

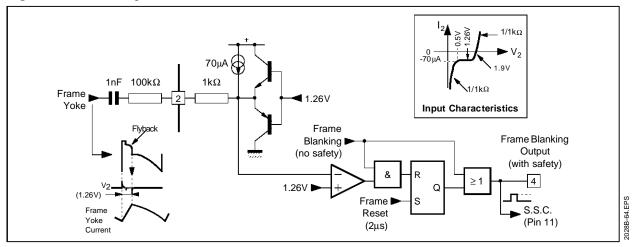

| V.6.3.4            | Frame blanking safety (TEA2028 only).                          | 30       |

|                    |                                                                |          |

| V.7                | SWITCHING POWER SUPPLY DRIVER STAGE                            | 31       |

| V.7.1              | Power Supply Block Diagram                                     | 31       |

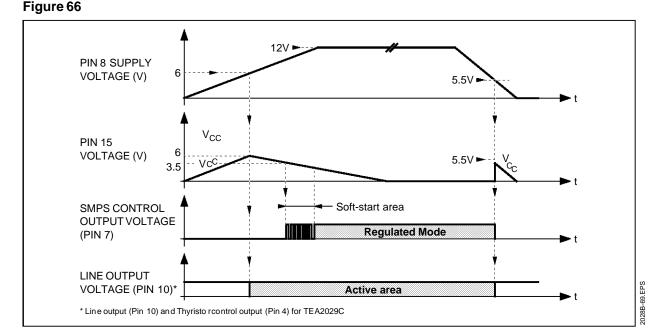

| V.7.2              | General Operating Principles                                   | 32       |

| V.7.3<br>V.7.4     | Electrical Characteristics of the Internal Regulation Loop     | 32<br>33 |

| V.7.5              | Protection Features.                                           | 34       |

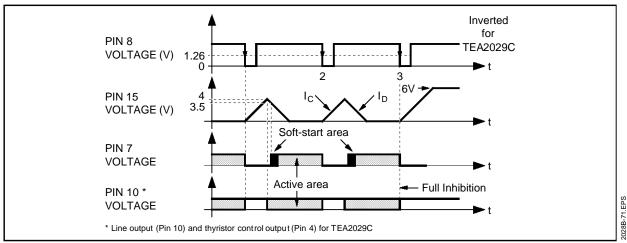

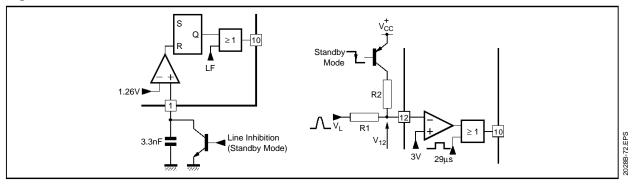

| V.7.6              | TV Power Supply in Standby Mode                                | 34       |

| V.7.6.1            | Regulation by primary controller circuit.                      | 34       |

| V.7.6.2            | Regulation by TEA2028                                          | 34       |

| V.8                | MISCELLANEOUS FUNCTIONS                                        | 35       |

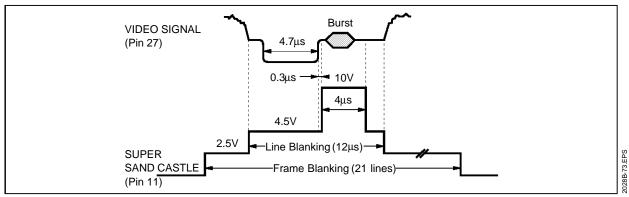

| V.8.1              | Super Sandcastle Signal Generator                              | 35       |

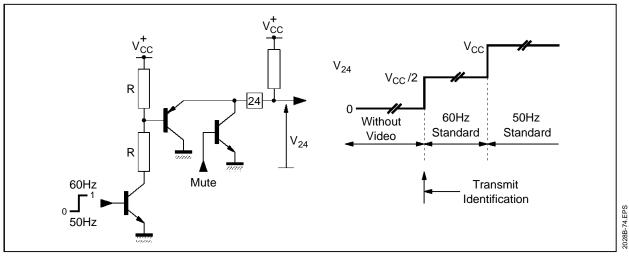

| V.8.2              | Video and 50/60HZ Standard Recognition Output                  | 35       |

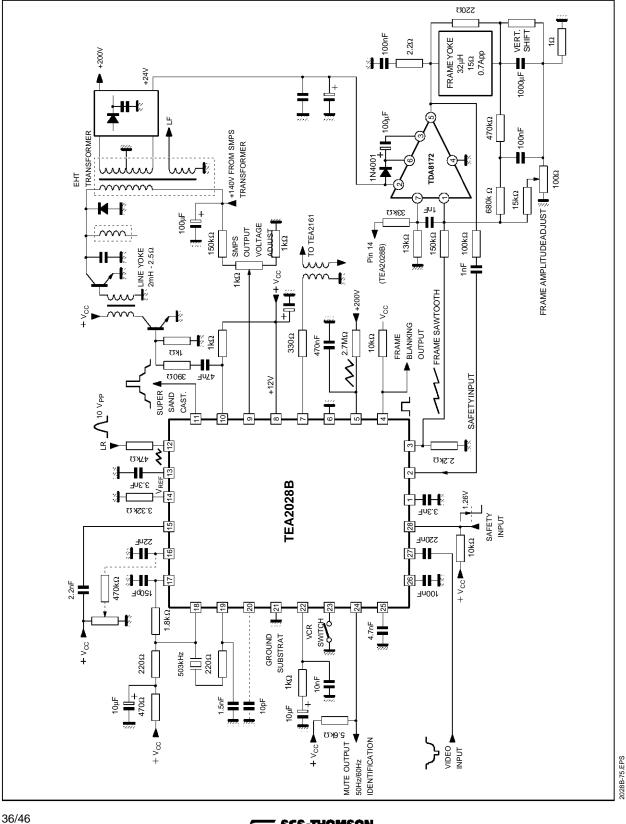

| VI                 | TEA2028 APPLICATION DIAGRAM                                    | 36       |

| V I                |                                                                | - 30     |

# **TEA2029**

| VII                                                                                  | TEA2029 : DIFFERENCES WITH TEA2028                                                                                                                                                                                                    | 37                                     |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VII.1                                                                                | GENERAL                                                                                                                                                                                                                               | 37                                     |

| VII.2                                                                                | PIN BY PIN DIFFERENCES                                                                                                                                                                                                                | 37                                     |

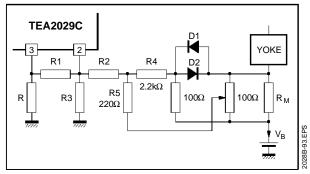

| VII.3                                                                                | TEA2029C PIN CONNEXTIONS                                                                                                                                                                                                              | 37                                     |

| VII.4                                                                                | FRAME PHASE MODULATOR                                                                                                                                                                                                                 | 37                                     |

| VII.5                                                                                | FRAME BLANKING SAFETY                                                                                                                                                                                                                 | 38                                     |

| VII.6                                                                                | ON-CHIP LINE FLIP-FLOP                                                                                                                                                                                                                | 39                                     |

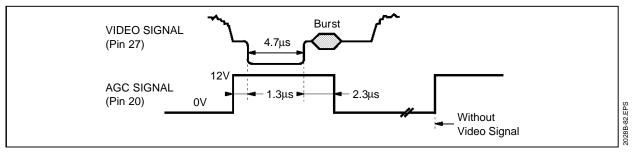

| VII.7                                                                                | AGC KEY PULSE                                                                                                                                                                                                                         | 40                                     |

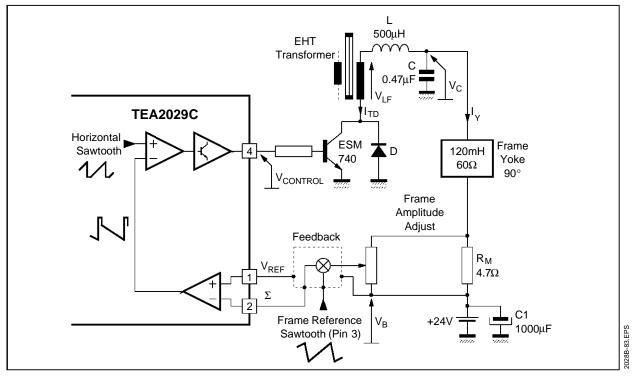

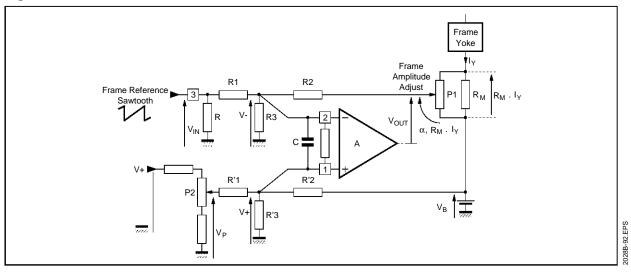

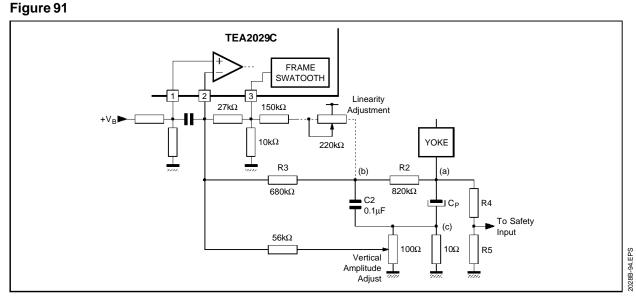

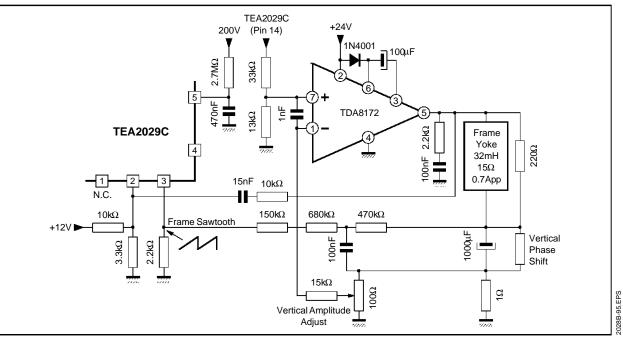

| VIII                                                                                 | APPLICATION INFORMATION ON FRAME SCANNING<br>IN SWITCHED MODE (TEA2029 ONLY)                                                                                                                                                          | 40                                     |

| VIII.1                                                                               | FUNDAMENTALS                                                                                                                                                                                                                          | 40                                     |

| VIII.2                                                                               | GENERAL DESCRIPTION                                                                                                                                                                                                                   | 40                                     |

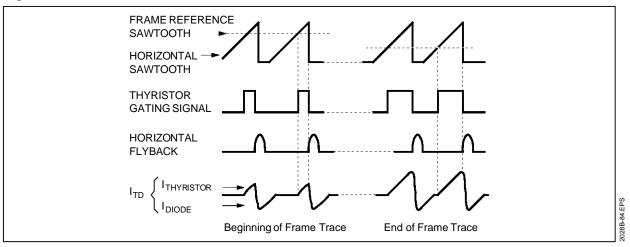

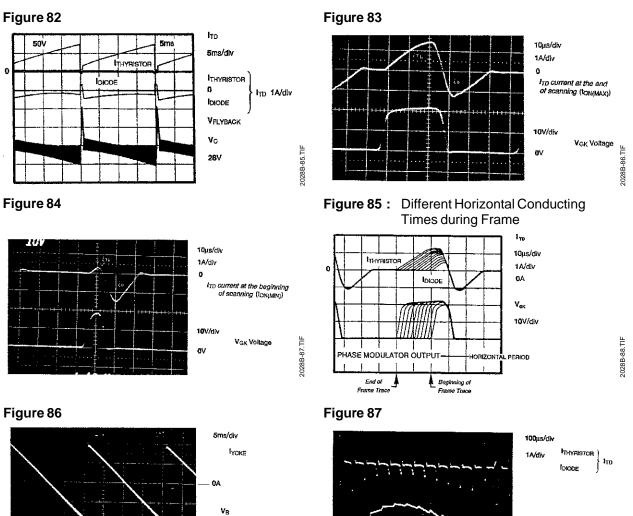

| VIII.3                                                                               | TYPICAL FRAME MODULATOR AND FRAME OUTPUT WAVEFORMS                                                                                                                                                                                    | 41                                     |

| VIII.4                                                                               | FRAME POWER STAGE WAVEFORMS                                                                                                                                                                                                           | 42                                     |

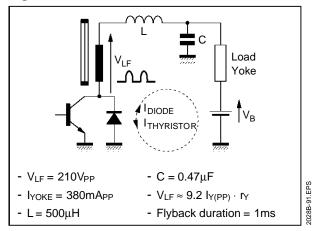

| VIII.5                                                                               | FRAME FLYBACK                                                                                                                                                                                                                         | 43                                     |

| VIII.6                                                                               | FEED-BACK CIRCUIT                                                                                                                                                                                                                     | 43                                     |

| VIII.6.1<br>VIII.6.1.1<br>VIII.6.1.2<br>VIII.6.1.3<br>VIII.6.2<br>VIII.6.3<br>VIII.7 | Influence of R3 value.         "S" Correction circuit in quasi-bridge configuration         Frame Scanning in Switched Mode using Coupling Capacitor         Frame Safety.         FRAME SCANNING IN CLASS B (WITH FLYBACK GENERATOR) | 43<br>43<br>43<br>44<br>44<br>45<br>45 |

| VIII.7.1                                                                             |                                                                                                                                                                                                                                       | 45                                     |

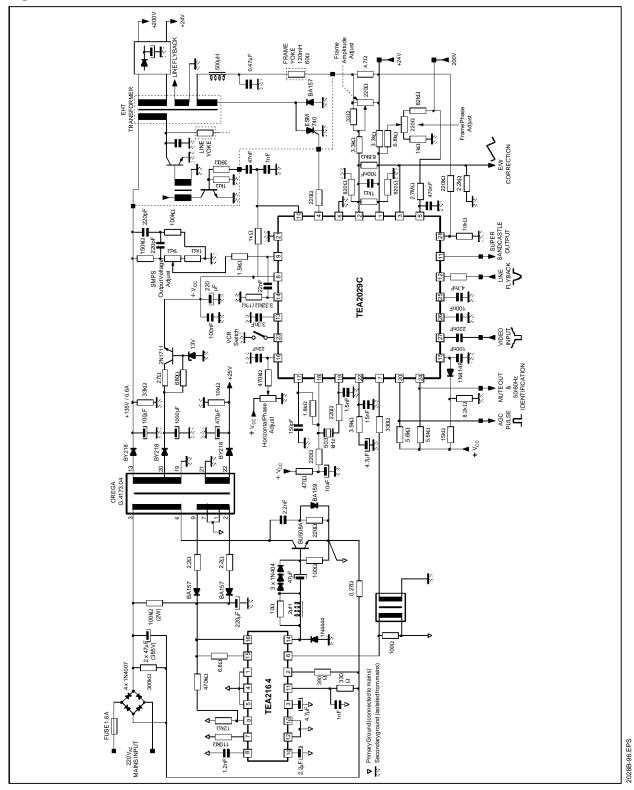

| IX                                                                                   | TEA2029 APPLICATION DIAGRAM COMPLETE APPLICATION WITH TEA2164                                                                                                                                                                         | 46                                     |

# I - GENERAL DESCRIPTION

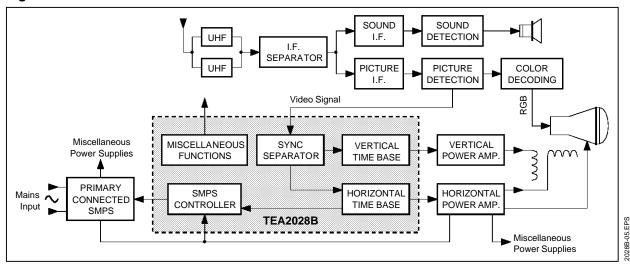

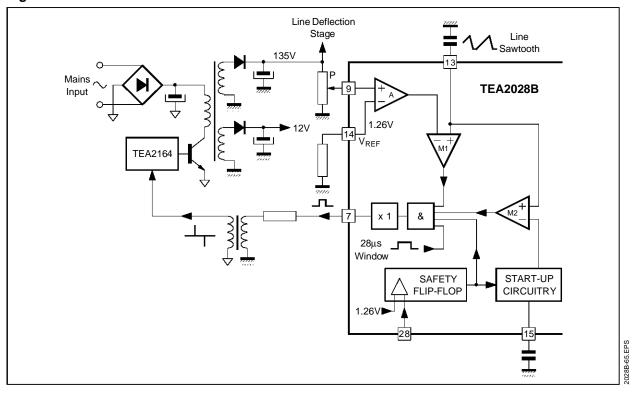

As depicted in Figure 1, the TEA2028 combines 3 major functions of a TV set as follows :

- Horizontal (line) and vertical (frame) time base generation for spot deviation. The video signal is used for the synchronization of both time bases.

- On-chip switching power supply controller synchronized on line frequency.

This integrated circuit has been implemented in bipolar  $I^2L$  technology, and various functions are digitally processed. In fact, resorting to logic functions has the advantage of working with pure and accurate signals while full benefit is drawn from high integration of logic gates (approx. 110 gates per mm<sup>2</sup>).

The main objective is to drive all functions using an accurate time base generated by a master 500kHz oscillator.

Also, horizontal and vertical time bases, are obtained by binary division of reference frequency. This has the advantage of eliminating the 2 adjustments which were necessary in former devices.

One section of this integrated circuit is designed to drive a switching power supply of recent implementation called "master-slave". Switching takes place on the primary side (i.e., directly on mains) of a transformer. The device ensures **SMPS Control**, **Start-up** and **Protection** functions. Control signals go through a small pulse transformer thereby providing full isolation from mains supply.

This new approach fully eliminates the bulky mains transformers used in the past. In addition, it offers optimized power consumption and reduction of TV cost-price.

# Figure 1

# **II - MAIN FUNCTIONS**

- Detection and extraction of line and frame synchronization pulses from the composite video signal.

- Horizontal scanning control and synchronization by two phase-locked loop devices.

- Video identification.

- 50 or 60Hz standard recognition for vertical scanning.

- Generation of a self-synchronized frame sawtooth for 50/60Hz standards.

- Line time constant switching for VCR operation through an input labeled "VCR" (Video Cassette Recorder).

- Control and regulation of a primary-connected switching power supply by on-chip controller device combining :

- an error amplifier

- a pulse width modulator synchronized on line frequency

- a start-up and protection system

- Overall TV set protection input

- Frame blanking and super sandcastle output signals

- Frame blanking safety input for CRT protection in case of vertical stage failure.

#### **III - PIN CONNECTIONS**

| Pin | Description                            |

|-----|----------------------------------------|

| 1   | Horizontal output monostable capacitor |

| 2   | Frame blanking safety input            |

| 3   | Frame saw-tooth output                 |

| 4   | Frame blanking output                  |

| 5   | Frame ramp generator                   |

| 6   | Power ground                           |

| Pin | Description                                                             |  |  |

|-----|-------------------------------------------------------------------------|--|--|

| 7   | SMPS control output                                                     |  |  |

| 8   | Supply voltage (V <sub>CC</sub> )                                       |  |  |

| 9   | SMPS regulation input                                                   |  |  |

| 10  | Horizontal output                                                       |  |  |

| 11  | Super-sandcastle output                                                 |  |  |

| 12  | Horizontal flyback input                                                |  |  |

| 13  | Horizontal saw-tooth generator                                          |  |  |

| 14  | Current reference                                                       |  |  |

| 15  | SMPS soft-start and safety time constant capacitor                      |  |  |

| 16  |                                                                         |  |  |

| 17  | V <sub>CO</sub> phase shift network                                     |  |  |

| 18  | V <sub>CO</sub> output                                                  |  |  |

| 19  | V <sub>CO</sub> input                                                   |  |  |

| 20  | Frame sync time constant adjustment capacitor                           |  |  |

| 21  | Substrate Ground                                                        |  |  |

| 22  | \$\$\phi\$1 phase comparator capacitor                                  |  |  |

| 23  | VCR switching input                                                     |  |  |

| 24  | Video and 50/60Hz identification output (Mute)                          |  |  |

| 25  | Video identification capacitor                                          |  |  |

| 26  | Horizontal sync detection capacitor<br>(50% of peak to peak sync level) |  |  |

| 27  | Video input                                                             |  |  |

| 28  | Safety input                                                            |  |  |

#### Package: DIP28

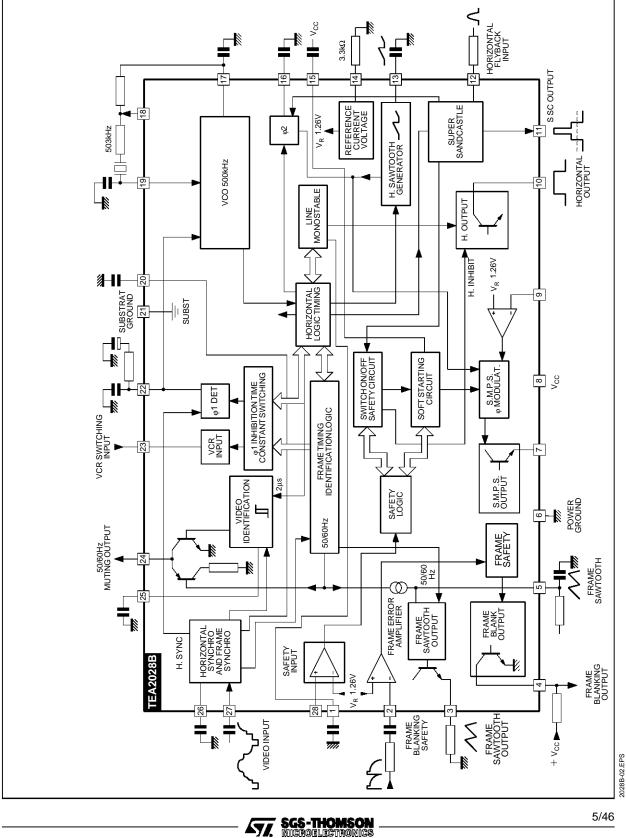

# **IV - INTERNAL BLOCK DIAGRAM**

# Figure 2

5/46

# **V** - FUNCTIONAL DESCRIPTION

Majority of the on-chip analog functions were computer simulated and results such as temperature variation, technological characteristic dispersion and stability, have led to the enhancement and implementation of actually employed structures. A parallel in-depth study of the device implemented in form of integrated sub-sections is provided to analyze the overall performance in a TV set.

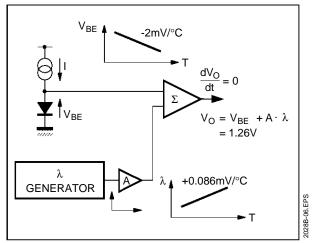

# V.1 - Internal Voltage and Current References V.1.1 - 1.26V Voltage reference

For optimum operation of the device, an accurate and temperature-stable voltage generator independent from  $V_{CC}$  variations is used (Band-gap type generator).

The generated 1.26V is particularly used as reference setting on input comparators.

#### V.1.1.1 - Generator block diagram

## Figure 3

with

$$\lambda = \frac{K \cdot T}{q} = 25.7 \text{mV} \text{ at } + 25^{\circ}\text{C}$$

$\frac{d\lambda}{dT} = \frac{K}{q} = + 0.086 \text{mV/}^{\circ}\text{C}$

$\frac{dV_{BE}}{dT} = \frac{V_{BE(25)} - 1.26}{T} = -2 \text{mV/}^{\circ}\text{C}$

if  $A\lambda = 1.26 - V_{BE}$

Then :  $V_{O} = 1.26\text{V}$  (temperature-independent)

In practice, maximum drift due to temperature can be + 0.23mV/°C i.e.,  $\pm$  1.5% for a  $\Delta T$  of 80°C.

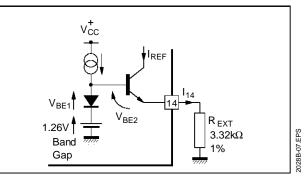

# V.1.2 - Current reference

This is implemented using the 1.26V generator in combination with an external resistor.

#### Figure 4

Thus, it follows that  $I_{\text{REF}}$  is accurate and independent of both  $V_{\text{CC}}$  and temperature.

A set of current generators proportional to I<sub>REF</sub> current are used in various circuit blocks.

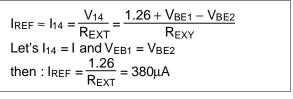

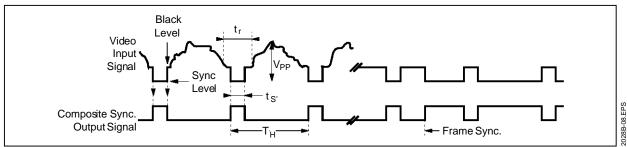

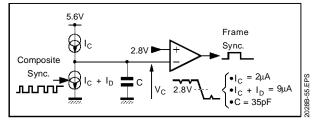

#### V.2 - Line Sync. Extraction

Horizontal and vertical time bases should be synchronized with corresponding sync. pulses transmitted inside the infra-black portion of video signal. The duty of this stage is to extract these sync pulses. The output signal, called composite sync, contains the vertical sync which is transmitted by simple inversion of line sync. pulses.

The vertical sync pulse is then extracted from this composite signal.

The main advantage of this arrangement is its ability to operate at video input signal levels falling within 0.2V to 3V peak-to-peak range and at any average value.

The operating principle is to lock the black level of the input signal (Pin 27) onto internaly fixed voltage ( $V_N$ ) and then memorize the average voltage of the sync pulse by using an integrating capacitor connected to Pin 26.

Finally, the composite sync signal is delivered by a comparator the inputs of which are driven by  $V_{50\%}$  and video signals.

# Figure 5

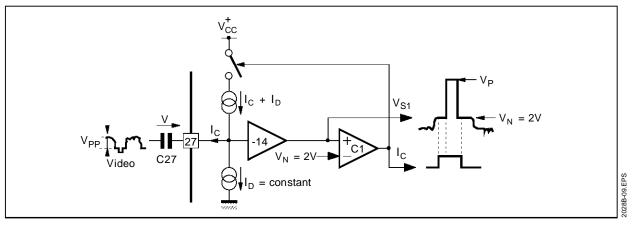

# V.2.1 - Black level locking

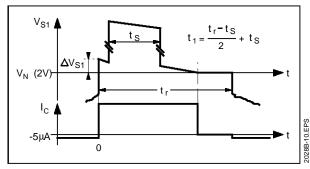

#### Figure 6

The video signal is applied to Pin 27 through the coupling capacitor "C27". Since the sync pulse amplitude is generally equal to 1/3 of V<sub>PP</sub> (i.e. 66mV to 1V) and in order to obtain a good precision of the black level, the sync pulse should be amplified by a coefficient of - 14 before being applied to the comparator "C1".

This comparator will charge the "C27" capacitor as long as  $V_{S1} > V_N \cdot V_{S1}$  will stabilize at  $V_N$  during the line flyback interval "T<sub>r</sub>" if the average charge of "C27" capacitor is nil for one T<sub>H</sub> period.

$I_C/I_D$  is calculated such that the locking occurs at the middle of the back porch.

# Figure 7

The  $\Delta V_{S1}$  produced by  $I_D$  during the line trace which is :  $14 \cdot \frac{I_D \cdot t_A}{C27}$

must be equal to  $\Delta V_{S1}$  during the time interval "t1", i.e. : 14  $\cdot \frac{I_C \cdot t_1}{C27}$

It follows that :

$$\frac{I_C}{I_D} = \frac{t_A}{t_1} = \frac{T_H - t_R}{t_S + \frac{t_R - t_S}{2}}$$

substituting  $T_H = 64 \,\mu s$ ,  $t_r = 12 \,\mu s$ ,  $t_S = 4.7 \,\mu s$  (which are standard and constant values) into above

equation :

$$\frac{IC}{I_D} = 6.23V$$

# V.2.1.1 - Application

At I<sub>C</sub> =

$$5\mu A \Rightarrow$$

I<sub>D</sub> =  $31\mu A$

- With C27 = 220nF,  $\Delta V_S$  will be

$14 \cdot \frac{5 \cdot 52}{220} = 16mV$

which yields 0.8% maximum error in black level with respect to  $V_{\text{N}}$  = 2V at the beginning of retrace time

- Due to transposition on amplifier stage, the black level voltage on Pin 27 is equal to 2V.

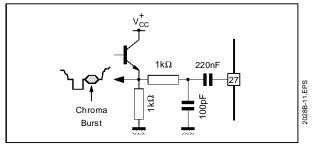

In practice, at low amplitude video signals, it is recommended to insert a low-pass filter before the "C27" capacitor so as to attenuate the chrominance sub-carrier and the noise components. The aim is to reduce the phase variations of the detected sync pulse and thus enhance the horizontal scanning stability.

#### Figure 8

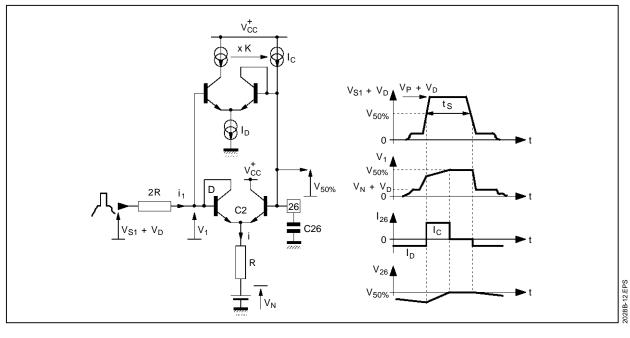

#### V.2.2 - Memorizing the sync pulse 50% value

The objective is to memorize the voltage corresponding to 50% of the line sync pulse  $V_{S1}$  by using an external capacitor connected to Pin 26 (see Figure 9).

The overall arrangement comprises two comparators.

- Comparator C2 : delivers an output voltage "V1" by comparing  $V_{S1}$  +  $V_D$ ,  $V_{26}$  and the voltage drop across two resistors.

- Comparator C3 : which delivers a constant output current thereby maintaining on capacitor "C26", the voltage  $V_{50\%}$  corresponding to 50% of peak to peak sync pulse.

#### Figure 9

During the line scanning, diode "D" is reverse biased :  $V_{S1} + V_D = V_1 < V_{26}$  and C3 will deliver a current  $I_D$  which will discharge the capacitor.

During sync pulse interval,  $V_{S1} + V_D = V_P + V_{D,}$ diode "D" begins conducting and thus :

$V_1 = (V_P + V_D) - (2 \text{ R i}_1)$ . Since the capacitor has been slightly discharged  $\Rightarrow V_1 > V_{26}$ , comparator C3 begins charging the capacitor until C2 is brought to equilibrium.

At this time,

$$I_1 = \frac{i}{2}$$

where  $i = \frac{V_{26} - V_D - V_N}{R}$

thus  $V_1 = V_P + V_D = 2 \frac{i}{2} = V_P + V_N + 2 V_D - V_{26}$

and  $V_1 = V_{26} \Leftrightarrow V_{26} = \frac{V_P + V_N}{2} + V_D = V_{50\%}$

A high value C26 capacitor will thus memorize the voltage level corresponding to 50% of the line sync. pulse.

# V.2.2.1 - $\frac{l_c}{l_D}$ Ratio calculation

During the line scanning period ( $T_H$  -  $T_S$ ), the capacitor C26 will loose a charge equivalent to :  $I_D$  ( $T_H$  -  $T_S$ ).

This energy must be recovered before the end of sync pulse such that :  $I_C \cdot t_S > I_D (T_H - T_S)$

therefore

$$\frac{I_C}{I_D} > \frac{I_H - t_S}{t_S}$$

$\frac{I_C}{I_D} > 12.6$

In practice, for C26 = 100nF,  $I_D$  = 25µA and  $I_C$  = 800µA.

SGS-THOMSON

MICROELEC

<u>ک</u>

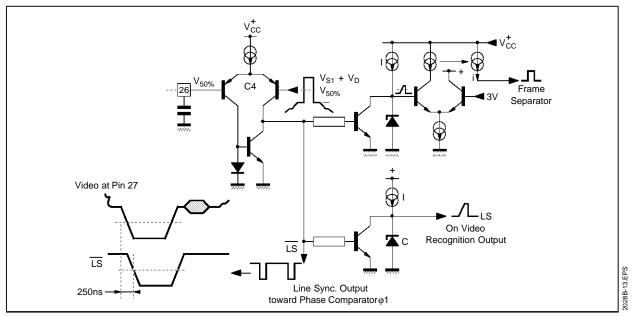

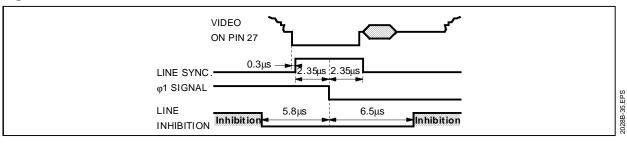

# V.2.3 - Sync pulse detection

This function is fulfilled by comparing the inverted video signal ( $V_{S1} + V_D$ ) whose black level is constant at 2V, with the sync 50% voltage level on Pin 26 (see Figure 10).

Comparator C4 will deliver the line sync pulse (LS) which will be used for 3 functions :

- Horizontal scanning frequency locking : output to  $\varphi 1$  phase comparator.

- Frame sync extraction for vertical scanning synchronization.

- Detecting the presence of a video signal at circuit input.

The LS signal in two latter functions is filtered for noise by using combination of current generator I and a zener diode equivalent to a capacitor.

Using this extraction technique at a very noisy video signal yields remarkable display stability.

#### Figure 10

The device also provides for scanning synchronization at aerial signal attenuation of approximately 75dB, i.e. 15 to 20dB better than other sync processors.

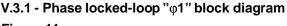

#### V.3 - First Phase Locked-loop Stage "q1"

This stage is commonly called the first Phase Locked-Loop " $\phi$ 1".

Its duty is to lock the frequency and the phase of the horizontal time base with respect to the line sync signal.

In the absence of transmission (i.e. lack of line sync), the horizontal scanning frequency is obtained by dividing the output frequency of a VCO device. This VCO oscillates at approximately 500kHz and uses a low frequency drift ceramic resonator. This method eliminates the need of horizontal frequency adjustment.

SGS-THOMSON

# V.3.2 - Functional duty of individual blocks V.3.2.1 - Phase comparator

The duty of this comparator is to issue an output current proportional to the phase difference between  $\phi_{\text{IN}}$  and  $\phi_{\text{OUT}}$ .

# V.3.2.2 - Low-pass filter

This filter suppresses the parasitic component containing the sum of phases, smoothens the phase difference component and determines the timing characteristics of the loop.

# V.3.2.3 - VCO centered on 500kHz

This is a voltage-controlled oscillator which generates an output frequency proportional to the voltage applied to its input.

This voltage is delivered by low-pass filter.

# V.3.2.4 - Divider stage

It is used to divide the VCO frequency (500kHz) by 32 so that it can be compared with the line sync signal frequency of 15625Hz.

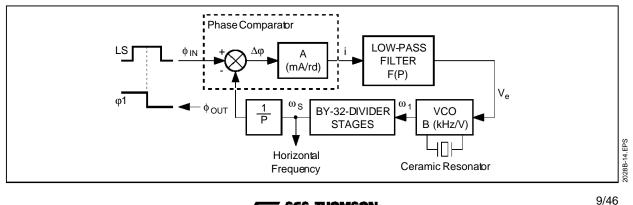

#### V.3.3 - Functional description of building blocks V.3.3.1 - Phase comparator "\ohned1"

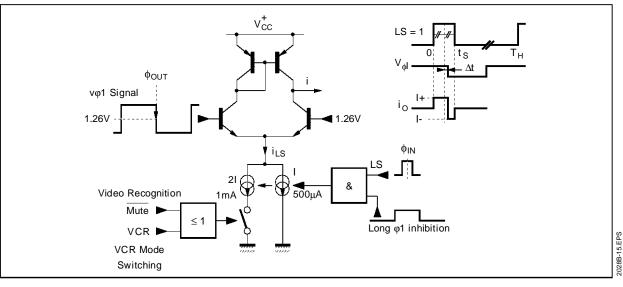

The comparator is functionally equivalent to a signal multiplier (see Figure 12).

Let's assume that :

-  $i_{LS}$  = I sin ( $\omega_{H}t$  +  $\phi_{IN})$  and  $V_{\varphi 1}$  = k cos ( $\omega_{H}t$  +  $\phi_{OUT})$  then :

- i =  $\frac{i_{LS} \cdot k}{2}$  [sin ( $\Phi_{IN} - \Phi_{OUT}$ ) + sin ( $2\omega_{H}t + \Phi_{IN} + \Phi_{OUT}$ )] (see Figure 13)

- the low-pass filter will suppress the 2fH frequency

# component

- $\phi_{\text{IN}}$   $\phi_{\text{OUT}}$  difference being low : sin ( $\phi_{\text{IN}}$  -  $\phi_{\text{OUT}}$ )  $\approx \phi_{\text{IN}}$  -  $\phi_{\text{OUT}}$

- the output current will be therefore proportional to the phase difference between the signals compared.

In other words, the average current over one period is :

$$I_{AV} \cdot T_{H} = I\left(\frac{t_{S}}{2} + \Delta t\right) - I\left(\frac{t_{S}}{2} - \Delta t\right) = 2I \Delta t$$

$$I_{AV} = 2I \frac{\Delta t}{T_{H}} \text{ and } \Delta t = \Delta \Phi \frac{T_{H}}{2\pi}$$

The comparator conversion gain is thus :

$$A = \frac{I}{\Delta \Phi} = \frac{I}{\pi} \text{ (in A/rd)}$$

Later in our discussion we shall consider the two possible values of the current I.

For the time being, let's define these values as follows :

- I =  $500\mu A$  for "long time constant" or normal operation

- I = 1.5mA for "short time constant" VCR mode or synchronization search (Mute).

The values of A are therefore :

- $A_{LONG} = 0.16 mA/rd$

- $A_{SHORT} = 0.47 \text{mA/rd}$

Use of comparator inhibition signal is quite useful under noisy transmission conditions. It eliminates risk of incorrect comparison during the line scanning phase which would be due to the noise present on LS signal. Horizontal phase and image stability are thus highly enhanced.

Characteristics of this inhibition signal will be discussed at the end of this chapter.

#### Figure 13

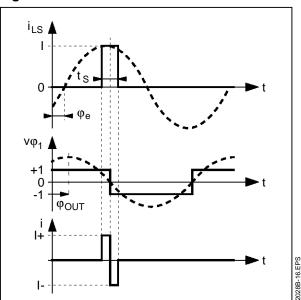

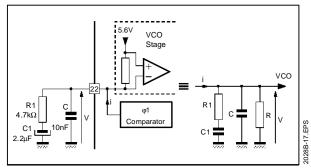

# V.3.3.2 - Low-pass filter (see Figure 14)

Its main function is to reject the  $2f_{\text{H}}$  (31kHz) frequency component delivered by the phase comparator.

It also defines the characteristics of the loop in transient mode.

The filter is built around two sub-sections which determine the stability and the response time of the loop in the following modes of transmission :

Normal or VCR modes. See section V.3.6 "Dynamic study of  $\phi$ 1".

### Figure 14

R is the dynamic input resistance of the VCO.

The filter transfer function may be defined as follows :

$$- f(p) = \frac{V}{i} = Z(p)$$

$$= \frac{Z(p)}{i} = \frac{P}{i}$$

$$2(p) - R$$

1 + p (R C + R1 C1 + R C1) + R R1 C C1 p<sup>2</sup>

The second order terms of the denominator can be converted to first order products as a function of

1 + R1 C1 p

frequency as follow :

$$f(jf) = R \frac{1 + j \frac{f}{f1}}{\left(1 + j \frac{f}{f2}\right)\left(1 + j \frac{f}{f3}\right)}$$

with R1 = 4.7kΩ, R = 500kΩ, C1 = 2.2µF, C = 10nF

we obtain :

- f1 =  $\frac{1}{2\pi R1 C1}$  = 15.4Hz

- f2 =  $\frac{1}{2\pi (R C1 + R C + R1 C1)}$  = 0.14Hz

- f3 = 3.43kHz

**TEA2028 - TEA2029 APPLICATION NOTE**

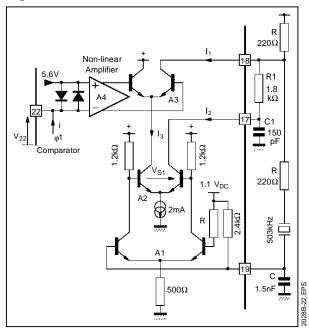

#### V.3.3.3 - VCO (Voltage Controlled Oscillator)

Its function is to generate a frequency proportional to a control voltage issued externally, by the lowpass filter in our case.

The period of the output signal is used as timing reference for various functions such as, horizontal and vertical time bases. The frequency range must be short and accurate :

- It must be short since the power dissipated within the horizontal scanning block is inversely proportional to the line frequency.

- The accuracy is required if the adjustment is to be omitted.

The basic arrangement is to employ a ceramic resonator (or ceramic filter) which has quite stable characteristics as a function of frequency.

A filter whose resonating frequency is a multiple of line frequency (15625Hz) is to be selected. An example is  $32 \cdot 15625 = 500$ kHz.

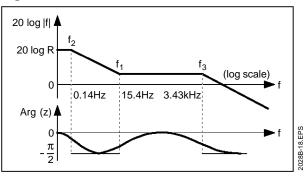

#### A. 503kHz CERAMIC FILTER

Where :

R1 =  $7\Omega$ , L1 = 1.26mH, C1 = 78pF, C0 = 507pF - Series resonance frequency :

$$f_{S} = \frac{1}{2\pi \sqrt{L1 C1}} = 503 \text{kHz}$$

Parallel resonance frequency :

$$f_{P} = f_{S} \cdot \sqrt{1 + \frac{C1}{C0}} = 540 \text{kHz}$$

- Tolerance within the resonance area :  $503 \text{kHz} \pm 0.3~\%$

- Temperature stability :  $\pm 0.3\%$  of f<sub>O</sub> at  $\Delta T = 100^{\circ}C$

# Figure 18

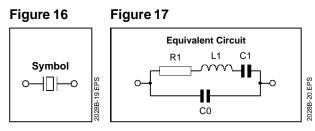

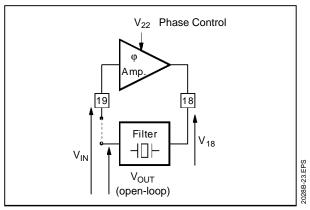

B - SIMPLIFIED BLOCK DIAGRAM OF VCO

#### Figure 19

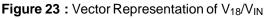

The overall arrangement is equivalent to a variablephase amplifier configured in closed loop with the external passive filter.

The system will oscillate if the open-loop gain is 0dB and if  $V_{OUT}$  leads  $V_{IN}$ .

In closed-loop oscillating mode, the phase variation of  $V_{18}/V_{IN}$  imposed by  $V_{22}$  will result in same  $V_{OUT}/V_{18}$  variation but of opposite sign.

This phase change will finally correspond to a change in frequency.

# Figure 20

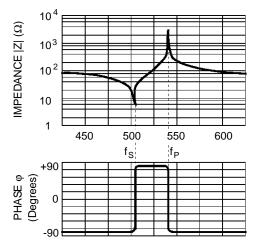

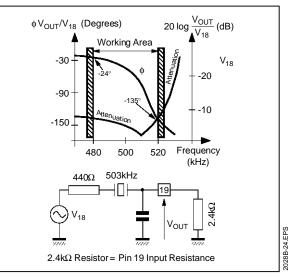

# C. - CHARACTERISTICS OF THE EXTERNAL FILTER

The ceramic resonator behaves as a capacitor at  $f < f_S$  ( $f_S$ : series resonance frequency) and as an inductor at frequencies falling between its two resonance frequencies.

Combined with a "R.C" network to generate a  $90^{\circ}$  phase lag, the overall arrangement will exhibit the following characteristics : see Figure 21

# Figure 21

2028B-21.EPS

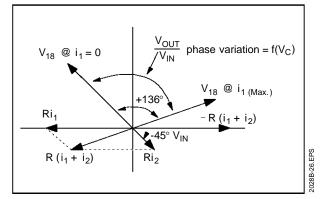

Thus, a variable  $(24^{\circ} \text{ to} + 135^{\circ})$  phase lead with a gain higher than 10dB, must be implemented onchip so as to enable the system to enter into oscillation.

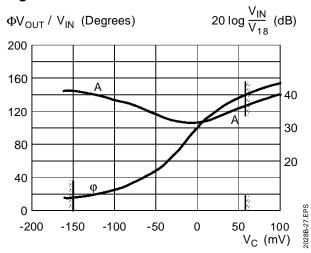

The frequency dead points correspond to the maximum internal phase variations. This phase shift is controlled by voltage V<sub>22</sub> whose value of  $5.6V \pm 0.7$  is determined by two diodes.

From the Figure 21, the non-linearity of phase-frequency characteristics is clearly apparent. If linear voltage-frequency response is required for a symmetrical gain of  $\phi$ 1 loop, it would then be necessary to implement a non-linearity, on the phase control amplifier A4, but in the opposite direction.

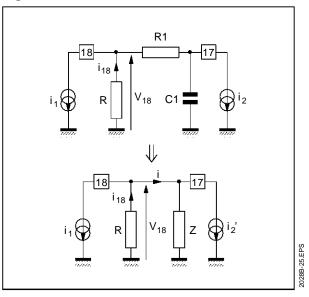

# D. - STUDY OF THE INTERNAL AMPLIFIER

Let's study the gain and phase response of  $\frac{V_{18}}{V_{1N}}$  as

a function of V<sub>22</sub>.

$V_{22} = \frac{V_C}{K}$  where K is a non-linear coefficient

To start with, the "Vc" voltage of comparator "A3" is taken as reference parameter.

The dynamic representation of the output stage can be depicted as below (Figure 22).

with :

$$l_2' = \frac{l_2}{1 + j\omega R1 C1}$$

(at f = 500kHz)

R1 C1  $\omega$  = 1  $\Rightarrow$   $i_2' = \frac{i_2}{1 + j}$

and Z = R1 +  $\frac{1}{j\omega C} << R \Leftrightarrow i \approx i_2'$

R1C1 network produces -45° phase lag of "i" with respect to "i2", around 500kHz.

$V_{18} \approx - R \cdot (i_1 + I_2')$

$i_1$  and  $i_2$  calculation as a function of "V<sub>IN</sub>" on Pin 19

1

- A1 Amplifier :

$$\frac{VS1}{V_{IN}} = \frac{KC}{dr_1} = \frac{1200}{57} = 2$$

dr : dynamic resistance =  $\frac{\lambda}{I}$

- A2 Amplifier

$$\frac{i_2}{V_{S2}} = \frac{1}{2dr_2} = \frac{1}{54} \Leftrightarrow \frac{i_2}{V_{IN}} = \frac{V_{S1}}{V_{IN}} \cdot \frac{i_2}{V_{S1}} = 0.395$$

$$\Rightarrow i_2 = 0.39 V_{IN}, i_2 \text{ is in phase with } V_{IN} \text{ therefore } :$$

$$i_3 = -i_2 = -0.39 V_{IN}$$

$$i_{1} = i_{3} \left( \frac{-V_{C}}{A\lambda} + \frac{1}{2} \right) = -0.39 V_{IN} \left( \frac{-V_{C}}{A\lambda} + \frac{1}{2} \right)$$

"V<sub>IN</sub>" always leads the "i<sub>1</sub>" by 180, only the amplitude of  $i_1$  is a function of V<sub>C</sub> (see Figure 23).

$$-\frac{V_{OUT}}{V_{IN}} = -R\frac{I_{1}(1+j)R_{1}C_{1}\omega) + I_{2}}{1+j(R_{1}+R)C_{1}\omega}$$

- i1 = -0.39 VIN  $\left(\frac{i}{2} - \frac{V_{C}}{4\lambda}\right)$  and i2 = 0.39 VIN

The Figure 24 illustrates the characteristics of  $V_{18}/V_{IN}$  phase versus  $V_C.$

- Phase variation determined by  $V_C$  falls between +24° and +135° range

- The gain is higher than 10dB. The Pin 18 output signal of 30 to 40dB has a rectangular component (see Figure 24).

#### Figure 24

# E - CHARACTERISTICS OF THE NON-LINEAR AMPLIFIER "A4" (see Figures 25 and 26)

This is a differential amplifier whose equivalent feed-back resistors of emitters vary as a function of its input voltage.

The maximum output voltage swing is set by two "clamp" diodes connected to "V $_{22}$ " input.

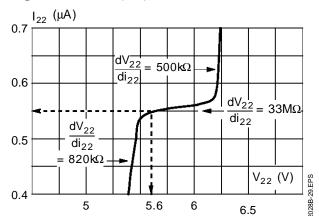

#### F - VOLTAGE-FREQUENCY TRANSFER CHARACTERISTICS OF V<sub>CO</sub> (see Figure 27)

The transfer characteristic is linear and centered at 5.6V at 500kHz operating frequency.

$T_{\text{transfer}} = \frac{\Delta f}{\Delta V} = 22.4 \text{kH/Vz}$  and once it goes through

five divide-by-two stages :  $T = \frac{22.4}{32} = 0.7 \text{ kHz/V}$

**Figure 26 :**  $I_{22} = F(V_{22})$

# V. 3.4. - "\ohngot1" Time constant switching

When switching between stations or receiving signal via a VCR, the loop locking interval must be as short as possible so as to avoid unwanted visible effect on the picture. In fact, since the synchronization between the VCR motor drive and the playback head is rather imperfect, it will produce frequency and phase fluctuations in the output composite video signal. Under these conditions, phase locking interval must be "short" (VCR Mode).

In the case of broadcast transmission, this loop must also filter all phase variations produced by noisy sync signal. In this case, its locking time constant must be "long" (normal mode).

In other "jungle" circuits, this time constant switching is carried out by capacitor switching within the filter loop. In our case, this function is achieved by changing the current amplitude of the phase comparator.

This amplitude changing modifies the open-loop system gain and therefore the damping coefficient and the locking time constant.

The device will be in short time constant mode under the following two conditions :

- VCR Mode or SCART Connector Mode : This mode is enabled by a low state on Pin 23.  $V_{23} < 2.1V$ .

- Transmitter search and tunning. In order to accelerate the capture, a "Video Identification" stage will detect the presence or the absence of a video signal on input Pin 27, and deliver accordingly a signal called "Mute".

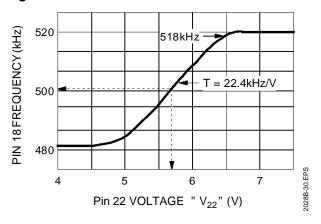

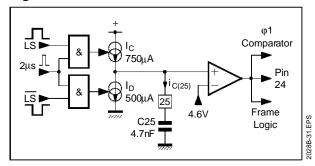

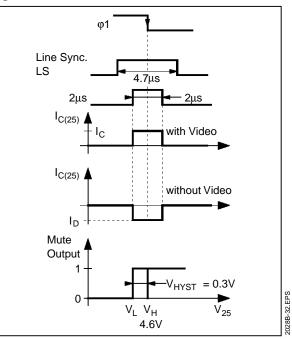

# V.3.5 - Video identification stage

This stage will detect the coincidence between the line sync pulse (if present) and a  $2\mu$ s pulse issued from the logic block. This  $2\mu$ s pulse at line frequency is positionned at the center of line sync pulse when the first loop " $\phi$ 1" is locked.

This sampled detection is stored by an external capacitor connected to Pin 25. The video recognition status is also available on Pin 24 so as to enable Sound Muting during station search process and the inhibition of Automatic Frequency Tuning.

# V.3.5.1 - Block diagram

#### Figure 28

The video recognition signal is delivered by a hysteresis comparator.

The recognition time "T\_R" is adjustable by an external capacitor, as soon as  $\phi 1$  is locked :

$$-I_{C25(AV)} = I_C \cdot \frac{2\mu s}{64\mu s}$$

and :

-

$$T_R = C25 \cdot \frac{V_H}{I_{C25(AV)}} = 1.96 \cdot 10^5 \cdot C25$$

with C25 = 4.7nF  $\Rightarrow$  T<sub>R</sub> = 1ms

(which is clearly quite fast)

#### Figure 29

# V.3.6 - Characteristics of loop $\varphi 1$ V.3.6.1 - Locking accuracy

Let's study the phase error  $"\phi_{OUT}$  -  $\phi_{IN}"$  under steady state conditions :

The open-loop gain is :

$$- T(p) = \frac{AB f(p)}{f}$$

Where :

$A = 0.16 \text{mA/rd} \text{ (long time constant)}$

$A = 0.47 \text{mA/rd} \text{ (short time constant)}$

$B = 0.7 \text{kHz/V or } B = 4.4 \ 10^3 \text{rd/s}$

$- f(p) = R \cdot \frac{1 + \tau_1 p}{(1 + \tau_2 p) (1 + \tau_3 p)}$

Where : R = Dynamic input resistance of VCO.

If a phase step of  $\Delta \phi$  is applied to the input, the following would be obtained as a function of (p) :

$$\Phi_{IN}(p) = \frac{\Delta \Phi}{p}$$

Using the last value theorem : lim  $f(t) = \lim p \cdot f(p)$ Let's calculate lim  $(\phi_{IN} - \phi_{OUT})$

- The closed-loop gain is :

$$-H(p) = \frac{T(p)}{1+T(p)} = \frac{ABf(p)}{p+ABf(p)} = \frac{\Phi_{OUT(p)}}{\Phi_{IN(p)}}$$

that is :

$$\lim_{p \to 0} p (\Phi_{IN} - \Phi_{OUT}) = \lim_{p \to 0} \frac{p \Delta \Phi}{p + AB f(0)} \to 0$$

It is therefore deduced that the system can follow all input phase variations without producing any static error.

In practice, there will be a slight error due to the input bias current "I<sub>B</sub>" of VCO, which is  $0.55\mu$ A at f<sub>O</sub> = 500kHz. This DC current is delivered by a phase comparator which will generate a phase error of :

- long time constant :

$$\Delta \Phi_{\text{LONG}} = \frac{I_{\text{B}}}{A_{\text{LONG}}} = 0.55 \cdot \frac{10^{-3}}{0.16}$$

= 3.4 \cdot 10^{-3} rd or 35ns in \Delta t

- short time constant :  $\Delta \Phi_{SHORT} = \frac{I_B}{A_{SHORT}} = 12ns$

These two errors cause a horizontal picture displacement. On a large screen of 54cm wide, this will be :  $64 - 12 = 52\mu s$ , which for both modes corresponds to a shift of :

$$\Delta_{\text{LINE}} = \frac{\Delta \Phi_{\text{LONG}} - \Delta \Phi_{\text{SHORT}}}{52} \cdot 520 = 0.24 \text{mm}$$

It is obvious that such displacement can be fully neglected.

#### **Response to a Frequency Step**

- The input phase is :  $\Phi_{IN}(t) = \Delta \omega t$

- which as a function of (p) is :  $\Phi_{IN}(p) = \frac{\Delta \omega}{p^2}$

- The accuracy is :

$$\lim_{p \to 0} (\Phi_{IN} - \Phi_{OUT}) = \lim_{p \to 0} \frac{\Delta \omega}{p + ABf(o)} = \frac{\Delta \omega}{ABR}$$

where R = 500kΩ at f(o)

In this case, the phase error depends on both, the magnitude of the frequency step and the static gain ABR.

In general,  $\frac{\Delta f}{\Delta f}$  which is the open-loop static gain, is taken into consideration.

$$\frac{\Delta \omega}{\Delta \Phi} = ABR = \frac{2\pi\Delta f}{\Delta t \times 2\pi} = A \cdot 2\pi \cdot B' \cdot R$$

$$\Rightarrow \frac{\Delta f}{\Delta t} = AB'R \cdot \frac{2\pi}{T_{H}} (B' \text{ in } kHz/V)$$

$$- \text{ In normal mode : } A_{LONG} = 0.16 \text{ mA/rd}$$

$$\Rightarrow \frac{\Delta I}{\Delta t} = 5.5 \text{ kHz/}\mu\text{s}, \text{ R} = 500 \text{ k}\Omega$$

- In VCR mode : A<sub>SHORT</sub> = 0.47 mA/rd

$$\Rightarrow \frac{\Delta f}{\Delta t} = 16.5 \text{kHz/}\mu\text{s}$$

Note : The capture range is specified within  $\pm$  500Hz with respect to 15625Hz.

#### **Numerical Example**

Let's suppose that in VCR mode there is a frequency variation of  $\pm$  100Hz, this will yield a phase variation of 0.1/16.5, i.e.  $\pm$  6ns which, on a 54cm wide screen, will produce a horizontal shift of  $\Delta_{\text{LINE}} = \pm$  0.06mm !

It is obvious that an excellent image stability is thus obtained.

#### V.3.6.2 - Dynamic study

The loop response in transient mode is quite important. It determines the overall system stability and the phase recovery time, which are imposed by the external filter "f(p)".

The close-loop transfer function is equivalent to a second order system. These time constants are in practice displayed on screen by a bar delivered by a special pattern generator representing the phase errors.

The following optimized results were obtained from filter f(p) connected to Pin 22.

Filter component values are : R1 =  $4.7k\Omega$ , C1 =  $2.2\mu$ F, C = 10nF

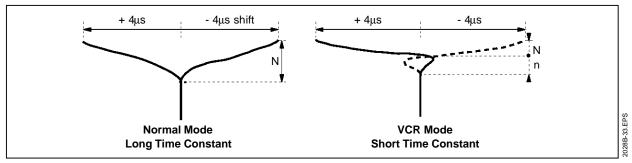

#### A. LONG TIME CONSTANT

- At  $\Delta t$  of  $4\mu s \Rightarrow N=18$  lines, i.e.  $\tau_{LONG} = 1.15$ ms. System oscillations are perfectly damped. Image stability with a noisy video signal is very satisfactory.

#### B. SHORT TIME CONSTANT

- At  $\Delta t = 4\mu s \Rightarrow N = 5$  lines, i.e.  $\tau_{SHORT} = 0.32ms$ - n = 5 lines

One should notice fast phase recovery, naturally followed by bounced oscillations due to the characteristics of a second order device.

As given in application diagram section 6, an other alternative would be to use the following component values :  $R1 = 3.9k\Omega$ ,  $C1 = 4.7\mu$ F, C = 15nF.

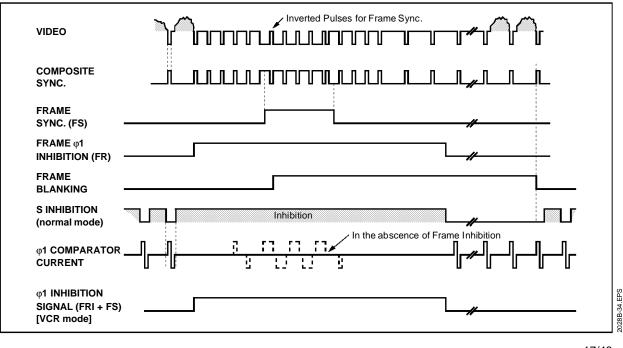

# V.3.7 - Phase comparator inhibition

The phase comparator is disabled under two conditions :

- During frame sync pulse (see Figure 30)

Inverting the line sync pulse contained within the video signal will provide the frame sync pulses required for the synchronization of vertical scanning.

Since the current supply to comparator  $\phi 1$  is controlled by the line sync pulse, the comparator must be inhibited at the time of line sync inversions so as to avoid occurrence of phase errors at the beginning of each frame.

This inhibition is activated during FRI (Frame Retrace Inhibition) issued by frame logic circuitry. If  $\phi 1$  is locked before the vertical scanning synchronization occurs, (e.g. when switching between channels), and since FRI phase is not yet correctly positioned, the  $\phi 1$  must be further inhibited by FS signal which is the extracted frame

Figure 30 : On Screen Display of Time Constants

sync pulse.

- During line scanning (see Figures 31 and 32) This inhibition will eliminate the occurrence of all possible phase errors due to a noisy sync signal or parasitics during the line scanning phase. It yields excellent display stability at noisy video signals.

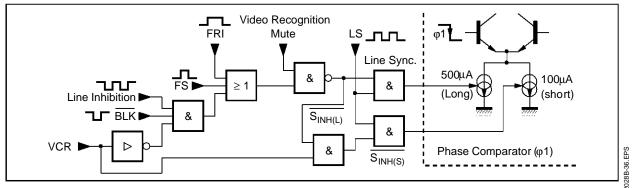

- f1 Inhibition in long time constant mode (VCR = 0)

$S_{INH(LONG)} = Mute . (FRI + FS + BLK . LINE_{INH})$ and  $S_{INH(SHORT)} = 1$

Inhibition is activated during, frame sync, FRI and each time line trace interval - except at frame beginning between lines 8 and 21.

• \$\phi1\$ Inhibition in short time constant mode (VCR = 1)

$$\begin{split} S_{\text{INH(SHORT)}} &= \text{Mute} \ . \ (FRI + FS) = S_{\text{INH(LONG)}} \\ \text{In VCR mode, inhibition is disabled during line} \\ \text{trace since phase or frequency variations are} \\ \text{not taken into account instantenously.} \end{split}$$

SGS-THOMSON

#### Figure 32

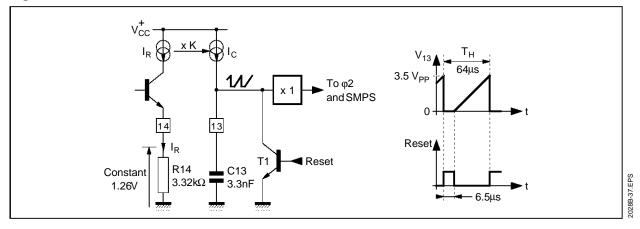

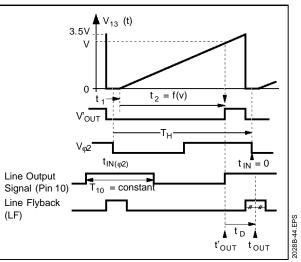

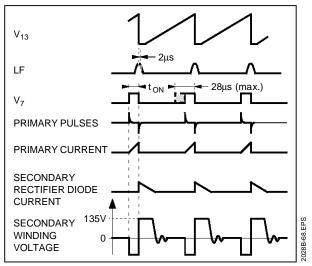

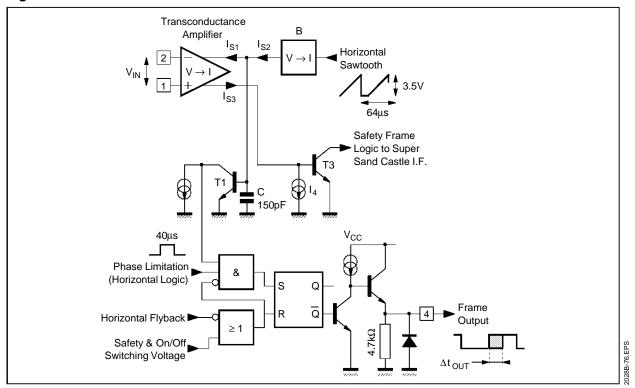

#### V.4 - Line saw-tooth generator

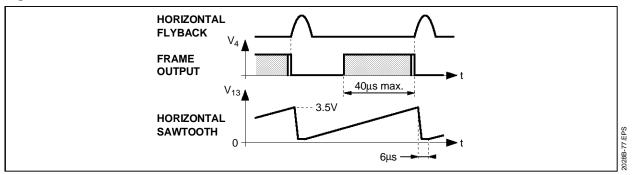

Before going through a detailed study of the second phase locked loop " $\phi$ 2", let's have an overview of the line saw-tooth generator which has been mainly implemented for  $\phi$ 2 phase variations and also the phase modulation of the switching power supply. It uses the combination of an external capacitor connected to Pin 13 and an internally implemented constant current generator generate a saw-tooth voltage at line frequency.

Its frequency is determined by the reset frequency

of the capacitor "C13". This reset signal is issued by the line logic circuitry at a period multiple of VCO period (×32).

$$- I_{C} = K \cdot I_{R} = K \cdot \frac{1.26}{R_{14}} = 200\mu A$$

$$- V_{13PP} = \frac{I_{C} (T_{H} - t_{reset})}{C13} = \frac{K \cdot 1.26 (T_{H} - t_{reset})}{R_{14} \cdot C_{13}}$$

$$= 3.48V$$

- VCE(SAT)T1

$$\approx 20 \text{mV} \Rightarrow \text{V13(MAX)} = 3.5\text{V}$$

- In sync mode :

$T_H = 64 \mu s$ ,  $t_{RESET} = 6.5 \mu s$ ,  $K = 0.527 \pm 2\%$

#

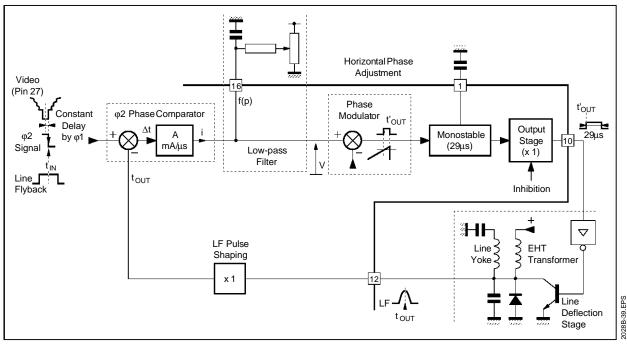

This stage controls the horizontal deflection of the electron beam i.e., the horizontal picture scanning. The frequency of operation, in the absence of video signal, is a multiple of the VCO frequency, i.e. 15625Hz - 500Hz.

When video signal is present, the scanning frequency is synchronized with the video signal through the first phase locked-loop " $\phi$ 1".

The output rectangular waveform signal drives the line switching transistor. This transistor, when turned-off, generates what is commonly called the "line flyback".

In order to obtain a horizontally centered picture, the line flyback (LF) must coincide with the blanking time on tube cathodes.

The turn-off delay is due to transistor base storage time. This time varies in different TV sets as the transistors employed may have different operating characteristics which are functions of temperature variations, power rating and base drive.

Therefore, it follows that in order to obtain stable

**Figure 36** : Second Phase Locked Loop "φ2" Block Diagram

image centering, the line flyback must be phaselocked with respect to the video signal.

The second phase-locked loop also offers the possibility of horizontal phase-shift adjustment.

# V.5.1 - Duty of different building blocks V.5.1.1 - "\u00f62" Phase comparator

This block generates a current proportional to the phase difference between the phase reference " $\phi$ 2" and the middle of the line flyback to be phase-locked.

# V.5.1.2 - Low-pass filter

- Rejects the parasitic component "sum of phases"

- Smoothens the "phase difference" component

- Allow "phase adjustment" by generating an error within the loop

# V.5.1.3 - Phase modulator

Uses the line saw-tooth voltage to convert the voltage delivered by the low-pass filter into a phase corresponding to the line transistor turn-off control signal.

# V.5.1.4 - Flip-flop

Generates the turn-off control signal for a constant time (fixed by the external capacitor), the phase of which is set by the modulator.

# V.5.1.5 - Output stage

- Delivers the control signal for line transistor driver

- Disables the output during start-up and protection phases

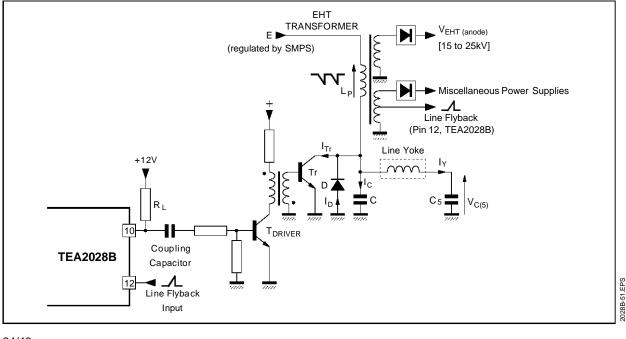

# V.5.1.6 - Line deflection stage

- Generates the saw-tooth current for line yoke

- Generates the high voltage required by picture tube and other supply voltages

- The line flyback information is provided by the EHT transformer.

# V.5.2 - Operation of building blocks

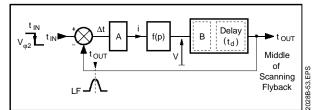

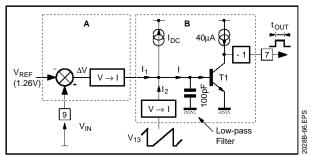

To provide an easier understanding of the subject, the " $\phi$ 2" loop study will be covered as a function of various time intervals and not as a function of phase.

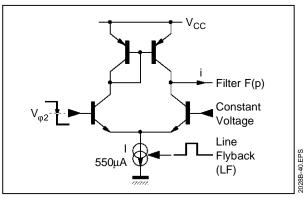

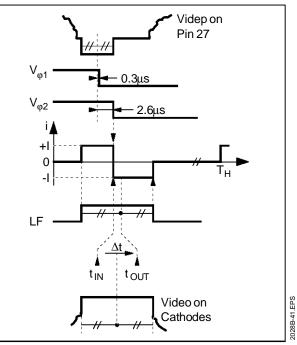

# V.5.2.1 - Phase comparator "\operator"

The operation is identical to that of " $\phi$ 1" loop.

The  $V_{\varphi 2}$  signal issued by logic block is phased with respect to the middle of line sync pulse on Pin 27 and delayed by a 2.6µs interval so as to be at the middle of blanking time on video cathodes.

The output current component  $^{\prime\prime}2f_{H}^{\prime\prime}$  is rejected by the low-pass filter.

# Figure 37

- The average current is  $i = 2I \frac{\Delta t}{T_H}$

Where :  $\Delta t = t_{IN} - t_{OUT}$

$$A = \frac{1}{\Delta t} = \frac{21}{T_H} = 17 \mu A/\mu s$$

At : I = 550 $\mu$ A and T<sub>H</sub> = 64 $\mu$ s, "A" will remain constant since "I" is a multiple of "I<sub>REF</sub>" current on Pin 14.

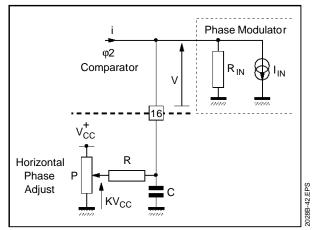

# V.5.2.2 - Low-pass filter f(p)

The horizontal phase-shift adjustment is taken into account : see Figure 39

- Filter V = f(i) transfer characteristic is given as : V = Zi +  $\frac{Z}{R} \cdot K \cdot V_{CC}$  - Z · I<sub>IN</sub>

Where :

•

$$Z = R_{IN} // R // \frac{1}{C \cdot p}$$

• RIN, IIN : modulator input characteristics

Figure 39

# In Dynamic Mode

$$-V = Zi \Longrightarrow f(p) = \frac{V}{i} = Z(p) = \frac{R'}{1 + \tau p}$$

Where :

- $R' = R_{IN} // R$  (R >> Potentiometer P)

- $\tau = R'$  . C : Filter time constant

The network behaves as a first order low-pass filter

whose cut-off frequency at -3dB is :  $f_{-3dB} = \frac{1}{2\pi R'C}$

# Filter component values

- R = 470k $\Omega$  and C = 22nF

- In practice, (K ∈ [0,1]) V<sub>CC</sub> = 12V

- R<sub>IN</sub> = 25MΩ, I<sub>IN</sub> = 0.65μA (base input current)

F<sub>-3db</sub> = 15.7Hz with adjustment and 0.3Hz without adjustment

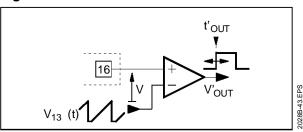

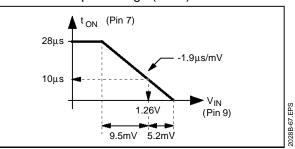

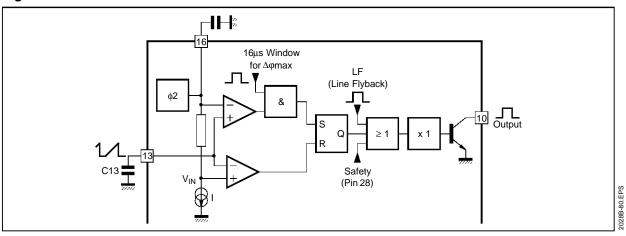

# V.5.2.3 - Phase modulator

This is built around a comparator which converts the filter voltage to a rectangular waveform such that its rising edge phase, variable as a function of filter voltage "V", will trigger the line transistor turnoff control circuitry.

The conversion gain is determined by the slope of the line saw-tooth applied to comparator.

Figure 40

# Figure 41

Transfer characteristic is given by :

$$\frac{\Delta t'_{OUT}}{\Delta V} = \frac{\Delta t_{13}}{\Delta V_{13}} = B = 16.4 \mu s/V$$

therefore  $t_2 = B.V$

Let's consider the delay interval between " $t_{OUT}$ " and the reference time " $t_{IN}$ "

- t<sub>H</sub>

where tout is the middle of line flyback :

$$t_{OUT} - t_{IN} = t_2 + t_d + t_1$$

Where :

- t1 = 4.3μs

- Reset for  $V_{13}$  and  $V_{\varphi 2}$  are signals coming from line logic block and are synchronized on line sync

- t<sub>d</sub> = 2 to 15μs

Delay between leading edge of output signal -Pin 10 - and the middle of line flyback

- tн = 64µs

- $t_{OUT}$   $t_{IN}$  = B.V +  $t_d$  59.7 $\mu$ s

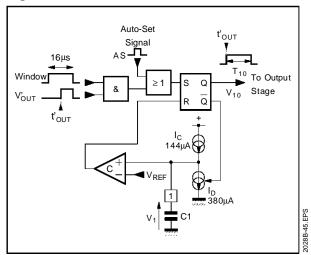

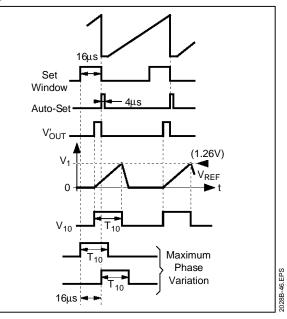

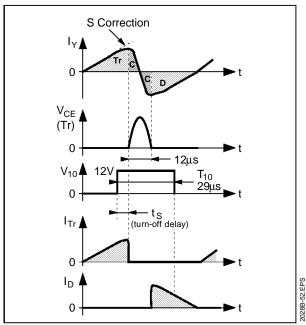

# **V.5.2.4 - Line flip-flop** (TEA2028 only for TEA2029 refer to Section VII.6)

It generates a constant duration rectangular signal used to turn-off the line transistor. It is triggered by the rising-edge of the phase comparator output voltage and reset after capacitor on pin 1 is charged.

# A. BLOCK DIAGRAM

"V'OUT" will set the flip-flop thereby allowing the capacitor "C1" to be charged by current "I<sub>C</sub>" delivered through current generator. The voltage across capacitor begins rising until it reaches "V<sub>REF</sub>". At this time, comparator "C" is triggered, the output of which will in turn reset the flip-flop. The capacitor "C" is consequently discharged by current I<sub>D</sub> - I<sub>C</sub>.

# Figure 42

B. T10 CALCULATION (see Figure 43)

$$T_{10} = \frac{C1 \cdot \Delta V_1}{I_0} = \frac{C1 \cdot V_{REF}}{I_0}$$

"Ic" is a fraction of "IREF" on pin 14

$$I_{C} = \frac{I_{REF}}{\alpha} = \frac{V_{REF}}{\alpha \cdot R14} = 144 \mu A$$

$\Rightarrow T_{10} = \alpha \cdot R14 \cdot C1 = 2.64 \cdot R14 \cdot C1$ with R14 = 3.32kΩ, C1 = 3.3nF  $\Rightarrow$  T<sub>10</sub> = 29µs

-  $T_{10}$  is independent from temperature and V<sub>CC</sub>

-  $\alpha$  has a maximum dispersion of  $\pm$  3% from device to device

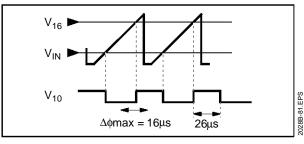

# C. 16µs WINDOW

This window is generated by the line logic circuitry and sets the maximum phase variations of the output signal " $V_{10}$ ".

Also, for protection purposes, should " $V_{16}$ " voltage equal "0", the output signal will be always present and have a maximum phase shift of 16µs with respect to the falling-edge of the line saw-tooth.

# D. AUTO-SET TO "1"

To provide protection, this function will trigger the flip-flop if the modulator is disabled, i.e.  $V_{16} > V_{13(MAX)}$ .

#### Figure 43

# E. MAXIMUM "T10" VALUE AS A FUNCTION OF "C1"

$\begin{array}{rl} T_{10 \ (Min.)}: & 16\mu s \ (window) + 4\mu s \ (auto \ set) = 20\mu s \\ \Rightarrow C1_{(Min.)} = 2.3nF \end{array}$

$$\begin{array}{rl} T_{10 \text{ (Max.)}} \colon & \text{for } \frac{C1 \cdot V_{\text{REF}}}{I_D - I_C} + \frac{C1 \cdot V_{\text{REF}}}{I_C} \leq 64 \mu s \\ \Rightarrow T_{10 \text{ (Max.)}} = 40 \mu s \Rightarrow C1_{\text{(Max.)}} = 4.6 n F \end{array}$$

For normal operation, C1 value has to be chosen between 2.3nF and 4.6nF.

If Pin 1 is grounded, output signal (Pin 10) is inhibited and goes high.

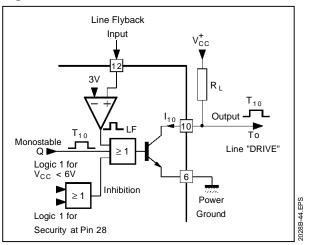

# V.5.2.5 - Line output stage & inhibitions

Open-collector output :

V<sub>10(SAT)</sub> < 1.5V at I<sub>10(MAX)</sub> = 20mA The line output (Pin 10) will go high if either the following three inhibitions is activated :

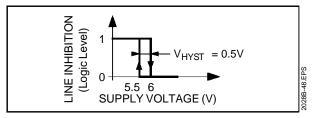

# A. INHIBITION AT START-UP

This is generated by a hysteresis comparator which is driven by "KVcc" and the "1.26V" reference voltage.

This inhibition is mandatory since the device will operate only at  $V_{CC} \ge 5V$ .

# Figure 45

# B. INHIBITION DURING LINE FLYBACK

The output signal Pin 10 is high during line transistor turn-off. The leading edge of output signal Pin 10 turns off the line transistor after a delay interval (storage time).

The line transistor turn-off generates an overvoltage on the collector corresponding to the line flyback pulse. During this interval, in order to avoid transistor destruction, the Pin 10 output must absolutely remain high.

This is done internally with the line flyback pulse (Pin 12), which forces Pin 10 output to high level during the line flyback time.

# C. SAFETY INHIBITION

The device has a security input terminal "Pin 28". If a signal lower than  $V_{REF}$  (1.26V) is applied to this pin. line and power supply outputs are all inhibited.

This function is particularly useful for TV chassis protection. Refer to section V.7.5 for further details.

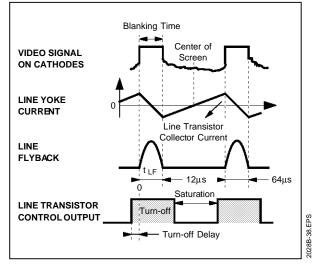

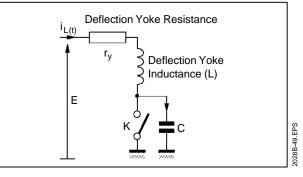

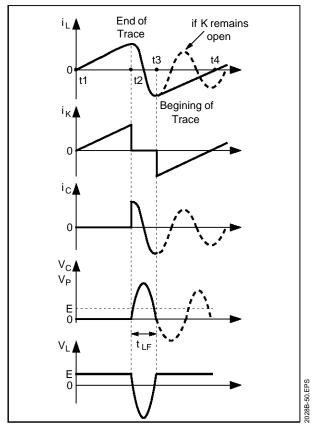

# V.5.2.6 - Line deflection stage

This chapter will cover a general description of the "horizontal deflection stage" employed almost commonly in all recent TV sets.

Deflection of electron beam is proportional to the intensity of magnetic field induced by the line yoke. This yoke is equivalent to an inductor. The deflection is therefore proportional to the current through inductor.

In order to obtain a linear deflection from left to right as a function of time, a saw-tooth current must be generated within the yoke. The approach is to apply a switched DC voltage to the line yoke.

- When K is closed :  $i_{L(t)} = \frac{E}{r_v} \left( 1 - e^{-\frac{ryt}{L}} \right)$

- $\frac{L}{r_v}$  is always higher than half of trace time :

$$\frac{t_{trace}}{2} = \frac{T_H - t_{LF}}{2} = \frac{64 - 12}{2} = 26 \mu s$$

- "iL" variations as a function of time :

# Figure 46

$\frac{di_{L}}{dt} = \frac{E}{L} e^{-\frac{ryt}{L}} \approx \frac{E}{L} \left( \text{ for } t \ll \frac{L}{r_{y}} \right)$ The current will therefore be linear as a function of time  $i_{L(t)} = \frac{E}{L} \cdot t$  from "t<sub>1</sub>" to "t<sub>2</sub>" which is the second portion of the line trace interval.

- Current at the end of trace :  $I_M = \frac{E}{L} \cdot \frac{t_{TRACE}}{2}$

- Energy stored within inductor :  $W = \frac{1}{2} \cdot L \cdot I_M^2$

- If the switch is opened at  $t = t_2$ , the "L.C" combination will enter into oscillation, the energy stored within inductor is transfered to the capacitor, which will return it to the inductor and so on.

The circuit period is classically given by :

$$T = 2\pi \cdot \sqrt{LC}$$

If "K" is closed at time "t3", the inductor will once again have a voltage "E" across its terminals. The current falls linearly until "t4". This phase corresponds to the first half of line trace interval.

The overvoltage across C is :

$$V_{P} = E \frac{t_{trace}}{2\sqrt{LC}} + E \text{ during } t_{LF} \approx \pi \sqrt{LC}$$

That is :

$$V_P = E \frac{t_{trace} \cdot \pi}{2t_{LF}} + E$$

In practice, E is higher than 100V.

$t_{trace} = 52\mu s, t_{LF} = 12\mu s \Rightarrow V_P \ge 780V$

Note that this overvoltage is almost 8 times higher than the source voltage "E". This overvoltage is applied to the primary winding of a "step-up transformer" (EHT Transformer) in order to generate the high voltage required by picture tube anode.

In practice, the power switch "K" is built by a combination of "High Voltage Switching Transistor" and "Fast Recovery Diode".

#### Figure 47

If considered in average value, it is seen that the voltage across capacitor"CS" is almost equal to the source voltage "E". The saw-tooth current through this capacitor will produce a parabolic ripple around "E", which will thus modify the equivalent source of the line yoke and induce a modified current of "S" shape within the yoke. This "S" current is used to produce a linear picture as a function of the picture tube geometry.

The basic arrangement can be reconstructed by assuming that the equivalent inductor "L" is the transformer "L<sub>P</sub>" and line yoke inductors put in parallel (since VC  $_{S(AV)} = E$ ).

The output Pin 10 of TEA2028 is applied to a matching stage called "line driver" the output of which drives the power transistor " $T_r$ ". The matching stage is necessary for optimized base drive.

At middle of trace, the transistor enters into saturation and its current rises linearly.  $V_{10}$  will then issue a control signal to turn the transistor off. The transistor will be in fact turned-off after a delay interval "ts" (storage time) varying from 2 to 8 µs depending on application. The system will then enter into oscillation during its half-period thereby generating the line flyback. At the end of flyback time, the line yoke current is negative while the voltage across capacitor"C" has fallen to zero. The energy transfer automatically takes place by the recovery diode during the first portion of trace time.

Also, it is clear that the line scanning phase with respect to video signal is determined by the risingedge of Pin 10 output signal.

SGS-THOMSON

MICROELECTRONI

#### Figure 49

High level duration (T10) of Pin 10 output signal must be higher than the delay interval "ts(MAX)" + the flyback time (i.e.  $8 + 12 = 20\mu s$ ) and must turn-off before the end of diode conduction :

$$T_{10} < t_{S(Min.)} + t_{LF} + \frac{t_{trace}}{2} \Rightarrow < 40 \mu s$$

In practice, one will select the pin 1 capacitor C1 = 3.3nF to yield T<sub>10</sub> =  $29\mu s$ .

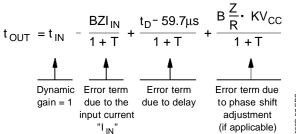

### V.5.3 - Characteristics of loop "02"

The function to calculate is a time with respect to the origin time set by " $V_{\phi 2}$ ". In fact, it is an easy task to inter-relate the horizontal displacement (in mm) to a time interval specified in us.

For a large screen width of 540mm, the horizontal scanning time :  $64 - 12 = 52\mu s$ , which corresponds to : ≈ 10mm/µs.

# Figure 50

-  $i = A \cdot (t_{IN} - t_{OUT})(1)$  $- V = Z \cdot i + \frac{Z}{R} \cdot K \cdot V_{CC} - Z \cdot I_{IN}$ (2) -  $t_{OUT}$  -  $t_{IN} = B \cdot V + t_d$  - 59.7 $\mu$ s (3)

- $-Z = \frac{R'}{1 + \tau p}$ - R' = R<sub>IN</sub> // R  $- A = 17 \mu A / \mu s$

- τ = R'Ċ

- B = 16.4µs/V

The open-loop dynamic gain is :

$$T = ABf(p) = ABZ = \frac{ABR'}{1 + \tau p} \qquad (4)$$

The system exhibits the characteristics inherent to a first order circuit and is therefore stable.

Combining equations (1), (2), (3) and (4), the  $t_{OUT}$ delay is found as follows :

028B-97.EPS

It is therefore clear that the second phase-locked loop does not cause any dynamic delay.

This can be explained by the fact that the phase modulator responds instanenously to all variations of " $\phi_2$ ".

#### V.5.3.1 - Study of the Static Error

$t_{IN} = 0$  (phase of  $V_{\phi 2}$ ) is taken as timing reference. The equivalent impedance of F(p) filter is :

- $R' = 460k\Omega (R // R_{IN})$  : if an adjustment is applied to Pin 16. or

- Modulator input resistance RIN =  $25M\Omega$  : without adjustment

A. PHASE SHIFT ERROR IN CASE OF NO ADJUSTMENT

Equation (5) becomes:

$$T_{OUT} = \frac{BR_{IN} I_{IN}}{1 + T_1} + \frac{t_D - 59.7\mu s}{1 + T_1}$$

with:  $T1 = ABR_{IN}$

Where :

$-R_{IN} = 25M\Omega$ tout = - 46ns  $-I_{IN} = 0.65 mA$ which corresponds to a - t<sub>d</sub> = 10µs picture shift of 0.46mm !  $-T1 = 6.8 \cdot 10^3 = 76$ dB

The error is quite negligible and thanks to rather high open-loop gain, the display accuracy with respect to the phase set by " $\phi_2$ ", is very satisfactory.

#### B. STUDY OF SHIFT ADJUSTMENT

With R, P network connected to Pin 16, the  $t_{\text{out}}$  becomes :

| tour - | – BR′ I <sub>IN</sub> | t <sub>D</sub> – 59.7μs | $B\frac{R'}{R} \cdot KVcc$ |

|--------|-----------------------|-------------------------|----------------------------|

| 1001 = | 1+T2                  | $1 + T_2$               | + 1 + T <sub>2</sub>       |

With : T2 = ABR' (where R' = R //  $R_{IN}$ ) and K  $\in$  [0;1] Substituting the following values into above equation :

- R = 470kΩ

- R' =  $470k\Omega / 25M\Omega = 46k\Omega$

- $A = 17 \times 10^{-6} A/\mu s$

- B = 16µs/V

- $t_d = 10 \mu s$

- T<sub>2</sub> = 125

- V<sub>CC</sub> = 12V

- $t_{OUT}$  = 38ns 390ns + 1.5µs×K therefore  $t_{out}$  = 1.5· K 0.43 ( in µs )

If K varies between 0 and 1

$\Rightarrow$  t<sub>out</sub> [-0.43ms to 1.07  $\mu s$ ]

which corresponds to a picture displacement of :  $\Delta_{\text{LINE}}$  [- 4mm to + 11mm].

Shift variations as a function of  $V_{CC}$  (with adjustment)

$$\frac{dt_{OUT}}{dV_{CC}} = \frac{B\frac{R'}{R} \cdot K}{1 + T_2} \approx \frac{B\frac{R'}{R} \cdot K}{T_2} \approx \frac{K}{AR}$$

$$= K \cdot 0.12 \mu s/V \quad \left[\frac{dL}{dV_{CC}} = 0.34 \text{mm/V} \\ \text{at } K_{\text{NOMINAL}} = 0.28 \right]$$

Therefore, a constant  $V_{CC}$  must be applied to the potentiometer.

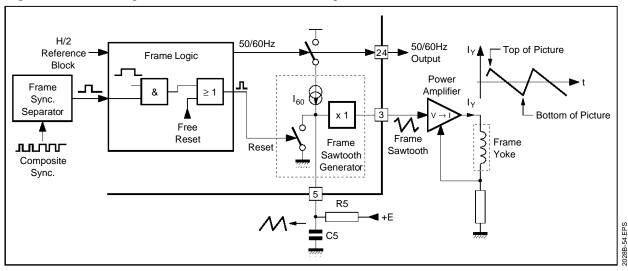

#### V.6 - Vertical deflection driver stage

This stage must constantly drive the vertical spot deflection. Such deflection will horizontally scan the screen from top to bottom thus generating the displayed image. Similar to horizontal deflection, the vertical deflection is obtained by magnetic field variations of a coil mounted on the picture tube.

A saw-tooth current at frame frequency will go through this coil commonly called "frame yoke". Frame period is the time required for the entire screen to be scanned vertically.

C.C.I.R. and N.T.S.C. TV standards require respectively 50Hz and 60Hz Frame Scanning Frequencies. Also, a full screen display is obtained by two successive vertical scannings such that the second scanning is delayed by a half line period with respect to the first.

This method increases the number of images per second (50 half images/s or 50 frames/s in 50Hz standard). This scanning mode called "Interlaced Scanning" eliminates the fliker which would have been otherwise produced by scanning 25 entire images per second.

The circuit will generate a saw-tooth voltage which is linear as a function of time and called "frame saw-tooth". A power amplifier will deliver to the "frame yoke" a current proportional to this sawtooth voltage. It is thus clear that this saw-tooth voltage reflects the function of the vertical spot deflection; which must itself be synchronized with the video signal. Synchronization signals are obtained from an extraction stage which will extract the useful signal during line pulse inversion of the composite sync signal.

Synchronization occurs at the end of scanning, in other words, when the saw-tooth voltage at Pin 5 is reset. This function is accomplished by the "frame logic circuitry" of full digital implementation. This processing method offers various advantages :

- Accurate free-running scanning frequency eliminates the frequency adjustment required by previous devices.

- **Digital synchronization** locked onto half line frequency thereby yielding perfect interlaced display and excellent stability with noisy video signal.

- Automatic 50/60Hz standard recognition and switching the corresponding display amplitude.

- Optimized synchronization in VCR mode.

- Generation of various accurate time intervals, such as narrow "sync windows" thus reducing considerably the vertical image instability in case of for instance, mains interference, superimposed on frame sync pulse.

- Generation of vertical blanking signal for spot flyback and to protect the picture tube in case of scanning failure.

Figure 51 : Block Diagram of the Vertical Deflection Stage

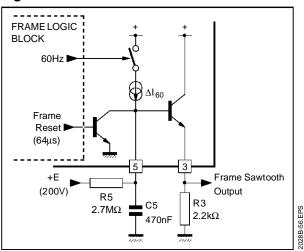

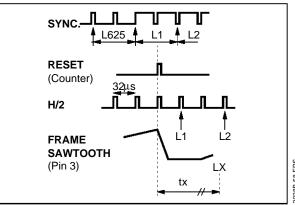

#### V.6.1 - Frame sync extraction

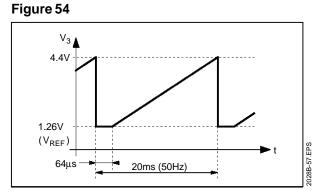

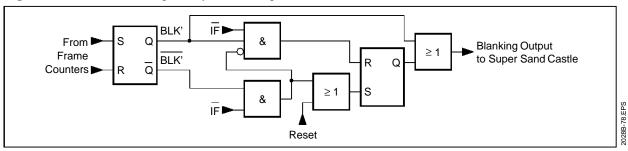

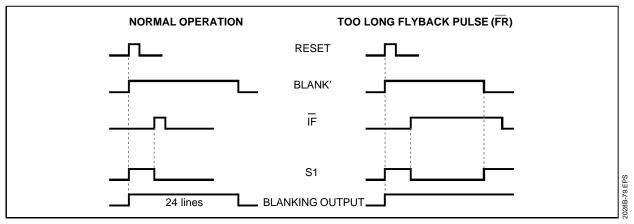

The main duty of this stage is to extract the frame sync pulses contained in composite sync signal.