# **5V ECL Programmable Delay Chip**

The MC10E/100E196 is a programmable delay chip (PDC) designed primarily for very accurate differential ECL input edge placement applications.

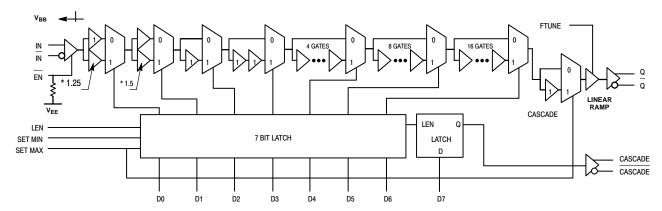

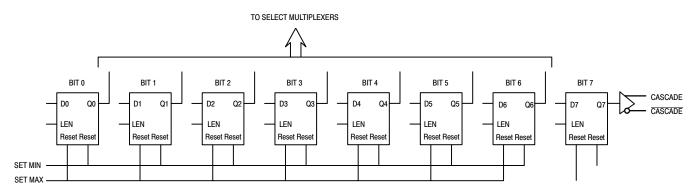

The delay section consists of a chain of gates and a linear ramp delay adjust organized as shown in the logic symbol. The first two delay elements feature gates that have been modified to have delays 1.25 and 1.5 times the basic gate delay of approximately 80 ps. These two elements provide the E196 with a digitally-selectable resolution of approximately 20 ps. The required device delay is selected by the seven address inputs D[0:6], which are latched on chip by a high signal on the latch enable (LEN) control.

The FTUNE input takes an analog voltage and applies it to an internal linear ramp for reducing the 20 ps L.S.B. minimum resolution still further. The FTUNE input is what differentiates the E196 from the E195.

An eighth latched input, D7, is provided for cascading multiple PDC's for increased programmable range. The cascade logic allows full control of multiple PDC's, at the expense of only a single added line to the data bus for each additional PDC, without the need for any external gating.

The  $V_{BB}$  pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to  $V_{BB}$  as a switching reference voltage.  $V_{BB}$  may also rebias AC coupled inputs. When used, decouple  $V_{BB}$  and  $V_{CC}$  via a 0.01  $\mu F$  capacitor and limit current sourcing or sinking to 0.5 mA. When not used,  $V_{BB}$  should be left open.

The 100 Series contains temperature compensation.

- 2.0 ns Worst Case Delay Range

- ≈20 ps/Delay Step Resolution

- Linear Input for Tighter Resolution

- >1.0 GHz Bandwidth

- On Chip Cascade Circuitry

- PECL Mode Operating Range: V<sub>CC</sub>= 4.2 V to 5.7 V with V<sub>EE</sub>= 0 V

- NECL Mode Operating Range: V<sub>CC</sub>= 0 V with V<sub>EE</sub>= -4.2 V to -5.7 V

- Internal Input Pulldown Resistors

- ESD Protection: > 1 KV HBM, > 75 V MM

- Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

- Moisture Sensitivity Level 1

For Additional Information, see Application Note AND8003/D

- Flammability Rating: UL-94 code V-0 @ 1/8", Oxygen Index 28 to 34

- Transistor Count = 425 devices

http://onsemi.com

#### **ORDERING INFORMATION**

| Device        | Package | Shipping       |  |  |  |  |

|---------------|---------|----------------|--|--|--|--|

| MC10E196FN    | PLCC-28 | 37 Units/Rail  |  |  |  |  |

| MC10E196FNR2  | PLCC-28 | 500 Units/Reel |  |  |  |  |

| MC100E196FN   | PLCC-28 | 37 Units/Rail  |  |  |  |  |

| MC100E196FNR2 | PLCC-28 | 500 Units/Reel |  |  |  |  |

#### LOGIC DIAGRAM AND PINOUT ASSIGNMENT

#### D5 D6 18 TTUNE D1 L 17 NC DO L LEN U28 VEE [ □ v<sub>cco</sub> MC10E196 MC100E196 IN 🛛 2 ĪN [ ΠQ 13 $V_{BB}$ 12 V<sub>CCO</sub> SET MAX ĒΝ NC NC

Figure 1. Pinout: 28-Lead PLCC (Top View)

Warning: All  $V_{CC}$ ,  $V_{CCO}$ , and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

#### **PIN DESCRIPTION**

| PIN                                | FUNCTION                          |

|------------------------------------|-----------------------------------|

| IN/IN                              | ECL Signal Input                  |

| EN                                 | ECL Input Enable (H Forces Q Low) |

| D[0:7]                             | ECL Mux Select Inputs             |

| Q/Q                                | ECL Signal Output                 |

| LEN                                | ECL Latch Enable                  |

| SET MIN                            | ECL Min Delay Set                 |

| SET MAX                            | ECL Max Delay Set                 |

| CASCADE                            | ECL Cascade Signal                |

| FTUNE                              | ECL Linear Voltage Input          |

| $V_{BB}$                           | Reference Voltage Output          |

| V <sub>CC</sub> , V <sub>CCO</sub> | Positive Supply                   |

| V <sub>EE</sub>                    | Negative Supply                   |

| NC                                 | No Connect                        |

#### **TRUTH TABLE**

| ĒN     | L | Q = IN               |

|--------|---|----------------------|

| EN     | Н | Q Logic Low          |

| LEN    | L | Pass Through D[0:10] |

| LEN    | Н | Latch D[0:10]        |

| SETMIN | L | Normal Mode          |

| SETMIN | Н | Min Delay Path       |

| SETMAX | L | Normal Mode          |

| SETMAX | Н | Max Delay Path       |

<sup>\*</sup> DELAYS ARE 25% OR 50% LONGER THAN STANDARD (STANDARD ≈ 80 PS)

Figure 2. LOGIC DIAGRAM - SIMPLIFIED

<sup>\*</sup> All V<sub>CC</sub> and V<sub>CCO</sub> pins are tied together on the die.

#### MAXIMUM RATINGS (Note 1)

| Symbol           | Parameter                                | Condition 1           | Condition 2         | Rating       | Units |

|------------------|------------------------------------------|-----------------------|---------------------|--------------|-------|

| V <sub>CC</sub>  | PECL Mode Power Supply                   | V <sub>EE</sub> = 0 V |                     | 8            | V     |

| V <sub>EE</sub>  | NECL Mode Power Supply                   | V <sub>CC</sub> = 0 V |                     | -8           | V     |

| V <sub>I</sub>   | PECL Mode Input Voltage                  | V <sub>EE</sub> = 0 V | $V_{I} \leq V_{CC}$ | 6            | V     |

|                  | NECL Mode Input Voltage                  | $V_{CC} = 0 V$        | $V_I \ge V_{EE}$    | -6           | V     |

| I <sub>out</sub> | Output Current                           | Continuous            |                     | 50           | mA    |

|                  |                                          | Surge                 |                     | 100          | mA    |

| I <sub>BB</sub>  | V <sub>BB</sub> Sink/Source              |                       |                     | ± 0.5        | mA    |

| TA               | Operating Temperature Range              |                       |                     | 0 to +85     | °C    |

| T <sub>stg</sub> | Storage Temperature Range                |                       |                     | -65 to +150  | °C    |

| $\theta_{JA}$    | Thermal Resistance (Junction to Ambient) | 0 LFPM                | 28 PLCC             | 63.5         | °C/W  |

|                  |                                          | 500 LFPM              | 28 PLCC             | 43.5         | °C/W  |

| θЈС              | Thermal Resistance (Junction to Case)    | std bd                | 28 PLCC             | 22 to 26     | °C/W  |

| V <sub>EE</sub>  | PECL Operating Range                     |                       |                     | 4.2 to 5.7   | V     |

|                  | NECL Operating Range                     |                       |                     | -5.7 to -4.2 | V     |

| T <sub>sol</sub> | Wave Solder                              | <2 to 3 sec @ 248°C   |                     | 265          | °C    |

<sup>1.</sup> Maximum Ratings are those values beyond which device damage may occur.

## 10E SERIES PECL DC CHARACTERISTICS $V_{CCx}$ = 5.0 V; $V_{EE}$ = 0.0 V (Note 2)

|                    |                                                                 |      | 0°C  |      |      | 25°C |      |      | 85°C |      |      |

|--------------------|-----------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|

| Symbol             | Characteristic                                                  | Min  | Тур  | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub>    | Power Supply Current                                            |      | 130  | 156  |      | 130  | 156  |      | 130  | 156  | mA   |

| V <sub>OH</sub>    | Output HIGH Voltage (Note 3)                                    | 3980 | 4070 | 4160 | 4020 | 4105 | 4190 | 4090 | 4185 | 4280 | mV   |

| V <sub>OL</sub>    | Output LOW Voltage (Note 3)                                     | 3050 | 3210 | 3370 | 3050 | 3210 | 3370 | 3050 | 3227 | 3405 | mV   |

| V <sub>IH</sub>    | Input HIGH Voltage (Single Ended)                               | 3830 | 3995 | 4160 | 3870 | 4030 | 4190 | 3940 | 4110 | 4280 | mV   |

| V <sub>IL</sub>    | Input LOW Voltage (Single Ended)                                | 3050 | 3285 | 3520 | 3050 | 3285 | 3520 | 3050 | 3302 | 3555 | mV   |

| $V_{BB}$           | Output Voltage Reference                                        | 3.62 |      | 3.63 | 3.65 |      | 3.75 | 3.69 |      | 3.81 | V    |

| V <sub>IHCMR</sub> | Input HIGH Voltage Common Mode<br>Range (Differential) (Note 4) |      | TBD  |      |      | TBD  |      |      | TBD  |      | V    |

| I <sub>IH</sub>    | Input HIGH Current                                              |      |      | 150  |      |      | 150  |      |      | 150  | μΑ   |

| I <sub>IL</sub>    | Input LOW Current                                               | 0.5  | 0.3  |      | 0.5  | 0.25 |      | 0.3  | 0.2  |      | μΑ   |

NOTE: Devices are designed to meet the DC specifications shown in the above table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained.

- 2. Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary +0.46 V / –0.06 V.

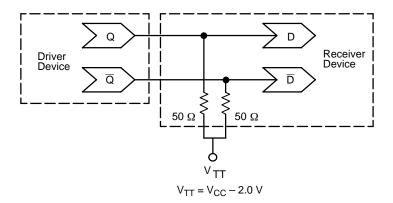

- 3. Outputs are terminated through a 50 ohm resistor to V<sub>CC</sub>-2 volts.

- 4. V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, max varies 1:1 with V<sub>CC</sub>.

#### 10E SERIES NECL DC CHARACTERISTICS V<sub>CCx</sub>= 0.0 V; V<sub>EE</sub>= -5.0 V (Note 5)

|                    |                                                                 |       | 0°C   |       | 25°C  |                  | 85°C  |       |       |       |      |

|--------------------|-----------------------------------------------------------------|-------|-------|-------|-------|------------------|-------|-------|-------|-------|------|

| Symbol             | Characteristic                                                  | Min   | Тур   | Max   | Min   | Тур              | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub>    | Power Supply Current                                            |       | 130   | 156   |       | 130              | 156   |       | 130   | 156   | mA   |

| V <sub>OH</sub>    | Output HIGH Voltage (Note 6)                                    | -1020 | -930  | -840  | -980  | -895             | -810  | -910  | -815  | -720  | mV   |

| V <sub>OL</sub>    | Output LOW Voltage (Note 6)                                     | -1950 | -1790 | -1630 | -1950 | -1790            | -1630 | -1950 | -1773 | -1595 | mV   |

| V <sub>IH</sub>    | Input HIGH Voltage (Single Ended)                               | -1170 | -1005 | -840  | -1130 | <del>-</del> 970 | -810  | -1060 | -890  | -720  | mV   |

| V <sub>IL</sub>    | Input LOW Voltage (Single Ended)                                | -1950 | -1715 | -1480 | -1950 | -1715            | -1480 | -1950 | -1698 | -1445 | mV   |

| V <sub>BB</sub>    | Output Voltage Reference                                        | -1.38 |       | -1.37 | -1.35 |                  | -1.25 | -1.31 |       | -1.19 | V    |

| V <sub>IHCMR</sub> | Input HIGH Voltage Common Mode<br>Range (Differential) (Note 7) |       | TBD   |       |       | TBD              |       |       | TBD   |       | V    |

| I <sub>IH</sub>    | Input HIGH Current                                              |       |       | 150   |       |                  | 150   |       |       | 150   | μΑ   |

| I <sub>IL</sub>    | Input LOW Current                                               | 0.5   | 0.3   |       | 0.5   | 0.065            |       | 0.3   | 0.2   |       | μΑ   |

NOTE: Devices are designed to meet the DC specifications shown in the above table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained.

- 5. Input and output parameters vary 1:1 with V<sub>CC</sub>.  $V_{EE}$  can vary +0.46 V / -0.06 V.

- 6. Outputs are terminated through a 50 ohm resistor to  $V_{\text{CC}}$ -2 volts.

- 7. V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, max varies 1:1 with V<sub>CC</sub>.

#### 100E SERIES PECL DC CHARACTERISTICS V<sub>CCx</sub>= 5.0 V; V<sub>EE</sub>= 0.0 V (Note 8)

|                    |                                                                  |      | 0°C  |      | 25°C |      | 85°C |      |      |      |      |

|--------------------|------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|

| Symbol             | Characteristic                                                   | Min  | Тур  | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub>    | Power Supply Current                                             |      | 130  | 156  |      | 130  | 156  |      | 150  | 179  | mA   |

| V <sub>OH</sub>    | Output HIGH Voltage (Note 9)                                     | 3975 | 4050 | 4120 | 3975 | 4050 | 4120 | 3975 | 4050 | 4120 | mV   |

| V <sub>OL</sub>    | Output LOW Voltage (Note 9)                                      | 3190 | 3295 | 3380 | 3190 | 3255 | 3380 | 3190 | 3260 | 3380 | mV   |

| V <sub>IH</sub>    | Input HIGH Voltage (Single Ended)                                | 3835 | 4050 | 4120 | 3835 | 4120 | 4120 | 3835 | 4120 | 4120 | mV   |

| V <sub>IL</sub>    | Input LOW Voltage (Single Ended)                                 | 3190 | 3300 | 3525 | 3190 | 3525 | 3525 | 3190 | 3525 | 3525 | mV   |

| V <sub>BB</sub>    | Output Voltage Reference                                         | 3.62 |      | 3.74 | 3.62 |      | 3.74 | 3.62 |      | 3.74 | V    |

| V <sub>IHCMR</sub> | Input HIGH Voltage Common Mode<br>Range (Differential) (Note 10) |      | TBD  |      |      | TBD  |      |      | TBD  |      | V    |

| I <sub>IH</sub>    | Input HIGH Current                                               |      |      | 150  |      |      | 150  |      |      | 150  | μΑ   |

| I <sub>IL</sub>    | Input LOW Current                                                | 0.5  | 0.3  |      | 0.5  | 0.25 |      | 0.5  | 0.2  |      | μΑ   |

NOTE: Devices are designed to meet the DC specifications shown in the above table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained.

- 8. Input and output parameters vary 1:1 with  $V_{CC}$ .  $V_{EE}$  can vary +0.46 V / -0.8 V. 9. Outputs are terminated through a 50 ohm resistor to  $V_{CC}$ -2 volts.

- 10. V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, max varies 1:1 with V<sub>CC</sub>.

## 100E SERIES NECL DC CHARACTERISTICS $V_{CCx}$ = 0.0 V; $V_{EE}$ = -5.0 V (Note 11)

|                    |                                                                  |       | 0°C   |       | 25°C  |       |       |       |       |       |      |

|--------------------|------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol             | Characteristic                                                   | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub>    | Power Supply Current                                             |       | 130   | 156   |       | 130   | 156   |       | 150   | 179   | mA   |

| V <sub>OH</sub>    | Output HIGH Voltage (Note 12)                                    | -1025 | -950  | -880  | -1025 | -950  | -880  | -1025 | -950  | -880  | mV   |

| V <sub>OL</sub>    | Output LOW Voltage (Note 12)                                     | -1810 | -1705 | -1620 | -1810 | -1745 | -1620 | -1810 | -1740 | -1620 | mV   |

| V <sub>IH</sub>    | Input HIGH Voltage (Single Ended)                                | -1165 | -950  | -880  | -1165 | -880  | -880  | -1165 | -880  | -880  | mV   |

| V <sub>IL</sub>    | Input LOW Voltage (Single Ended)                                 | -1810 | -1700 | -1475 | -1810 | -1475 | -1475 | -1810 | -1475 | -1475 | mV   |

| V <sub>BB</sub>    | Output Voltage Reference                                         | -1.38 |       | -1.26 | -1.38 |       | -1.26 | -1.38 |       | -1.26 | V    |

| V <sub>IHCMR</sub> | Input HIGH Voltage Common Mode<br>Range (Differential) (Note 13) |       | TBD   |       |       | TBD   |       |       | TBD   |       | V    |

| I <sub>IH</sub>    | Input HIGH Current                                               |       |       | 150   |       |       | 150   |       |       | 150   | μΑ   |

| I <sub>IL</sub>    | Input LOW Current                                                | 0.5   | 0.3   |       | 0.5   | 0.25  |       | 0.5   | 0.2   |       | μΑ   |

NOTE: Devices are designed to meet the DC specifications shown in the above table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained.

11. Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary +0.46 V / -0.8 V.

12. Outputs are terminated through a 50 ohm resistor to V<sub>CC</sub>-2 volts.

13. V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, max varies 1:1 with V<sub>CC</sub>.

**AC CHARACTERISTICS**  $V_{CCx} = 5.0 \text{ V}$ ;  $V_{EE} = 0.0 \text{ V}$  or  $V_{CCx} = 0.0 \text{ V}$ ;  $V_{EE} = -5.0 \text{ V}$  (Note 14)

|                                      |                                                                                          |                                 | 0°C                                         |                                  |                                 | 25°C                                          |                                  |                                 | 85°C                                        |                                  |      |

|--------------------------------------|------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------|----------------------------------|---------------------------------|-----------------------------------------------|----------------------------------|---------------------------------|---------------------------------------------|----------------------------------|------|

| Symbol                               | Characteristic                                                                           | Min                             | Тур                                         | Max                              | Min                             | Тур                                           | Max                              | Min                             | Тур                                         | Max                              | Unit |

| f <sub>MAX</sub>                     | Maximum Toggle Frequency                                                                 |                                 | TBD                                         |                                  |                                 | >1.0                                          |                                  |                                 | TBD                                         |                                  | GHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay  IN to Q; Tap = 0  IN to Q; Tap = 127  EN to Q; Tap = 0  D7 to CASCADE | 1210<br>3320<br>1250<br>300     | 1360<br>3570<br>1450<br>450                 | 1510<br>3820<br>1650<br>700      | 1240<br>3380<br>1275<br>300     | 1390<br>3630<br>1475<br>450                   | 1540<br>3880<br>1675<br>700      | 1440<br>3920<br>1350<br>300     | 1590<br>4270<br>1650<br>450                 | 1765<br>4720<br>1950<br>700      | ps   |

| t <sub>RANGE</sub>                   | Programmable Range t <sub>PD</sub> (max) – t <sub>PD</sub> (min)                         | 2000                            | 2175                                        |                                  | 2050                            | 2240                                          |                                  | 2375                            | 2580                                        |                                  | ps   |

| Δt                                   | Step Delay (Note 20)  D0 High D1 High D2 High D3 High D4 High D5 High D6 High            | 55<br>115<br>250<br>505<br>1000 | 17<br>34<br>68<br>136<br>272<br>544<br>1088 | 105<br>180<br>325<br>620<br>1190 | 55<br>115<br>250<br>515<br>1030 | 17.5<br>35<br>70<br>140<br>280<br>560<br>1120 | 105<br>180<br>325<br>620<br>1220 | 65<br>140<br>305<br>620<br>1240 | 21<br>42<br>84<br>168<br>336<br>672<br>1344 | 120<br>205<br>380<br>740<br>1450 | ps   |

| Lin                                  | Linearity (Note 21)                                                                      | D1                              | D0                                          |                                  | D1                              | D0                                            |                                  | D1                              | D0                                          |                                  |      |

| tskew                                | Duty Cycle Skew t <sub>PHL</sub> -t <sub>PLH</sub> (Note 15)                             |                                 | ±30                                         |                                  |                                 | ±30                                           |                                  |                                 | ±30                                         |                                  | ps   |

| t <sub>JITTER</sub>                  | Cycle-to-Cycle Jitter                                                                    |                                 | TBD                                         |                                  |                                 | TBD                                           |                                  |                                 | TBD                                         |                                  | ps   |

| t <sub>s</sub>                       | Setup Time  D to LEN  D to IN (Note 16)  EN to IN (Note 17)                              | 200<br>800<br>200               | 0                                           |                                  | 200<br>800<br>200               | 0                                             |                                  | 200<br>800<br>200               | 0                                           |                                  | ps   |

| t <sub>h</sub>                       | Hold Time  LEN to D  IN to EN (Note 18)                                                  | 500<br>0                        | 250                                         |                                  | 500<br>0                        | 250                                           |                                  | 500<br>0                        | 250                                         |                                  | ps   |

| t <sub>R</sub>                       | Release Time  EN to IN (Note 19)  SET MAX to LEN  SET MIN to LEN                         | 300<br>800<br>800               |                                             |                                  | 300<br>800<br>800               |                                               |                                  | 300<br>800<br>800               |                                             |                                  | ps   |

| t <sub>jit</sub>                     | Jitter (Note 22)                                                                         |                                 | <5.0                                        |                                  |                                 | <5.0                                          |                                  |                                 | <5.0                                        |                                  | ps   |

| t <sub>r</sub><br>t <sub>f</sub>     | Output Rise/Fall Time<br>20–80% (Q)<br>20–80% (CASCADE)                                  | 125<br>300                      | 225<br>450                                  | 325<br>650                       | 125<br>300                      | 225<br>450                                    | 325<br>650                       | 125<br>300                      | 225<br>450                                  | 325<br>650                       | ps   |

<sup>14.10</sup> Series: V<sub>EE</sub> can vary +0.46 V / -0.06 V.

<sup>100</sup> Series: VEE can vary +0.46 V / -0.8 V.

<sup>15.</sup> Duty cycle skew guaranteed only for differential operation measured from the cross point of the input to the cross point of the output.

<sup>16.</sup> This setup time defines the amount of time prior to the input signal the delay tap of the device must be set.

<sup>17.</sup> This setup time is the minimum time that EN must be asserted prior to the next transition of IN/IN to prevent an output response greater than ±75 mV to that IN/IN transition.

<sup>18.</sup> This hold time is the minimum time that  $\overline{\text{EN}}$  must remain asserted after a negative going IN or positive going  $\overline{\text{IN}}$  to prevent an output response greater than  $\pm 75$  mV to that IN/IN transition.

<sup>19.</sup> This release time is the minimum time that EN must be de–asserted prior to the next IN/IN transition to ensure an output response that meets the specified IN to Q propagation delay and transition times.

<sup>20.</sup> Specification limits represent the amount of delay added with the assertion of each individual delay control pin. The various combinations of asserted delay control inputs will typically realize D0 resolution steps across the specified programmable range.

<sup>21.</sup> The linearity specification guarantees to which delay control input the programmable steps will be monotonic (i.e. increasing delay steps for increasing binary counts on the control inputs Dn). Typically the device will be monotonic to the D0 input, however under worst case conditions and process variation, delays could decrease slightly with increasing binary counts when the D0 input is the LSB. With the D1 input as the LSB the device is guaranteed to be monotonic over all specified environmental conditions and process variation.

<sup>22.</sup> The jitter of the device is less than what can be measured without resorting to very tedious and specialized measurement techniques.

#### **ANALOG INPUT CHARACTERISTICS**

Ftune =  $V_{CC}$  to  $V_{EE}$

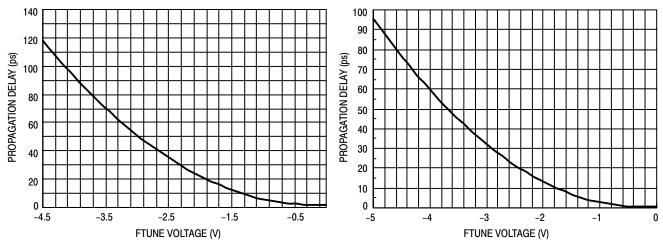

Propagation Delay versus Ftune Voltage (100E196)

Propagation Delay versus Ftune Voltage (10E196)

#### **USING THE FTUNE ANALOG INPUT**

The analog FTUNE pin on the E196 device is intended to add more delay in a tunable gate to enhance the 20 ps resolution capabilities of the fully digital E195. The level of resolution obtained is dependent on the number of increments applied to the appropriate range on the FTUNE pin.

To provide this further level of resolution (See Logic Diagram), the FTUNE pin must be capable of adjusting the additional delay finer than the 20 ps digital resolution. From the provided graphs one sees that this requirement is easily achieved as over the entire FTUNE voltage range a 100 ps additional delay can be achieved. This extra analog range ensures that the FTUNE pin will be capable even under worst case conditions of covering the digital resolution. Typically the analog input will be driven by an external DAC to provide a digital control with very fine analog output steps. The final resolution of the device will be dependent on the width of the DAC chosen.

To determine the voltage range necessary for the FTUNE input, the graphs provided should be used. As an example if a tuning range of 40 ps is selected to cover worst case conditions and ensure coverage of the digital range, from the 100E196 graph a voltage range of –3.25 V to –4.0 V would be necessary on the FTUNE pin. Obviously there are numerous voltage ranges which can be used to cover a given delay range, users are given the flexibility to determine which one best fits their designs.

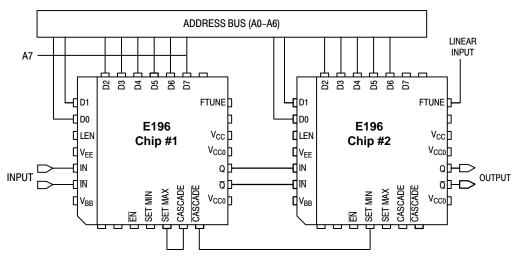

#### Cascading Multiple E196's

To increase the programmable range of the E196 internal cascade circuitry has been included. This circuitry allows for the cascading of multiple E196's without the need for any

external gating. Furthermore this capability requires only one more address line per added E196. Obviously cascading multiple PDC's will result in a larger programmable range, however, this increase is at the expense of a longer minimum delay.

Figure 3 illustrates the interconnect scheme for cascading two E196's. As can be seen, this scheme can easily be expanded for larger E196 chains. The D7 input of the E196 is the cascade control pin. With the interconnect scheme of Figure 3 when D7 is asserted it signals the need for a larger programmable range than is achievable with a single device.

An expansion of the latch section of the block diagram is pictured below. Use of this diagram will simplify the explanation of how the cascade circuitry works. When D7 of chip #1 above is low the cascade output will also be low while the cascade bar output will be a logical high. In this condition the SET MIN pin of chip #2 will be asserted and thus all of the latches of chip #2 will be reset and the device will be set at its minimum delay. Since the RESET and SET inputs of the latches are overriding any changes on the A0–A6 address bus will not affect the operation of chip #2.

Chip #1 on the other hand will have both SET MIN and SET MAX de-asserted so that its delay will be controlled entirely by the address bus A0–A6. If the delay needed is greater than can be achieved with 31.75 gate delays (1111111 on the A0–A6 address bus) D7 will be asserted to signal the need to cascade the delay to the next E196 device. When D7 is asserted the SET MIN pin of chip #2 will be de-asserted and the delay will be controlled by the A0–A6 address bus. Chip #1 on the other hand will have its SET

MAX pin asserted resulting in the device delay to be independent of the A0–A6 address bus.

When the SET MAX pin of chip #1 is asserted the D0 and D1 latches will be reset while the rest of the latches will be set. In addition, to maintain monotonicity an additional gate delay is selected in the cascade circuitry. As a result when D7 of chip #1 is asserted the delay increases from 31.75 gates

to 32 gates. A 32 gate delay is the maximum delay setting for the E196.

When cascading multiple PDC's it will prove more cost effective to use a single E196 for the MSB of the chain while using E195 for the lower order bits. This is due to the fact that only one fine tune input is needed to further reduce the delay step resolution.

Figure 3. Cascading Interconnect Architecture

Figure 4. Expansion of the Latch Section of the E196 Block Diagram

(sd) PROPAGATION DELAY Temperature (°C)

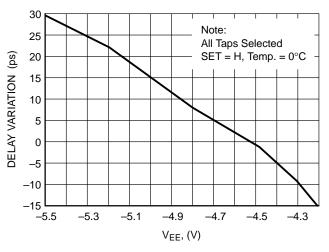

Figure 5. Change in Delay vs. Change in Supply Voltage

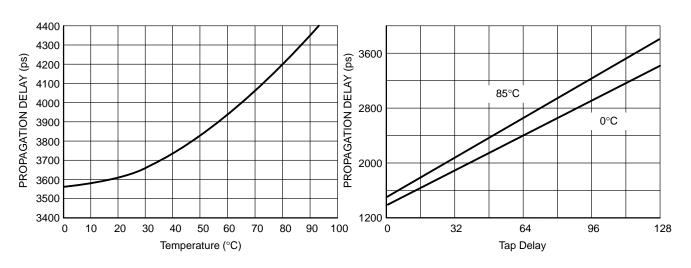

Figure 6. Delay vs. Temperature (Fixed Path)

Figure 7. Delay vs. Temperature (Max. Delay).

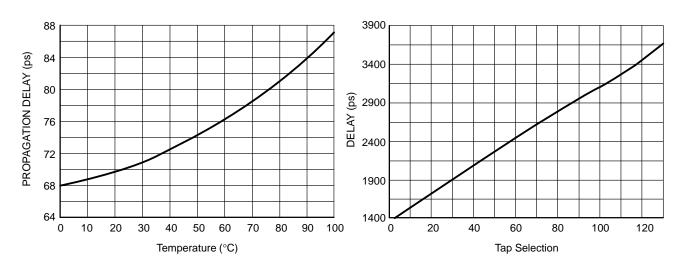

Figure 8. 100E195 Temperature Effects on Delay.

Figure 9. Delay vs. Temperature (Per Gate).

Figure 10. E195 Delay Linearity.

Figure 11. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020 – Termination of ECL Logic Devices.)

## **Resource Reference of Application Notes**

**AN1404** – ECLinPS Circuit Performance at Non–Standard  $V_{IH}$  Levels

AN1405 – ECL Clock Distribution Techniques

AN1406 – Designing with PECL (ECL at +5.0 V)

AN1503 – ECLinPS I/O SPICE Modeling Kit

AN1504 – Metastability and the ECLinPS Family

AN1568 – Interfacing Between LVDS and ECL

AN1596 - ECLinPS Lite Translator ELT Family SPICE I/O Model Kit

AN1650 - Using Wire-OR Ties in ECLinPS Designs

AND8001 - The ECL Translator Guide

AND8001 - Odd Number Counters Design

AND8002 - Marking and Date Codes

AND8020 - Termination of ECL Logic Devices

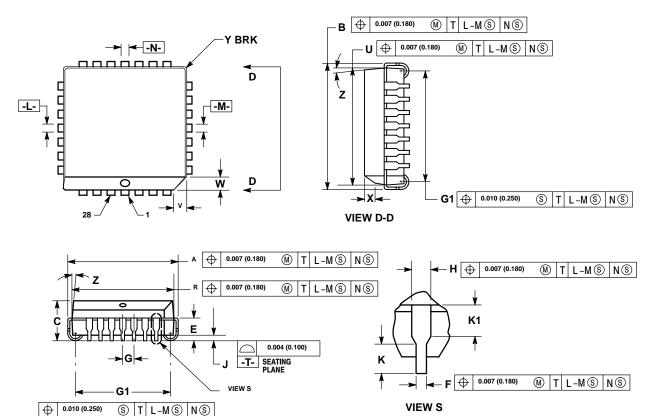

#### **PACKAGE DIMENSIONS**

#### PLCC-28 FN SUFFIX

PLASTIC PLCC PACKAGE CASE 776–02 ISSUE E

#### NOTES:

- DATUMS -L-, -M-, AND -N- DETERMINED

WHERE TOP OF LEAD SHOULDER EXITS

PLASTIC BODY AT MOLD PARTING LINE

- PLASTIC BODY AT MOLD PARTING LINE.

2. DIM G1, TRUE POSITION TO BE MEASURED

- AT DATUM -T., SEATING PLANE.

3. DIM R AND U DO NOT INCLUDE MOLD FLASH.

ALLOWABLE MOLD FLASH IS 0.010 (0.250)

PER SIDE

- DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M. 1982.

- Y14.5M, 1982. 5. CONTROLLING DIMENSION: INCH.

- 6. THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300). DIMENSIONS R AND U A REDETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, THE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

- PLASTIC BODY.

DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 (0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INC   | HES   | MILLIN | IETERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 0.485 | 0.495 | 12.32  | 12.57  |

| В   | 0.485 | 0.495 | 12.32  | 12.57  |

| С   | 0.165 | 0.180 | 4.20   | 4.57   |

| Е   | 0.090 | 0.110 | 2.29   | 2.79   |

| F   | 0.013 | 0.019 | 0.33   | 0.48   |

| G   | 0.05  | 0 BSC | 1.27   | BSC    |

| Н   | 0.026 | 0.032 | 0.66   | 0.81   |

| J   | 0.020 |       | 0.51   |        |

| K   | 0.025 | _     | 0.64   |        |

| R   | 0.450 | 0.456 | 11.43  | 11.58  |

| U   | 0.450 | 0.456 | 11.43  | 11.58  |

| ٧   | 0.042 | 0.048 | 1.07   | 1.21   |

| W   | 0.042 | 0.048 | 1.07   | 1.21   |

| Х   | 0.042 | 0.056 | 1.07   | 1.42   |

| Y   | _     | 0.020 | _      | 0.50   |

| Z   | 2°    | 10°   | 2°     | 10°    |

| G1  | 0.410 | 0.430 | 10.42  | 10.92  |

| K1  | 0.040 | _     | 1.02   |        |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax:** 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051

Phone: 81–3–5773–3850 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.