### **LP3947**

# USB/AC Adaptor, Single Cell Li-Ion Battery Charger IC

### **General Description**

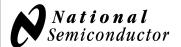

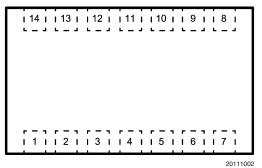

The LP3947 is a complete charge management system that safely charges and maintains a Li-Ion battery from either USB power source or AC adaptor. In USB mode, the LP3947 supports charging in low power or high power mode. Alternatively, the LP3947 can take charge from AC adaptor. In both USB and AC adaptor modes, charge current, battery regulation voltage, and End of Charge (EOC) point can be selected via I<sup>2</sup>C interface. The LP3947 can also operate on default values that are pre-programmed in the factory. The battery temperature is monitored continuously at the Ts pin to safeguard against hazardous charging conditions. The charger also has under-voltage and over-voltage protection as well as an internal 5.6 hr timer to protect the battery. The pass transistor and charge current sensing resistor are all integrated inside the LP3947.

The LP3947 operates in four modes: pre-qualification, constant current, constant voltage and maintenance modes. There are two open drain outputs for status indication. An internal amplifier readily converts the charge current into a voltage. Also, the charger can operate in an LDO mode providing a maximum of 1.2 Amp to the load.

#### **Features**

- Supports USB Charging Scheme

- Integrated Pass Transistor

- Near-Depleted Battery Preconditioning

- Monitors Battery Temperature

- Built-In 5.6 hour timer

- Under Voltage and Over Voltage Lockout

- Charge Status Indicators

- Charge Current Monitor Analog Output

- LDO Mode Operation can source 1 Amp

- Continuous Over Current/Temperature Protection

### **Key Specifications**

- 1% Charger Voltage Accuracy Over 0°C ≤ T<sub>.1</sub> ≤ 85°C

- 4.3V to 6.0V Input Voltage Range

- 100 mA to 750 mA charge current range, in charger mode

- 100mA to 500mA charge current range, in USB mode

- LLP Package Power Dissipation: 2.7W at T<sub>A</sub> = 25°C

### **Applications**

- Cellular Phones

- PDAs

- Digital Cameras

- USB Powered Devices

- Programmable Current Sources

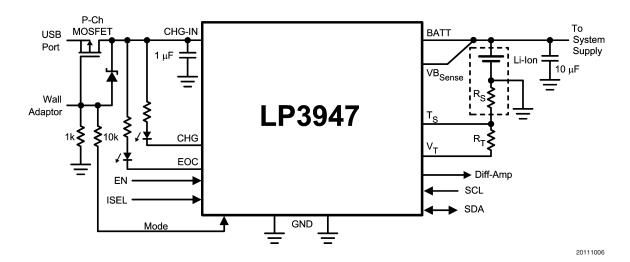

## **Typical Application Circuit**

More Application Circuit can be found in the Application Note section.

20111001

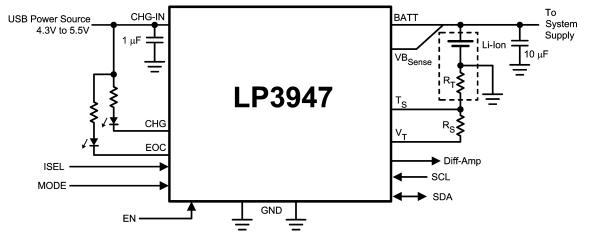

# **Connection Diagrams and Package Mark Information**

(Top View) See NS Package Number SDA14B

## **Pin Description**

| Pin # | Name                | Description                                                                                                                                                                                                                                   |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | EN                  | Charger Enable Input. Internally pulled high to CHG-IN pin. A HIGH enables the charger and a LOW disables the charger.                                                                                                                        |

| 2     | SCL                 | I <sup>2</sup> C serial Interface Clock input.                                                                                                                                                                                                |

| 3     | SDA                 | I <sup>2</sup> C serial Interface Data input/out.                                                                                                                                                                                             |

| 4     | BATT                | Battery supply input terminal. Must have 10 µF ceramic capacitor to GND                                                                                                                                                                       |

| 5     | V <sub>T</sub>      | Regulated 2.78V output used for biasing the battery temperature monitoring thermistor.                                                                                                                                                        |

| 6     | VB <sub>SENSE</sub> | Battery Voltage Sense connected to the positive terminal of the battery.                                                                                                                                                                      |

| 7     | MODE                | Select pin between AC adaptor and USB port. A LOW sets the LP3947 in USB port and a HIGH sets it in the AC adaptor.                                                                                                                           |

| 8     | Diff-Amp            | Charge current monitoring differential amplifier output. Voltage output representation of the charge current.                                                                                                                                 |

| 9     | Ts                  | Multi function pin. Battery temperature monitoring input and LDO/Charger mode.  Pulling this pin to V <sub>T</sub> , or removing the thermistor by physically disconnecting the battery, sets the device in LDO mode.                         |

| 10    | EOC                 | Active Low Open Drain Output. Active when USB port or AC adaptor is connected and battery is fully charged. For more information, refer to "LED Charge Status Indicators" section.                                                            |

| 11    | GND                 | Ground                                                                                                                                                                                                                                        |

| 12    | CHG                 | Active Low Open Drain Output. Active when USB port or AC adaptor is connected and battery is being charged. For more information, refer to "LED Charge Status Indicators" section.                                                            |

| 13    | ISEL                | Control pin to switch between low power (100 mA) mode and high power (500 mA) mode in USB mode. This pin is pulled high internally as default to set the USB in 100 mA mode. This pin has to be externally pulled low to go into 500 mA mode. |

| 14    | CHG-IN              | Charger input from a regulated, current limited power source. Must have a 1 µF ceramic capacitor to GND                                                                                                                                       |

# **Ordering Information**

| LP3947<br>Supplied as 1000 Units,<br>Tape and Reel | LP3947<br>Supplied as 4500 Units<br>Tape and Reel | Default<br>Options*                                       | Package<br>Marking |

|----------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------|--------------------|

| LP3947ISD-09                                       | LP3947ISDX-09                                     | $I_{CHG}$ = 500 mA<br>$V_{BATT}$ = 4.1V<br>EOC = 0.1C     | L00055B            |

| LP3947ISD-51                                       | LP3947ISDX-51                                     | $I_{CHG} = 500 \text{ mA}$ $V_{BATT} = 4.2V$ $EOC = 0.1C$ | L00056B            |

<sup>\*</sup>Other default options are available. Please contact National Semiconductor sales office/distributors for availability and specifications.

# LP3947 Functional Block Diagram

### **Absolute Maximum Ratings** (Notes 1,

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

CHG-IN -0.3V to +6.5V

All pins except GND and CHG-IN

(Note 3) -0.3V to +6V

Junction Temperature 150°C

Storage Temperature -40°C to +150°C

Power Dissipation (Note 4) 1.89W

ESD (Note 5)

Human Body Model 2 kV Machine Model 200V

### Operating Ratings (Notes 1, 2)

CHG-IN 0.3V to 6.5V

EN, ISEL, MODE, SCL, SDA,

$V_T$  (Note 3) 0V to 6V Junction Temperature  $-40^{\circ}$ C to  $+125^{\circ}$ C Operating Temperature  $-40^{\circ}$ C to  $+85^{\circ}$ C

Thermal Resistance  $\theta_{JA}$  37°C/W Maximum Power Dissipation 1.21W

(Note 6)

### **Electrical Characteristics**

Unless otherwise noted,  $V_{CHG-IN} = 5V$ ,  $V_{BATT} = 4V$ ,  $C_{CHG-IN} = 1 \mu F$ ,  $C_{BATT} = 10 \mu F$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40^{\circ}C$  to  $+85^{\circ}C$ . (Notes 7, 8, 9)

| Symbol                 | Parameter                            | Conditions                                                              | Тур  | Li    | Units |                                         |  |

|------------------------|--------------------------------------|-------------------------------------------------------------------------|------|-------|-------|-----------------------------------------|--|

| Зуппоот                | Farameter                            | ТУР                                                                     | Min  | Max   | Units |                                         |  |

| V <sub>CC</sub> SUPPL  | Υ                                    |                                                                         |      |       |       |                                         |  |

| V <sub>CHG-IN</sub>    | Input Voltage Range                  |                                                                         |      | 4.5   | 6     | V                                       |  |

| V <sub>USB</sub>       |                                      |                                                                         |      | 4.3   | 6     | 7 V                                     |  |

| I <sub>cc</sub>        | Quiescent Current                    | $V_{CHG-IN} \le 4V$                                                     | 2    |       | 20    |                                         |  |

|                        |                                      | EOC = Low, adaptor connected,<br>V <sub>BATT</sub> = 4.1V               | 50   |       | 150   | μA                                      |  |

| V <sub>OK-TSHD</sub>   | Adaptor OK Trip Point (CHG-IN)       | V <sub>CHG-IN</sub> –V <sub>BATT</sub> (Rising)                         | 60   |       |       | mV                                      |  |

|                        |                                      | V <sub>CHG-IN</sub> -V <sub>BATT</sub> (Falling)                        | 50   |       |       | mV                                      |  |

| V <sub>UVLO-TSHD</sub> | Under Voltage Lock-Out Trip Point    | V <sub>CHG-IN</sub> (Rising)                                            | 3.95 | 3.6   | 4.3   | V                                       |  |

|                        |                                      | V <sub>CHG-IN</sub> (Falling)                                           | 3.75 | 3.4   | 4.1   | V                                       |  |

| V <sub>OVLO-TSHD</sub> | Over Voltage Lock-Out Trip Point     | V <sub>CHG-IN</sub> (Rising)                                            | 5.9  |       |       | V                                       |  |

|                        |                                      | V <sub>CHG-IN</sub> (Falling)                                           | 5.7  |       |       | 7 V                                     |  |

|                        | Thermal Shutdown Temperature         | (Note 8)                                                                | 160  |       |       | • • • • • • • • • • • • • • • • • • • • |  |

|                        | Thermal Shutdown Hysteresis          |                                                                         | 20   |       |       | °C                                      |  |

| BATTERY C              | HARGER                               |                                                                         |      |       |       | •                                       |  |

| I <sub>CHG</sub>       | Fast Charge Current Range            | ISEL = High, In USB Mode                                                | 100  |       |       |                                         |  |

|                        |                                      | ISEL = Low, In USB Mode                                                 | 500  |       |       | mA                                      |  |

|                        |                                      | In AC Adaptor Mode                                                      |      | 100   | 750   |                                         |  |

|                        | Fast Charge Current Accuracy         | I <sub>CHARGE</sub> = 100 mA or 150 mA                                  |      | -20   | +20   | mA                                      |  |

|                        |                                      | I <sub>CHARGE</sub> ≥ 200 mA                                            |      | -10   | +10   | %                                       |  |

| I <sub>PRE-CHG</sub>   | Pre-Charge Current                   | V <sub>BATT</sub> = 2V                                                  |      | 45    | 70    | mA                                      |  |

| I <sub>EOC</sub>       | End of Charge Current Accuracy       | 100 mA to 450 mA, 0.1C EOC Only (Note 10)                               |      | -10   | +10   | mA                                      |  |

|                        |                                      | 500 mA to 750 mA, All EOC Points                                        |      | -20   | +20   | %                                       |  |

| V <sub>BATT</sub>      | Battery Regulation Voltage (For 4.1V | $T_J = 0^{\circ}C \text{ to } +85^{\circ}C$                             | 4.1  | 4.059 | 4.141 |                                         |  |

|                        | Cell)                                | $T_J = -40^{\circ}C \text{ to } +85^{\circ}C$                           | 4.1  | 4.038 | 4.162 | ] ,,                                    |  |

|                        | Battery Regulation Voltage (For 4.2V | $T_J = 0^{\circ}C \text{ to } +85^{\circ}C$                             | 4.1  | 4.158 | 4.242 | _ V                                     |  |

|                        | Cell)                                | $T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                     | 4.2  | 4.137 | 4.263 |                                         |  |

| V <sub>CHG-Q</sub>     | Full Charge Qualification Threshold  | V <sub>BATT</sub> Rising, Transition from<br>Pre-Charge to Full Current | 3.0  |       |       | V                                       |  |

### **Electrical Characteristics** (Continued)

Unless otherwise noted,  $V_{CHG-IN} = 5V$ ,  $V_{BATT} = 4V$ ,  $C_{CHG-IN} = 1~\mu F$ ,  $C_{BATT} = 10~\mu F$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40^{\circ}C$  to +85°C. (Notes 7, 8, 9)

| Symbol               | Parameter                                    | Conditions                                                                 | Typ   | Li   | Units |       |  |

|----------------------|----------------------------------------------|----------------------------------------------------------------------------|-------|------|-------|-------|--|

| Syllibol             | Farameter                                    | Conditions                                                                 | Тур   | Min  | Max   |       |  |

| BATTERY (            | CHARGER                                      |                                                                            |       |      |       | •     |  |

| V <sub>BAT-RST</sub> | Restart Threshold Voltage<br>(For 4.1V Cell) |                                                                            |       | 3.77 | 4.02  |       |  |

|                      | Restart Threshold Voltage<br>(For 4.2V Cell) | V <sub>BATT</sub> Falling, Transition from EOC, to Pre-Qualification State | 4.00  | 3.86 | 4.12  | - V   |  |

| R <sub>SENSE</sub>   | Internal Current Sense Resistance            | (Note 8)                                                                   | 120   |      |       | mΩ    |  |

|                      | Internal Current Sense Resistor Load Current |                                                                            |       |      | 1.2   | А     |  |

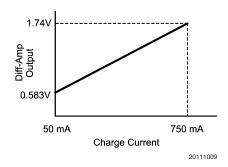

| ICHG <sub>MON</sub>  | Diff-Amp Output                              | I <sub>CHG</sub> = 50 mA                                                   | 0.583 |      |       |       |  |

|                      |                                              | I <sub>CHG</sub> = 100 mA                                                  | 0.663 |      |       | \ \ \ |  |

|                      |                                              | I <sub>CHG</sub> = 750 mA                                                  | 1.790 |      |       | 7     |  |

| t <sub>OUT</sub>     | Charger Time Out                             | $T_J = 0^{\circ}C \text{ to } 85^{\circ}C$                                 | 5.625 | 4.78 | 6.42  | Hrs   |  |

|                      |                                              | $T_J = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                        | 5.625 | 4.5  | 6.75  | HIS   |  |

| V <sub>OL</sub>      | Low Level Output Voltage                     | EOC, CHG Pins each at 9 mA                                                 | 100   |      |       | mV    |  |

| TEMPERAT             | TURE SENSE COMPARATORS                       |                                                                            |       |      |       | •     |  |

| $V_{\rm UTLO}$       | Low Voltage Threshold                        | Voltage at Ts Pin, Rising                                                  | 2.427 |      |       | V     |  |

|                      |                                              | Voltage at Ts Pin, Falling                                                 | 2.369 |      |       | 7 °   |  |

| V <sub>OTLO</sub>    | High Voltage Threshold                       | Voltage at Ts Pin, Rising                                                  | 1.470 |      |       | V     |  |

|                      |                                              | Voltage at Ts Pin, Falling                                                 | 1.390 |      |       | 7 °   |  |

| $V_{LDO}$            | LDO Mode Voltage Threshold                   | Voltage at Ts Pin, % of V <sub>T</sub>                                     | 97    |      |       | %     |  |

| V <sub>T</sub>       | Voltage Output                               |                                                                            | 2.787 |      |       | V     |  |

| LDO MODE             | (Ts = HIGH)                                  |                                                                            |       |      |       | •     |  |

| V <sub>OUT</sub>     | Output Voltage Regulation                    | I <sub>LOAD</sub> = 50 mA                                                  | 4.10  |      |       | V     |  |

|                      |                                              | $I_{LOAD} = 750 \text{ mA}$                                                | 4.06  |      |       | \ \ \ |  |

| LOGIC LEV            | /ELS                                         |                                                                            |       |      |       |       |  |

| V <sub>IL</sub>      | Low Level Input Voltage                      | EN, ISEL, MODE                                                             |       |      | 0.4   | V     |  |

| V <sub>IH</sub>      | High Level Input Voltage                     | EN, ISEL, MODE                                                             |       | 2.0  |       | V     |  |

| I <sub>IL</sub>      | Input Current                                | EN, ISEL = LOW                                                             |       | -10  | +10   | μA    |  |

|                      |                                              | MODE = LOW                                                                 |       | -5   | +5    | μΑ    |  |

| I <sub>IH</sub>      | Input Current                                | EN, ISEL, MODE = HIGH                                                      |       | -5   | +5    | μΑ    |  |

## Electrical Characteristics, I<sup>2</sup>C Interface

Unless otherwise noted,  $V_{CHG-IN} = V_{DD} = 5V$ ,  $V_{BATT} = 4V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ . (Notes 7, 8, 9)

| Cumbal              | Davameter                          | Conditions         | Turn | Li                  | Units                |       |

|---------------------|------------------------------------|--------------------|------|---------------------|----------------------|-------|

| Symbol              | Parameter                          | Conditions         | Тур  | Min                 | Max                  | Units |

| V <sub>IL</sub>     | Low Level Input Voltage            | SDA & SCL (Note 8) |      | 0.4                 | 0.3 V <sub>DD</sub>  | V     |

| V <sub>IH</sub>     | High Level Input Voltage           | SDA & SCL (Note 8) |      | 0.7 V <sub>DD</sub> | V <sub>DD</sub> +0.5 | V     |

| V <sub>OL</sub>     | Low Level Output Voltage           | SDA & SCL (Note 8) |      | 0                   | 0.2 V <sub>DD</sub>  | V     |

| V <sub>HYS</sub>    | Schmitt Trigger Input Hysteresis   | SDA & SCL (Note 8) |      | 0.1 V <sub>DD</sub> |                      | V     |

| F <sub>CLK</sub>    | Clock Frequency                    | (Note 8)           |      |                     | 400                  | kHz   |

| t <sub>HOLD</sub>   | Hold Time Repeated START Condition | (Note 8)           |      | 0.6                 |                      | μs    |

| t <sub>CLK-LP</sub> | CLK Low Period                     | (Note 8)           |      | 1.3                 |                      | μs    |

| t <sub>CLK-HP</sub> | CLK High Period                    | (Note 8)           |      | 0.6                 |                      | μs    |

### Electrical Characteristics, I<sup>2</sup>C Interface (Continued)

Unless otherwise noted,  $V_{CHG-IN} = V_{DD} = 5V$ ,  $V_{BATT} = 4V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40^{\circ}C$  to +125°C. (Notes 7, 8, 9)

| Symbol                 | Parameter                            | Conditions | Turn | Liı | Units |       |

|------------------------|--------------------------------------|------------|------|-----|-------|-------|

| Syllibol               | Farameter                            | Conditions | Тур  | Min | Max   | Units |

| t <sub>su</sub>        | Set-Up Time Repeated START Condition | (Note 8)   |      | 0.6 |       | μs    |

| t <sub>DATA-HOLD</sub> | Data Hold Time                       | (Note 8)   |      | 300 |       | ns    |

| t <sub>DATA-SU</sub>   | Data Set-Up Time                     | (Note 8)   |      | 100 |       | ns    |

| t <sub>SU</sub>        | Set-Up Time for STOP Condition       | (Note 8)   |      | 0.6 |       | μs    |

| t <sub>TRANS</sub>     | Maximum Pulse Width of Spikes that   | (Note 8)   |      |     |       |       |

|                        | must be Suppressed by the Input      |            | 50   |     |       | ns    |

|                        | Filter of both DATA & CLK Signals.   |            |      |     |       |       |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: Caution must be taken to avoid raising pins EN and V<sub>T</sub> 0.3V higher than V<sub>CHG-IN</sub> and raising pins ISEL, MODE, SCL and SDA 0.3V higher than V<sub>BATT</sub>.

Note 4: The Absolute Maximum power dissipation depends on the ambient temperature and can be calculated using the formula

$$P = (T_J - T_A)\theta_{JA},\tag{1}$$

where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance. The 1.89W rating appearing under Absolute Maximum Ratings results from substituting the Absolute Maximum junction temperature, 150°C, for  $T_J$ , 80°C for  $T_A$ , and 37°C/W for  $\theta_{JA}$ . More power can be dissipated safely at ambient temperatures above 80°C. The Absolute Maximum power dissipation can be increased by 27 mW for each degree below 80°C, and it must be de-rated by 27 mW for each degree above 80°C.

Note 5: The human-body model is used. The human-body model is 100 pF discharged through 1.5 k $\Omega$ .

**Note 6:** Like the Absolute Maximum power dissipation, the maximum power dissipation for operation depends on the ambient temperature. The 1.21W rating appearing under Operating Ratings results from substituting the maximum junction temperature for operation, 125°C, for  $T_J$ , 80°C for  $T_A$ , and 37°C/W for  $\theta_{JA}$  into (1) above. More power can be dissipated at ambient temperatures below 80°C. Less power can be dissipated at ambient temperatures above 80°C. The maximum power dissipation for operation can be increased by 27 mW for each degree below 80°C, and it must be de-rated by 27 mW for each degree above 80°C.

Note 7: All limits are guaranteed. All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are guaranteed by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Note 8: Guaranteed by design.

Note 9: LP3947 is not intended as a Li-lon battery protection device, any battery used in this application should have an adequate internal protection.

Note 10: The ±10 mA limits apply to all charge currents from 100 mA to 450 mA, to 0.1C End Of Charge (EOC). The limits increase proportionally with higher EOC points. For example, at 0.2C, the End Of Charge current accuracy becomes ±20 mA.

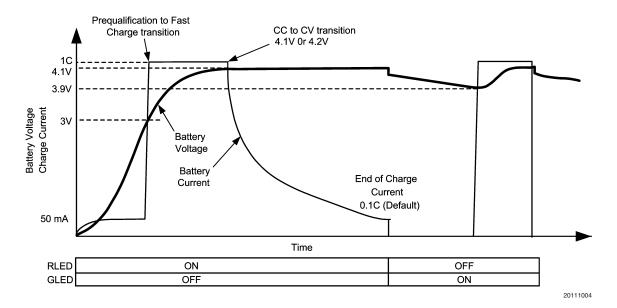

FIGURE 1. Li-Ion Charging Profile

### **Application Notes**

#### **LP3947 CHARGER OPERATION**

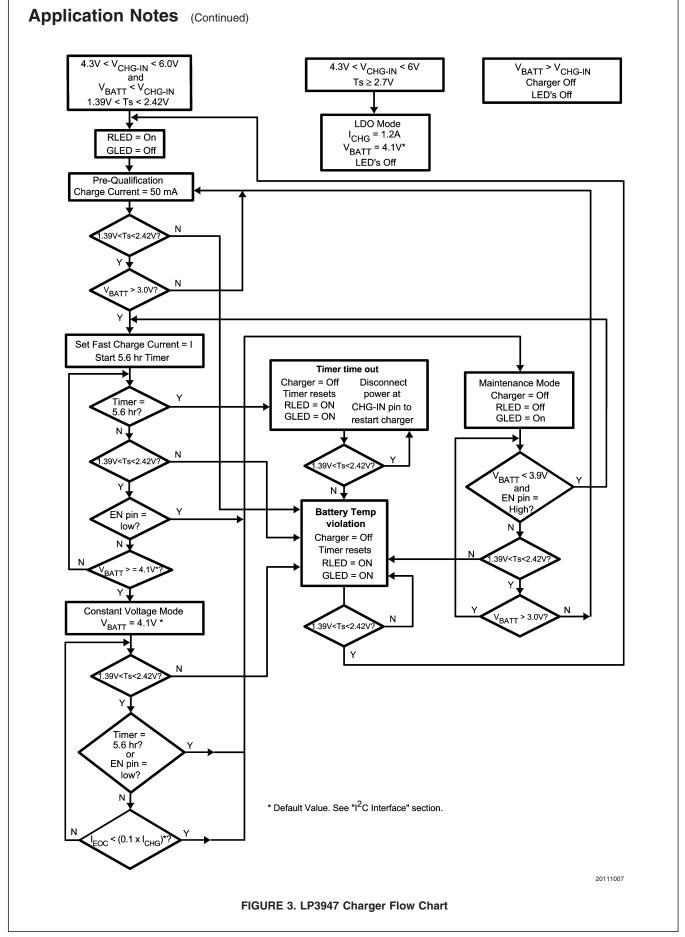

The LP3947 charge cycle is initiated with AC adaptor or USB power source insertion. If the voltage on the CHG-IN pin meets under-voltage (V<sub>UVLO-TSHD</sub>), over-voltage (V<sub>OVLO-TSHD</sub>) requirements, and the Adaptor OK signal is detected, then pre-qualification cycle begins (see *Figure 1*). In this cycle, a safe current level, less than 70mA, is pumped into the battery while the voltage across the battery terminals is measured. Once this voltage exceeds 3.0V, the controller will initiate constant current fast charge cycle. If the CHG-IN pin is connected to an AC adaptor, the default charge current is 500 mA and I<sup>2</sup>C interface can be used to program this parameter. If the CHG-IN pin is connected to the USB port, constant current cycle will start with a default of 100 mA. During this cycle, the 5.6 hr safety timer starts counting.

If the 5.6 hr safety timers times out during constant current cycle, charging is terminated. As the battery is charged during constant current mode, the voltage across pack terminal increases until it reaches 4.2V (or 4.1V). As soon as pack terminal reaches 4.2V (or 4.1V), the controller starts operating in constant voltage mode by applying regulated

$V_{\rm BATT}$  voltage across the battery terminals. During this cycle, the charge current,  $I_{\rm CHG},$  continues to decrease with time and when it drops below 0.1C (default value), the EOC signal is activated indicating successful completion of the charge cycle. The EOC current can be programmed to 0.1C, 0.15C, or 0.2C. The default value is 0.1C. After completing the full charge cycle, the controller will start the maintenance cycle where battery pack voltage is monitored continuously. During the maintenance cycle, if the pack voltage drops 200 mV below the termination voltage, charge cycle will be initiated providing that the wall adaptor is plugged in and is alive.

Charging terminates when the battery temperature is out of range. For more explanation, please refer to "Ts Pin" section.

The LP3947 with I<sup>2</sup>C interface allows maximum flexibility in selecting the charge current, battery regulation voltage and EOC current. The LP3947 operates in default mode during power up. See the "I<sup>2</sup>C Interface" section for more detail.

When charging source comes from the USB port, charging starts with 100 mA (low power mode, ISEL = high). The USB controller can set the ISEL pin low to charge the battery at 500 mA. A simple external circuit selects between an AC adaptor or the USB port. The circuit is designed with priority given to the AC adaptor.

FIGURE 2. LP3947 with External Switch

# CHARGE CURRENT SELECTION IN CONSTANT CURRENT MODE

In the AC adaptor mode, the LP3947 is designed to provide a charge current ranging from 100 mA to 750 mA, in steps of 50 mA, to support batteries with different capacity ratings. The default value is 500 mA. No external resistor is required

to set the charge current in the LP3947. In the USB mode, the LP3947 will initially charge with 100 mA (ISEL = high). By setting the ISEL pin low, charge current can be programmed to 500 mA. In addition, with ISEL = low, the charge current can be programmed to different values via the I<sup>2</sup>C interface.

TABLE 1. Charge Current Selection in AC Adaptor/USB Mode

|                 | MODE Pin | ISEL Pin | Functions                                                                |

|-----------------|----------|----------|--------------------------------------------------------------------------|

| AC Adaptor Mode | HIGH     | HIGH     | ISEL polarity is irrelevant. Default 500 mA charge current. Can be       |

|                 | HIGH     | LOW      | reprogrammed via I <sup>2</sup> C.                                       |

| USB Mode        | LOW      | HIGH     | 100 mA charge current                                                    |

|                 | LOW      | LOW      | Default 500 mA charge current. Can be reprogrammed via I <sup>2</sup> C. |

#### **BATTERY VOLTAGE SELECTION**

The battery voltage regulation can be set to 4.1V or 4.2V by default. Please refer to the Ordering Information table for more detail.

#### **END OF CHARGE (EOC) CURRENT SELECTION**

The EOC thresholds can be programmed to 0.1C, 0.15C or 0.2C in the LP3947. The default value is 0.1C, which provides the highest energy storage, but at the expense of longer charging time. On the other hand, 0.2C takes the least amount of charging time, but yields the least energy storage.

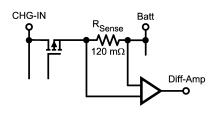

#### **CHARGE CURRENT SENSE DIFFERENTIAL AMPLIFIER**

The charge current is monitored across the internal 120 m $\Omega$  current sense resistor. The differential amplifier provides the analog representation of the charge current. Charge current can be calculated using the following equation:

$$I_{CHG} = \frac{(V_{DIFF} - 0.497)}{1.655}$$

Where voltage at Diff Amp output ( $V_{\rm DIFF}$ ) is in volt, and charge current ( $I_{\rm CHG}$ ) is in amps.

FIGURE 4. Charge Current Monitoring Circuit (Diff-Amp)

Monitoring the Diff Amp output during constant voltage cycle can provide an accurate indication of the battery charge status and time remaining to EOC. This feature is particularly useful during constant voltage mode. The current sense circuit is operational in the LDO mode as well. It can be used to monitor the system current consumption during testing.

#### LED CHARGE STATUS INDICATORS

The LP3947 is equipped with two open drain outputs to drive a green LED and a red LED. These two LEDs work together in combinations to indicate charge status or fault conditions. *Table 2* shows all the conditions.

**TABLE 2. LED Indicator Summary**

|                                                        | RED LED<br>(CHG) | GREEN LED<br>(EOC) |

|--------------------------------------------------------|------------------|--------------------|

| Charger Off                                            | OFF              | OFF                |

| Charging Li Ion Battery*                               | ON               | OFF                |

| Maintenance Mode                                       | OFF              | ON                 |

| Charging Li Ion Battery after Passing Maintenance Mode | OFF              | ON                 |

| EN Pin = LOW                                           | OFF              | ON                 |

| LDO Mode                                               | OFF              | OFF                |

| 5.6 Hr Safety Timer Flag/Battery Temperature Violation | ON               | ON                 |

<sup>\*</sup> Charging Li Ion battery for the first time after V<sub>CHG-IN</sub> insertion.

#### Ts PIN

The LP3947 continuously monitors the battery temperature by measuring the voltage between the Ts pin and ground. Charging stops if the battery temperature is outside the permitted temperature range set by the battery's internal thermistor  $R_{\rm T}$  and the external bias resistor  $R_{\rm S}$ . A 1% precision resistor should be used for  $R_{\rm S}$ . A curve 2 type thermistor is recommended for  $R_{\rm T}$ . The voltage across  $R_{\rm T}$  is proportional to the battery temperature. If the battery temperature is outside of the range during the charge cycle, the LP3947 will suspend charging. As an example, for a temperature range of 0°C to 50°C, a 10k $\Omega$  for the thermistor and a 4.1k $\Omega$  for  $R_{\rm S}$  should be used. When battery temperature returns to the permitted range, charging resumes from the beginning of the flow chart and the 5.6 hr safety timer is reset. Refer to Figure 3. LP3947 Charger Flow Chart for more information.

In absence of the thermistor, Ts pin will be pulled high to VT and the LP3947 goes into LDO mode. In this mode, the internal power FET provides up to 1.2 amp of current at the BATT pin. The LDO output is set to 4.1V or 4.2V, depending on the programmed battery regulation voltage. When operating at higher output currents, care must be taken not to exceed the package power dissipation rating. See "Thermal Performance of LLP Package" section for more detail.

#### Charger Status in Relation to Ts Voltage

| Voltage on the Ts Pin | Charger Status |

|-----------------------|----------------|

| Ts ≥ 2.7V             | LDO Mode       |

| Voltage on the Ts Pin | Charger Status |

|-----------------------|----------------|

| 2.427v ≤ Ts < 2.7V    | Charger Off    |

| 0V ≤ Ts ≤ 1.39V       |                |

| 1.39V < Ts < 2.427V   | Charger On     |

#### LDO MODE

The charger is in the LDO mode when the Ts pin is left floating. This mode of operation is used primarily during system level testing of the handset to eliminate the need for battery insertion. **CAUTION:** battery may be damaged if device is operating in LDO mode with battery connected.

The internal power FET provides up to 1.2 amp of current at BATT pin in this mode. The LDO output is set to 4.1V. When operating at higher output currents, care must be taken not to exceed the package power dissipation rating. See "Thermal Performance of LLP Package" section for more detail.

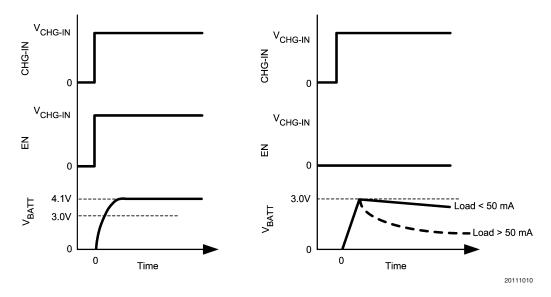

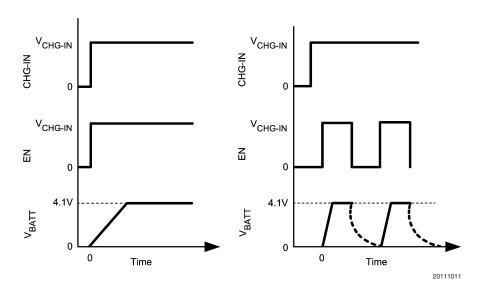

#### **EN PIN**

The Enable pin is used to enable/disable the charger, in both the charger mode and the LDO mode, see *Figures 5, 6*. The enable pin is internally pulled HIGH to the CHG-IN pin. When the charger is disabled, it draws less than  $4 \mu A$  of current.

FIGURE 5. Power Up Timing Diagram in Charger Mode (1.39V < Ts < 2.427V)

FIGURE 6. Power Up Timing Diagram in LDO Mode (Ts  $\geq$  2.7V)

#### **MODE PIN**

The mode pin toggles the LP3947 between the AC adaptor mode and the USB mode. When CHG-IN is connected to a USB port, this pin must be set low. When CHG-IN is connected to an AC adaptor, this pin must be tied high to either the BATT pin or to the wall adaptor input. Caution: MODE pin should never be tied to CHG-IN pin directly, as it will turn on an internal diode.

#### 5.6 HR SAFETY TIMER IN CHARGER MODE

The LP3947 has a built-in 5.6 hr back up safety timer to prevent over-charging a Li lon battery. The 5.6 hr timer starts counting when the charger enters the constant current

mode. It will turn the charger off when the 5.6 hr timer is up while the charger is still in constant current mode. In this case, both LEDs will turn on, indicating a fault condition.

When the battery temperature is outside the specified temperature range, the 5.6 hr safety timer will reset upon recovery of the battery temperature.

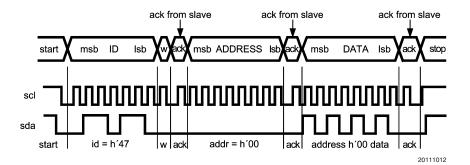

#### I<sup>2</sup>C INTERFACE

$I^2C$  interface is used in the LP3947 to program various parameters as shown in *Table 3*. The LP3947 operates on default settings following power up. Once programmed, the LP3947 retains the register data as long as the battery voltage is above 2.85V.

TABLE 3. LP3947 Serial Port Communication address code 7h'47

| LP3947 Control and Data Codes |             |   |   |   |              |            |            |            |            |

|-------------------------------|-------------|---|---|---|--------------|------------|------------|------------|------------|

| Addrs                         | Register    | 7 | 6 | 5 | 4            | 3          | 2          | 1          | 0          |

| 8'h00                         | Charger     |   |   |   | Batt Voltage | AC Adaptor | AC Adaptor | AC Adaptor | AC Adaptor |

|                               | Register -1 |   |   |   | (0) = 4.1V   | Charge     | Charge     | Charge     | Charge     |

|                               |             |   |   |   | 1 = 4.2V     | Current    | Current    | Current    | Current    |

|                               |             |   |   |   |              | Code 3     | Code 2     | Code 1     | Code 0     |

|                               |             |   |   |   |              | (1)        | (0)        | (0)        | (0)        |

| 8'h01                         | Charger     |   |   |   | EOC          | Charging   | EOC        | EOC        |            |

|                               | Register -2 |   |   |   | (Green LED)  | (Red LED)  | SEL-1      | SEL-0      |            |

|                               |             |   |   |   | R/O          | R/O        | (0)        | (1)        |            |

| 8'h02                         | Charger     |   |   |   |              | USB        | USB        | USB        | USB        |

|                               | Register -3 |   |   |   |              | Charge     | Charge     | Charge     | Charge     |

|                               |             |   |   |   |              | Current    | Current    | Current    | Current    |

|                               |             |   |   |   |              | Code 3     | Code 2     | Code 1     | Code 0     |

|                               |             |   |   |   |              | (1)        | (0)        | (0)        | (0)        |

Numbers in parentheses indicate default setting. "0" bit is set to low state, and "1" bit is set to high state. R/O -Read Only, All other bits are Read and Write.

TABLE 4. Charger Current and EOC Current Programming Code

| Data Code | Charger Current<br>Selection Code I <sub>SET</sub> (mA) | End of Charge Current<br>Selection Code |

|-----------|---------------------------------------------------------|-----------------------------------------|

| 4h'00     | 100                                                     |                                         |

| 4h'01     | 150                                                     | 0.1C                                    |

| 4h'02     | 200                                                     | 0.15C                                   |

| 4h'03     | 250                                                     | 0.2C                                    |

| 4h'04     | 300                                                     |                                         |

| 4h'05     | 350                                                     |                                         |

| 4h'06     | 400                                                     |                                         |

| 4h'07     | 450                                                     |                                         |

| 4h'08     | 500                                                     |                                         |

| 4h'09     | 550                                                     |                                         |

| 4h'0A     | 600                                                     |                                         |

| 4h'0B     | 650                                                     |                                         |

| 4h'0C     | 700                                                     |                                         |

| 4h'0D     | 750                                                     |                                         |

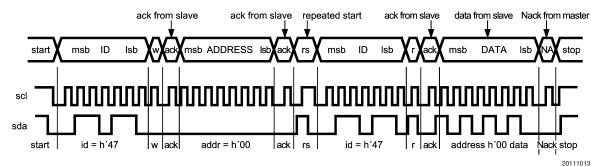

w = write (sda = "0")

r = read (sda = "1")

ack = acknowledge (sda pulled low by either master or slave)

Nack = No Acknowledge rs = repeated start

FIGURE 7. LP3947 (Slave) Register Write

w = write (sda = "0")

r = read (sda = "1")

ack = acknowledge (sda pulled low by either master or slave)

Nack = No Acknowledge

rs = repeated start

#### FIGURE 8. LP3947 (Slave) Register Read

#### THERMAL PERFORMANCE OF LLP PACKAGE

The LP3947 is a monolithic device with an integrated pass transistor. To enhance the power dissipation performance, the Leadless Lead frame Package, or LLP, is used. The LLP package is designed for improved thermal performance because of the exposed die attach pad at the bottom center of the package. It brings advantage to thermal performance by creating a very direct path for thermal dissipation. Compared to the traditional leaded packages where the die attach pad is embedded inside the mold compound, the LLP reduces a layer of thermal path.

The thermal advantage of the LLP package is fully realized only when the exposed die attach pad is soldered down to a thermal land on the PCB board and thermal vias are planted underneath the thermal land. Based on a LLP thermal measurement, junction to ambient thermal resistance  $(\theta_{\text{JA}})$  can be improved by as much as two times if a LLP is soldered on the board with thermal land and thermal vias than if not.

An example of how to calculate for LLP thermal performance is shown below:

$$\theta_{JA} = \frac{T_J - T_A}{P_D}$$

By substituting  $37^{\circ}$ C/W for  $\theta_{JA}$ ,  $125^{\circ}$ C for  $T_{J}$  and  $70^{\circ}$ C for  $T_{A}$ , the maximum power dissipation allowed from the chip is 1.48W. If  $V_{CHG-IN}$  is at 5.0V and a 3.0V battery is being

charged, then 740 mA of  $I_{CHG}$  can safely charge the battery. More power can be dissipated at ambient temperatures below 70°C. Less power can be dissipated at ambient temperatures above 70°C. The maximum power dissipation for operation can be increased by 27 mW for each degree below 70°C, and it must be de-rated by 27 mW for each degree above 70°C.

#### LAYOUT CONSIDERATION

The LP3947 has an exposed die attach pad located at the bottom center of the LLP package. It is imperative to create a thermal land on the PCB board when designing a PCB layout for the LLP package. The thermal land helps to conduct heat away from the die, and the land should be the same dimension as the exposed pad on the bottom of the LLP (1:1 ratio). In addition, thermal vias should be added inside the thermal land to conduct more heat away from the surface of the PCB to the ground plane. Typical pitch and outer diameter for these thermal vias are 1.27 mm and 0.33 mm respectively. Typical copper via barrel plating is 1oz although thicker copper may be used to improve thermal performance. The LP3947 bottom pad is connected to ground. Therefore, the thermal land and vias on the PCB board need to be connected to ground.

For more information on board layout techniques, refer to Application Note 1187 "Leadless Leadframe Package (LLP)." The application note also discusses package handling, solder stencil, and assembly.

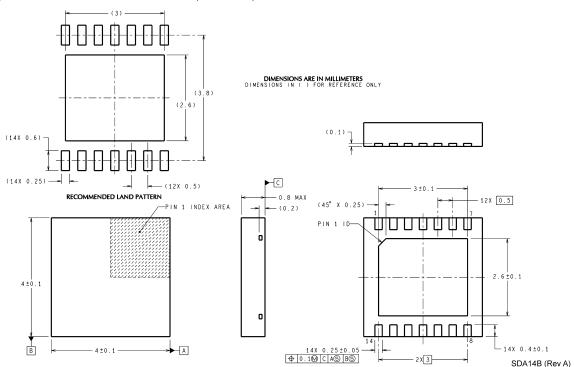

### Physical Dimensions inches (millimeters) unless otherwise noted

NS Package Number SDA14B

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560