### LM4950 Boomer® Audio Power Amplifier Series

## 7.5W Mono-BTL or 3.1W Stereo Audio Power Amplifier

### **General Description**

The LM4950 is a dual audio power amplifier primarily designed for demanding applications in flat panel monitors and TV's. It is capable of delivering 3.1 watts per channel to a  $4\Omega$  single-ended load with less than 1% THD+N or 7.5 watts mono BTL to an  $8\Omega$  load, with less than 10% THD+N from a  $12V_{DG}$  power supply.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM4950 does not require bootstrap capacitors or snubber circuits. Therefore, it is ideally suited for display applications requiring high power and minimal size.

The LM4950 features a low-power consumption active-low shutdown mode. Additionally, the LM4950 features an internal thermal shutdown protection mechanism along with short circuit protection.

The LM4950 contains advanced pop & click circuitry that eliminates noises which would otherwise occur during turn-on and turn-off transitions.

The LM4950 is a unity-gain stable and can be configured by external gain-setting resistors.

### **Key Specifications**

|  | Quiscent F | Power | Supply | Current | 16mA | (typ) |

|--|------------|-------|--------|---------|------|-------|

|--|------------|-------|--------|---------|------|-------|

■ P<sub>OUT</sub> (SE)

$V_{DD} = 12V, R_L = 4\Omega, 1\% \text{ THD+N}$  3.1W (typ)

■ P<sub>OUT</sub> (BTL)

$V_{DD} = 12V, R_L = 8\Omega, 10\% \text{ THD+N}$  7.5W (typ)

■ Shutdown current 40µA (typ)

#### **Features**

- Pop & click circuitry eliminates noise during turn-on and turn-off transitions

- Low current, active-low shutdown mode

- Low quiescent current

- Stereo 3.1W output,  $R_1 = 4\Omega$

- Mono 7.5W BTL output,  $R_L = 8\Omega$

- Short circuit protection

- Unity-gain stable

- External gain configuration capability

### **Applications**

- Flat Panel Monitors

- Flat panel TV's

- Computer Sound Cards

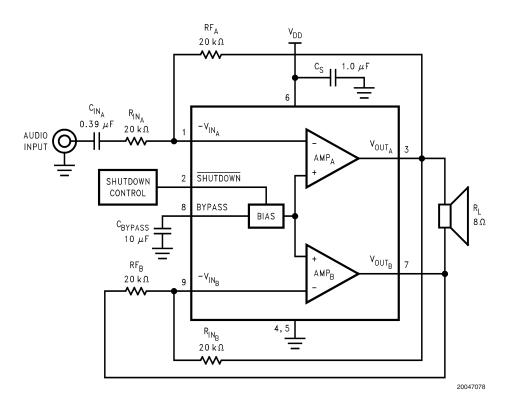

### **Typical Application**

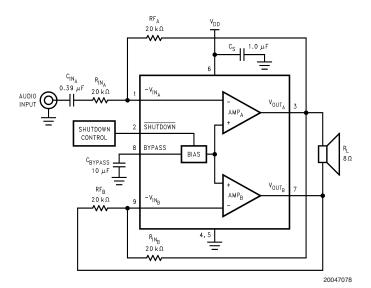

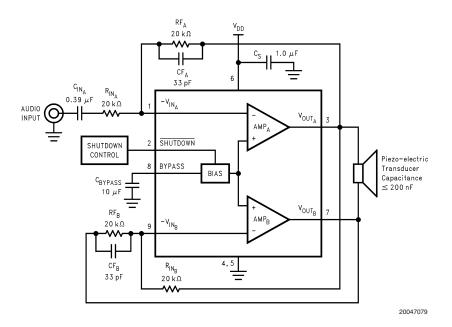

FIGURE 1. Typical Bridge-Tied-Load (BTL) Audio Amplifier Application Circuit

Boomer® is a registered trademark of National Semiconductor Corporation.

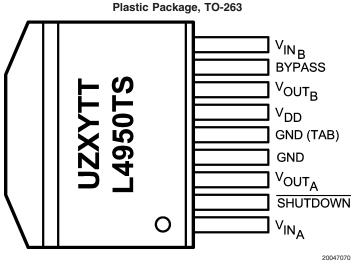

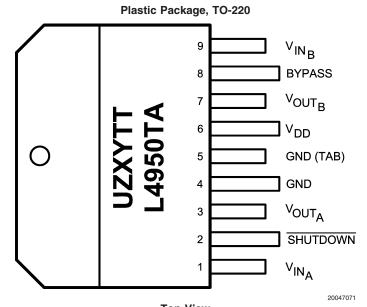

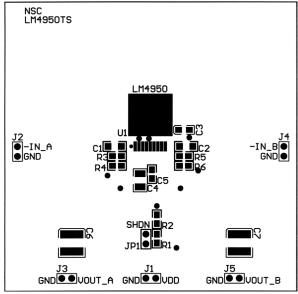

### **Connection Diagrams**

Top View

U = Wafer Fab Code

Z = Assembly Plant Code

XY = Date Code

TT = Die Traceability

Order Number LM4950TS

See NS Package Number TS9A

Top View

U = Wafer Fab Code

Z = Assembly Plant Code

XY = Date Code

TT = Die Traceability

Order Number LM4950TA

See NS Package Number TA09A

### Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (pin 6, referenced

to GND, pins 4 and 5) 18.0V Storage Temperature  $-65^{\circ}C$  to  $+150^{\circ}C$

Input Voltage

pins 3 and 7 -0.3V to  $V_{DD} + 0.3V$ pins 1, 2, 8, and 9 -0.3V to 9.5V

Power Dissipation (Note 3) Internally limited ESD Susceptibility (Note 4) 2000V

ESD Susceptibility (Note 5) 20

| Junction Temperature        | 150°C  |

|-----------------------------|--------|

| Thermal Resistance          |        |

| $\theta_{JC}$ (TS)          | 4°C/W  |

| $\theta_{JA}$ (TS) (Note 3) | 20°C/W |

| $\theta_{JC}$ (TA)          | 4°C/W  |

| $\theta_{JA}$ (TA) (Note 3) | 20°C/W |

### **Operating Ratings**

Temperature Range

$\begin{aligned} T_{\text{MIN}} \leq T_{\text{A}} \leq T_{\text{MAX}} & -40\,^{\circ}\text{C} \leq T_{\text{A}} \leq 85\,^{\circ}\text{C} \\ \text{Supply Voltage} & 9.6\text{V} \leq \text{V}_{\text{DD}} \leq 16\text{V} \end{aligned}$

### Electrical Characteristics V<sub>DD</sub> = 12V (Notes 1, 2)

The following specifications apply for  $V_{DD} = 12V$ ,  $A_V = 0$ dB (SE) or 6dB (BTL) unless otherwise specified. Limits apply for  $T_A = 25$ °C.

| Symbol            | Parameter                         | Conditions                                                                            | LM4950   |                    | Units       |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------|----------|--------------------|-------------|

|                   |                                   |                                                                                       | Typical  | Limit              | (Limits)    |

|                   |                                   |                                                                                       | (Note 6) | (Notes 7, 8)       |             |

| I <sub>DD</sub>   | Quiescent Power Supply Current    | $V_{IN} = 0V$ , $I_O = 0A$ , No Load                                                  | 16       | 30                 | mA (max)    |

| I <sub>SD</sub>   | Shutdown Current                  | V <sub>SHUTDOWN</sub> = GND (Note 9)                                                  | 40       | 80                 | μA (max)    |

| Vos               | Offset Voltage                    | $V_{IN} = 0V$ , $RL = 8\Omega$                                                        | 5        | 30                 | mV (max)    |

| V <sub>SDIH</sub> | Shutdown Voltage Input High       |                                                                                       |          | 2.0                | V (min)     |

|                   |                                   |                                                                                       |          | V <sub>DD</sub> /2 | V (max)     |

| $V_{SDIL}$        | Shutdown Voltage Input Low        |                                                                                       |          | 0.4                | V (max)     |

| T <sub>WU</sub>   | Wake-up Time                      | $C_B = 10\mu F$                                                                       | 440      |                    | ms          |

| TSD               | Thermal Shutdown Temperature      |                                                                                       | 170      | 150                | °C (min)    |

| 100               | Thermal Shutdown Temperature      |                                                                                       |          | 190                | °C (max)    |

| Po                | Output Power                      | f = 1kHz                                                                              |          |                    |             |

|                   |                                   | $R_L = 4\Omega$ SE, Single Channel,                                                   |          | 3.0                | W (min)     |

|                   |                                   | THD+N = 1%                                                                            | 3.1      | 3.0                | VV (111111) |

|                   |                                   | $R_L = 8\Omega$ BTL, THD+N = 10%                                                      | 7.5      |                    |             |

|                   |                                   | $P_O = 2.5Wrms; f = 1kHz;$                                                            | 0.05     |                    |             |

| THD+N             | Total Harmomic Distortion + Noise | $R_L = 4\Omega SE$                                                                    | 0.03     |                    | %           |

| TTID+N            | Total Harmonic Distortion + Noise | $P_{O} = 2.5 \text{Wrms}; A_{V} = 10; f = 1 \text{kHz};$                              | 0.14     |                    |             |

|                   |                                   | $R_L = 4\Omega$ , SE                                                                  |          |                    |             |

| $\epsilon_{OS}$   | Output Noise                      | A-Weighted Filter, $V_{IN} = 0V$ ,                                                    | 10       |                    | μV          |

|                   |                                   | Input Referred                                                                        |          |                    | μ,          |

| X <sub>TALK</sub> | Channel Separation                | $f_{IN} = 1kHz, P_O = 1W, SE Mode$                                                    |          |                    |             |

|                   |                                   | $R_L = 8\Omega$                                                                       | 76       |                    | dB          |

|                   |                                   | $R_L = 4\Omega$                                                                       | 70       |                    |             |

| PSRR              | Power Supply Rejection Ratio      | $V_{RIPPLE} = 200 \text{mV}_{p-p}, \text{ f} = 1 \text{kHz},$<br>$R_L = 8\Omega, BTL$ | 70       | 56                 | dB (min)    |

| I <sub>OL</sub>   | Output Current Limit              | $V_{IN} = 0V, R_L = 500m\Omega$                                                       | 5        |                    | Α           |

Note 1: All voltages are measured with respect to the GND pin, unless otherwise specified.

**Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

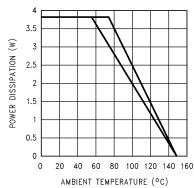

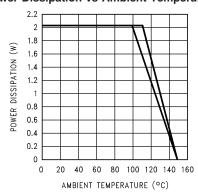

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the given in Absolute Maximum Ratings, whichever is lower. For the LM4950 typical application (shown in *Figure 1*) with  $V_{DD} = 12V$ ,  $R_L = 4\Omega$  stereo operation the total power dissipation is 3.65W.  $\theta_{JA} = 20^{\circ}$ C/W for both TO263 and TO220 packages mounted to  $16in^2$  heatsink surface area.

3

Note 4: Human body model, 100pF discharged through a 1.5 k $\!\Omega$  resistor.

Note 5: Machine Model, 220pF-240pF discharged through all pins.

# **Electrical Characteristics** $V_{DD} = 12V$ (Notes 1, 2) (Continued) **Note 6:** Typicals are measured at 25°C and represent the parametric norm.

- Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

- Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

- Note 9: Shutdown current is measured in a normal room environment. The Shutdown pin should be driven as close as possible to GND for minimum shutdown

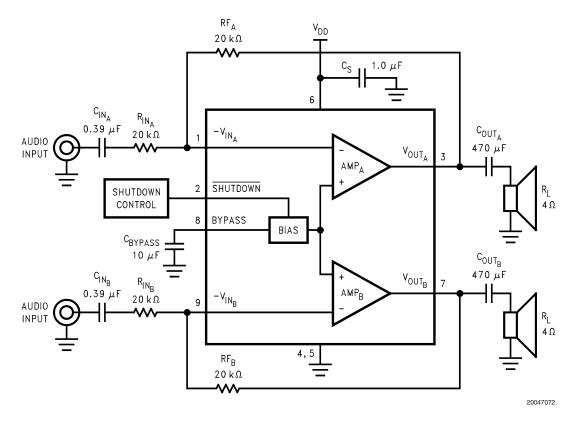

FIGURE 2. Typical Stereo Single-Ended (SE) Audio Amplifier Application Circuit

### External Components Description Refer to (Figure 1.)

| Components             | Functional Description                                                                                                             |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1 D                    | This is the inverting input resistance that, along with $R_F$ , sets the closed-loop gain. Input resistance $R_{IN}$               |  |  |  |

| 1. R <sub>IN</sub>     | and input capacitance $C_{IN}$ form a high pass filter. The filter's cutoff frequency is $f_c = 1/(2\pi R_{IN}C_{IN})$ .           |  |  |  |

|                        | This is the input coupling capacitor. It blocks DC voltage at the amplifier's inverting input. C <sub>IN</sub> and R <sub>IN</sub> |  |  |  |

| 2. C <sub>IN</sub>     | create a highpass filter. The filter's cutoff frequency is $f_C = 1/(2\pi R_{IN}C_{IN})$ . Refer to the <b>SELECTING</b>           |  |  |  |

|                        | <b>EXTERNAL COMPONENTS</b> , for an explanation of determining $C_{IN}$ 's value.                                                  |  |  |  |

| 3. R <sub>F</sub>      | This is the feedback resistance that, along with R <sub>i</sub> , sets closed-loop gain.                                           |  |  |  |

| 4. C <sub>S</sub>      | The supply bypass capacitor. Refer to the POWER SUPPLY BYPASSING section for information about                                     |  |  |  |

| 4. U <sub>S</sub>      | properly placing, and selecting the value of, this capacitor.                                                                      |  |  |  |

|                        | This capacitor filters the half-supply voltage present on the BYPASS pin. Refer to the Application section,                        |  |  |  |

| 5. C <sub>BYPASS</sub> | SELECTING EXTERNAL COMPONENTS, for information about properly placing, and selecting the                                           |  |  |  |

|                        | value of, this capacitor.                                                                                                          |  |  |  |

### **Typical Performance Characteristics**

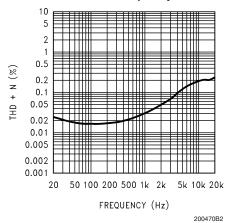

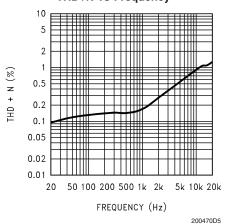

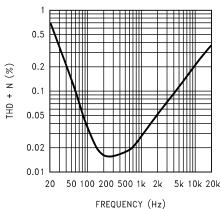

#### THD+N vs Frequency

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , BTL operation,  $P_{OUT}$  = 1W

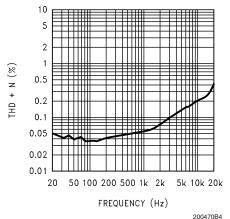

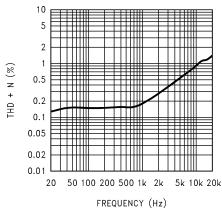

#### THD+N vs Frequency

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , BTL operation,  $P_{OUT}$  = 5W

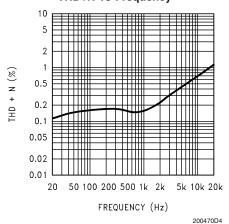

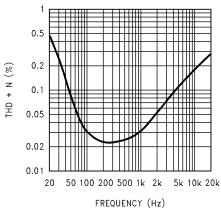

#### THD+N vs Frequency

$\label{eq:VDD} \begin{aligned} \text{V}_{\text{DD}} &= \text{12V}, \, \text{R}_{\text{L}} = 8\Omega, \\ \text{BTL operation, BTLA}_{\text{V}} &= 20, \, \text{P}_{\text{OUT}} = 3\text{W} \end{aligned}$

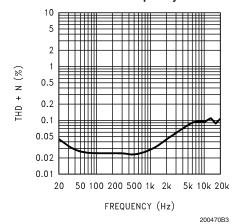

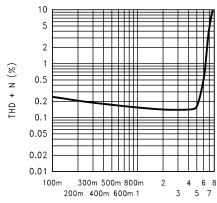

#### THD+N vs Frequency

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , BTL operation,  $P_{OUT}$  = 3W

#### THD+N vs Frequency

$\label{eq:vdd} {\rm V_{DD}} = 12 {\rm V}, \ {\rm R_L} = 8 \Omega, \\ {\rm BTL \ operation}, \ {\rm BTLA_V} = 20, \ {\rm P_{OUT}} = 1 {\rm W}$

#### THD+N vs Frequency

200470D6

$\label{eq:VDD} {\rm V_{DD}} = 12 {\rm V}, \ {\rm R_L} = 8 \Omega,$  BTL operation, BTLA  $_{\rm V} = 20, \ {\rm P_{OUT}} = 5 {\rm W}$

#### THD+N vs Frequency

$V_{DD}$  = 12V,  $R_L$  =  $4\Omega$ , SE operation, both channels driven and loaded (average shown),  $P_{OUT} = 1W, A_V = 1$

#### THD+N vs Frequency

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , SE operation, both channels driven and loaded (average shown),  $P_{OUT} = 1W, A_V = 1$

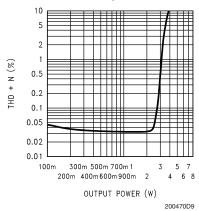

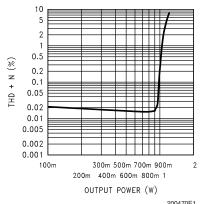

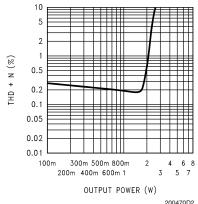

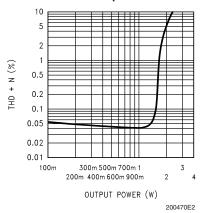

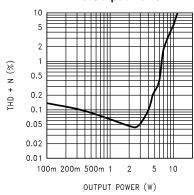

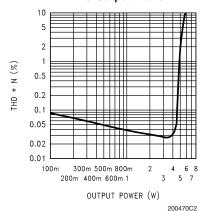

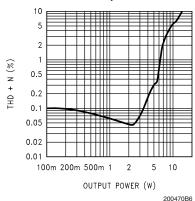

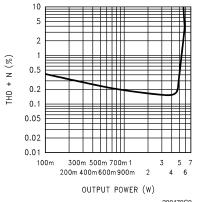

#### THD+N vs Output Power

OUTPUT POWER (W)

200470D0

$V_{DD} = 12V, R_L = 8\Omega,$ BTL operation, BTLA $_V$  = 20,  $f_{IN}$  = 1kHz

#### THD+N vs Frequency

$V_{DD}$  = 12V,  $R_L$  =  $4\Omega$ , SE operation, both channels driven and loaded (average shown),  $P_{OUT} = 2.5W, A_V = 1$

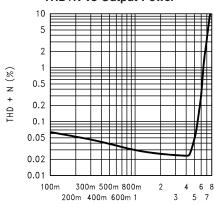

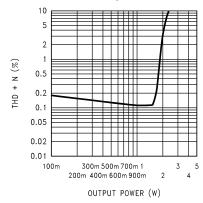

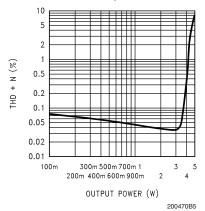

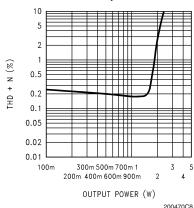

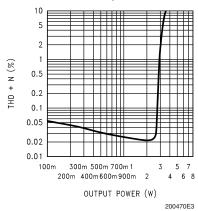

#### THD+N vs Output Power

OUTPUT POWER (W)

200470A9

$V_{DD} = 12V, R_L = 8\Omega,$ BTL operation,  $f_{IN} = 1kHz$

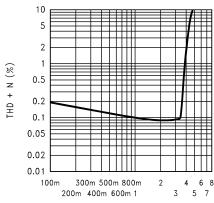

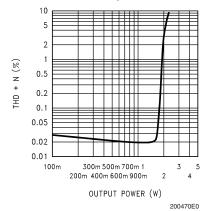

#### THD+N vs Output Power

OUTPUT POWER (W)

200470D1

$$\label{eq:vdd} \begin{aligned} V_{DD} &= 12V, \ R_L = 16\Omega, \\ \text{BTL operation, BTLA}_V &= 20, \ f_{\text{IN}} = 1\text{kHz} \end{aligned}$$

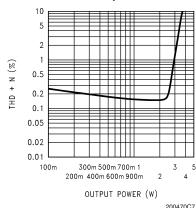

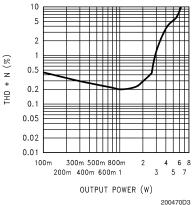

#### THD+N vs Output Power

$\label{eq:VDD} {\rm V_{DD}} = 12 {\rm V}, \ {\rm R_L} = 4 \Omega, \ {\rm SE} \ {\rm operation},$  both channels driven and loaded (average shown),  ${\rm f_{IN}} = 1 {\rm kHz}$

#### THD+N vs Output Power

$V_{DD}$  = 12V,  $R_L$  = 16 $\Omega$ , SE operation, both channels driven and loaded (average shown),  $f_{IN}$  = 1kHz

#### THD+N vs Output Power

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , SE operation,  $A_V$  = 10 both channels driven and loaded (average shown),  $f_{IN}$  = 1kHz

#### THD+N vs Output Power

$\label{eq:VDD} {\rm V_{DD}} = 12 {\rm V}, \ {\rm R_L} = 8 \Omega, \ {\rm SE} \ {\rm operation},$  both channels driven and loaded (average shown),  ${\rm f_{IN}} = 1 {\rm kHz}$

#### THD+N vs Output Power

$V_{DD}$  = 12V, R<sub>L</sub> = 4 $\Omega$ , SE operation, A<sub>V</sub> = 10 both channels driven and loaded (average shown),  $f_{IN}$  = 1kHz

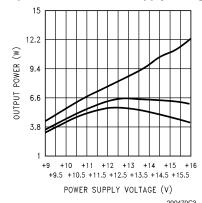

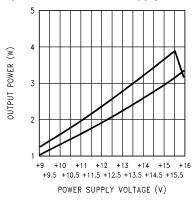

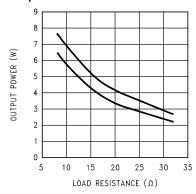

#### **Output Power vs Power Supply Voltage**

$R_L=8\Omega,\ BTL,\ f_{IN}=1kHz,$  at (from top to bottom at 12V): THD+N = 10% THD+N = 1%, THD+N = 0.2%

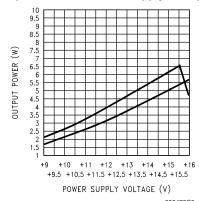

#### **Output Power vs Power Supply Voltage**

$R_L=4\Omega, \, \text{SE operation}, \\ \text{both channels driven and loaded (average shown)}, \\ \text{at (from top to bottom at 12V): THD+N = 10\%}, \\ \text{THD+N = 1\%}$

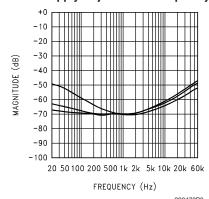

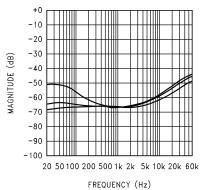

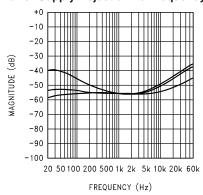

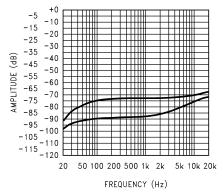

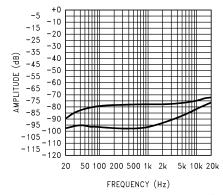

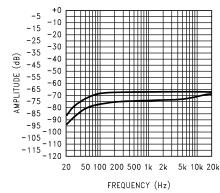

#### **Power Supply Rejection vs Frequency**

$$\begin{split} V_{DD} &= 12 V, \ R_L = 8 \Omega, \ BTL \ operation, \\ V_{RIPPLE} &= 200 m V_{p-p}, \ at \ (from \ top \ to \ bottom \ at \ 60 Hz): \\ C_{BYPASS} &= 1 \mu F, \ C_{BYPASS} = 4.7 \mu F, \ C_{BYPASS} = 10 \mu F, \end{split}$$

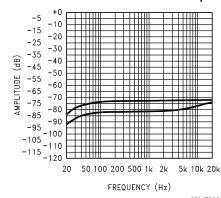

#### **Power Supply Rejection vs Frequency**

$$\begin{split} \textbf{V}_{\text{DD}} &= 12 \textbf{V}, \, \textbf{R}_{\text{L}} = 8 \Omega, \, \text{BTL operation}, \, \textbf{V}_{\text{RIPPLE}} = 200 \text{mV}_{\text{p-p}}, \\ \textbf{A}_{\text{V}} &= 20, \, \text{at (from top to bottom at 60Hz):} \\ \textbf{C}_{\text{BYPASS}} &= 1 \mu \textbf{F}, \, \textbf{C}_{\text{BYPASS}} = 4.7 \mu \textbf{F}, \, \textbf{C}_{\text{BYPASS}} = 10 \mu \textbf{F} \end{split}$$

#### **Output Power vs Power Supply Voltage**

$\rm R_L=8\Omega,$  SE operation,  $\rm f_{IN}=1kHz,$  both channels driven and loaded (average shown), at (from top to bottom at 12V): THD+N = 10%, THD+N = 1%

#### Power Supply Rejection vs Frequency

$$\begin{split} V_{DD} &= 12 V, \ R_L = 8 \Omega, \ SE \ operation, \\ V_{RIPPLE} &= 200 m V_{p-p}, \ at \ (from \ top \ to \ bottom \ at \ 60 Hz): \\ C_{BYPASS} &= 1 \mu F, \ C_{BYPASS} = 4.7 \mu F, \ C_{BYPASS} = 10 \mu F, \end{split}$$

200470B8

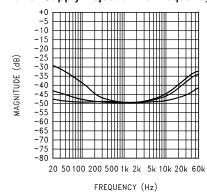

#### **Power Supply Rejection vs Frequency**

$V_{DD}$  = 12V,  $R_L$  = 8Ω, SE operation,  $V_{RIPPLE}$  = 200m $V_{p-p}$ ,  $A_V$  = 10, at (from top to bottom at 60Hz):  $C_{BYPASS}$  = 1 $\mu$ F,  $C_{BYPASS}$  = 4.7 $\mu$ F,  $C_{BYPASS}$  = 10 $\mu$ F

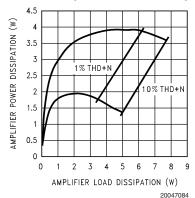

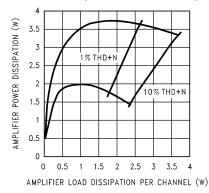

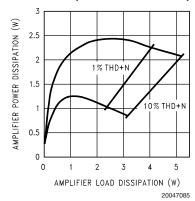

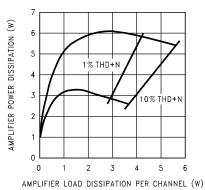

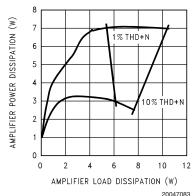

#### **Total Power Dissipation vs Load Dissipation**

$V_{DD}$  = 12V, BTL operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 3W):  $R_L$  = 8 $\Omega$ ,  $R_L$  = 16 $\Omega$

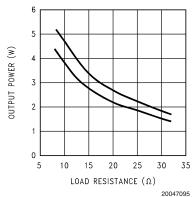

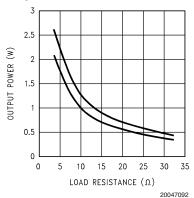

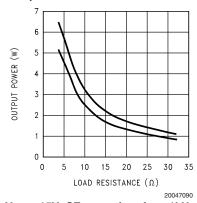

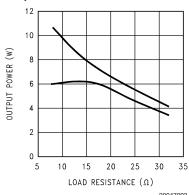

#### **Output Power vs Load Resistance**

$V_{DD}$  = 12V, BTL operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

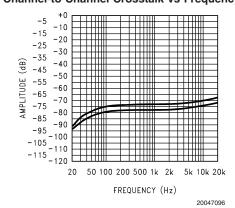

#### Channel-to-Channel Crosstalk vs Frequency

$m V_{DD}$  = 12V, R<sub>L</sub> = 4 $\Omega$ , P<sub>OUT</sub> = 1W, SE operation, at (from top to bottom at 1kHz): V<sub>INB</sub> driven, V<sub>OUTB</sub> measured; V<sub>INA</sub> driven, V<sub>OUTB</sub> measured

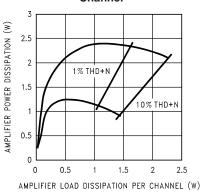

#### **Total Power Dissipation vs Load Dissipation**

$V_{DD}$  = 12V, SE operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 1W):  $R_L = 4\Omega$ ,  $R_L = 8\Omega$

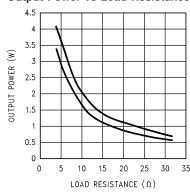

#### **Output Power vs Load Resistance**

$V_{DD}$  = 12V, SE operation,  $f_{IN}$  = 1kHz, both channels driven and loaded, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

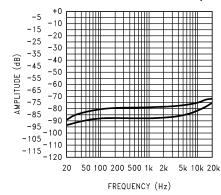

#### Channel-to-Channel Crosstalk vs Frequency

$m V_{DD}$  = 12V, R<sub>L</sub> = 8 $\Omega$ , P<sub>OUT</sub> = 1W, SE operation, at (from top to bottom at 1kHz): V<sub>INB</sub> driven, V<sub>OUTA</sub> measured; V<sub>INA</sub> driven, V<sub>OUTB</sub> measured

#### THD+N vs Output Power

$\begin{aligned} \mathbf{V_{DD}} &= 9.6 \text{V, R}_{\text{L}} = 8 \Omega, \\ \text{BTL operation, f}_{\text{IN}} &= 1 \text{kHz} \end{aligned}$

#### THD+N vs Output Power

$V_{DD}$  = 9.6V,  $R_L$  = 8 $\Omega$ , BTL operation, BTLA<sub>V</sub> = 20,  $f_{IN}$  = 1kHz

#### **Total Power Dissipation vs Load Dissipation**

$V_{DD}$  = 9.6V, BTL operation,  $f_{IN}$  = 1kHz at (from top to bottom at 2W):  $R_L$  =  $8\Omega$ ,  $R_L$  =  $16\Omega$

#### THD+N vs Output Power

$\begin{aligned} \mathbf{V_{DD}} &= 9.6 \text{V, R}_{\text{L}} = 4 \Omega, \\ \text{SE operation, f}_{\text{IN}} &= 1 \text{kHz} \\ \text{both channels driven and loaded (average shown)} \end{aligned}$

#### THD+N vs Output Power

${

m V_{DD}}$  = 9.6V, R<sub>L</sub> = 4 $\Omega$ , SE operation, AV = 10, f<sub>IN</sub> = 1kHz both channels driven and loaded (average shown)

#### Total Power Dissipation vs Load Dissipation per Channel

$V_{DD}$  = 9.6V, SE operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 1W):  $R_L = 4\Omega$ ,  $R_L = 8\Omega$

#### **Output Power vs Load Resistance**

$V_{DD}$  = 9.6V, BTL operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

### Channel-to Channel Crosstalk vs Frequency

$m V_{DD}$  = 9.6V, R<sub>L</sub> = 4 $\Omega$ , P<sub>OUT</sub> = 1W, SE operation, at (from top to bottom at 1kHz): V<sub>INB</sub> driven, V<sub>OUTA</sub> measured; V<sub>INA</sub> driven, V<sub>OUTB</sub> measured

#### THD+N vs Output Power

$V_{DD}$  = 15V,  $R_L$  =  $8\Omega$ , BTL operation,  $f_{IN}$  = 1kHz

#### **Output Power vs Load Resistance**

$m V_{DD}$  = 9.6V, SE operation, f $_{IN}$  = 1kHz, both channels driven and loaded, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

#### Channel-to Channel Crosstalk vs Frequency

$m V_{DD}$  = 9.6V, R<sub>L</sub> = 8 $\Omega$ , P<sub>OUT</sub> = 1W, SE operation, at (from top to bottom at 1kHz): V<sub>INB</sub> driven, V<sub>OUTB</sub> measured

#### THD+N vs Output Power

$\begin{aligned} \mathbf{V_{DD}} &= 15 \mathbf{V}, \, \mathbf{R_L} = 4 \Omega, \\ \mathbf{SE} \ \text{operation, f}_{\mathrm{IN}} &= 1 \mathrm{kHz} \\ \mathbf{both} \ \text{channels driven and loaded (average shown)} \end{aligned}$

#### THD+N vs Output Power

$\begin{aligned} \mathbf{V}_{\mathrm{DD}} &= 15\mathrm{V}, \ \mathbf{R}_{\mathrm{L}} &= 8\Omega, \\ \mathbf{SE} \ \text{operation, f}_{\mathrm{IN}} &= 1\mathrm{kHz} \\ \mathbf{both \ channels \ driven \ and \ loaded \ (average \ shown)} \end{aligned}$

#### Total Power Dissipation vs Load Dissipation per Channel

$V_{DD}$  = 15V, SE operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 2W):  $R_L$  =  $4\Omega$ ,  $R_L$  =  $8\Omega$

#### **Output Power vs Load Resistance**

$m V_{DD}$  = 15V, SE operation, f $_{\rm IN}$  = 1kHz, both channels driven and loaded, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

#### **Total Power Dissipation vs Load Dissipation**

$V_{DD}$  = 15V, BTL operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 4W):  $R_L$  = 8 $\Omega$ ,  $R_L$  = 16 $\Omega$

#### **Output Power vs Load Resistance**

$V_{DD}$  = 15V, BTL operation,  $f_{IN}$  = 1kHz, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

#### THD+N vs Output Power

$V_{DD}$  = 16V,  $R_L$  = 8 $\Omega$ , BTL operation,  $f_{IN}$  = 1kHz

#### THD+N vs Output Power

$\label{eq:VDD} {\rm V_{DD}} = 16 {\rm V, \ R_L} = 8 \Omega,$  BTL operation,  ${\rm f_{IN}} = 1 {\rm kHz, \ BTLA_V} = 20$

### THD+N vs Output Power

$\begin{aligned} \mathbf{V_{DD}} &= \mathbf{16V}, \ \mathbf{R_L} = \mathbf{4\Omega}, \ \mathbf{A_V} = \mathbf{10} \\ \mathbf{SE} \ \text{operation}, \ \mathbf{f_{IN}} &= \mathbf{1kHz}, \\ \mathbf{both} \ \text{channels} \ \text{driven} \ \text{and} \ \mathbf{loaded} \ \text{(average shown)} \end{aligned}$

#### Channel-to-Channel Crosstalk vs Frequency

$m V_{DD}$  = 16V, R<sub>L</sub> = 4 $\Omega$ , P<sub>OUT</sub> = 1W, SE operation at (from top to bottom at 1kHz): V<sub>INB</sub> driven, V<sub>OUTA</sub> measured; V<sub>INA</sub> driven, V<sub>OUTB</sub> measured

#### Channel-to-Channel Crosstalk vs Frequency

$m V_{DD} = 16V, R_L = 8\Omega, P_{OUT} = 1W, SE$  operation at (from top to bottom at 1kHz):  $m V_{INB}$  driven,  $m V_{OUTA}$  measured;  $m V_{INA}$  driven,  $m V_{OUTB}$  measured

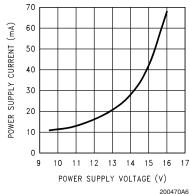

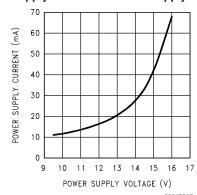

#### Power Supply Current vs Power Supply Voltage

$R_L = 8\Omega$ , BTL operation  $V_{IN} = 0V$ ,  $R_{SOURCE} = 50\Omega$

#### **Power Supply Current vs Power Supply Voltage**

$R_L = 4\Omega$ , SE operation  $V_{IN} = 0V$ ,  $R_{SOURCE} = 50\Omega$

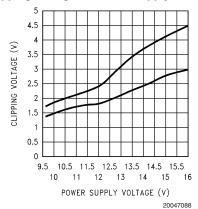

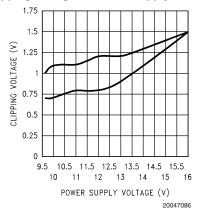

#### Clipping Voltage vs Power Supply Voltage

$m R_L = 8\Omega, \, BTL \, \, operation, \, f_{IN} = 1 kHz$  at (from top to bottom at 12V): positive signal swing, negative signal swing

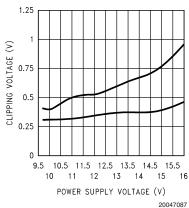

#### Clipping Voltage vs Power Supply Voltage

$m R_L = 4\Omega,$  SE operation,  $\rm f_{IN} = 1 kHz$  both channels driven and loaded, at (from top to bottom at 13V): negative signal swing, positive signal swing

#### **Power Dissipation vs Ambient Temperature**

$V_{DD}$  = 12V,  $R_L$  =  $8\Omega$  (BTL),  $f_{IN}$  = 1kHz, (from to bottom at  $80^{\circ}$ C):  $16in^2$  copper plane heatsink area,  $8in^2$  copper plane heatsink area

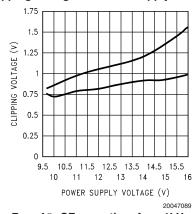

#### Clipping Voltage vs Power Supply Voltage

$R_L = 16\Omega$ , BTL operation,  $f_{IN} = 1kHz$ at (from to bottom at 12V): positive signal swing, negative signal swing

#### Clipping Voltage vs Power Supply Voltage

$m R_L = 8\Omega, \, SE \, operation, \, f_{IN} = 1kHz$  both channels driven and loaded, at (from to bottom at 13V): negative signal swing, positive signal swing

#### **Power Dissipation vs Ambient Temperature**

$m V_{DD}$  = 12V, R<sub>L</sub> = 8 $\Omega$  (SE), f<sub>IN</sub> = 1kHz, (from to bottom at 120°C): 16in² copper plane heatsink area, 8in² copper plane heatsink area

### **Application Information**

## HIGH VOLTAGE BOOMER WITH INCREASED OUTPUT POWER

Unlike previous 5V Boomer® amplifiers, the LM4950 is designed to operate over a power supply voltages range of 9.6V to 16V. Operating on a 12V power supply, the LM4950 will deliver 7.5W into an  $8\Omega$  BTL load with no more than 10% THD+N.

FIGURE 3. Typical LM4950 BTL Application Circuit

#### **BRIDGE CONFIGURATION EXPLANATION**

As shown in *Figure 3*, the LM4950 consists of two operational amplifiers that drive a speaker connected between their outputs. The value of external input and feedback resistors determine the gain of each amplifier. Resistors RIN<sub>A</sub> and RF<sub>A</sub> set the closed-loop gain of AMP<sub>A</sub>, whereas two  $20k\Omega$  resistors set AMP<sub>B</sub>'s gain to -1. The LM4950 drives a load, such as a speaker, connected between the two amplifier outputs, VOUT<sub>A</sub> and VOUT<sub>B</sub>. *Figure 3* shows that AMP<sub>A</sub>'s output serves as AMP<sub>B</sub>'s input. This results in both amplifiers producing signals identical in magnitude, but 180° out of phase. Taking advantage of this phase difference, a load is placed between AMP<sub>A</sub> and AMP<sub>B</sub> and driven differentially (commonly referred to as "bridge mode"). This results in a differential, or BTL, gain of

$$A_{VD} = 2(R_f / R_i) \tag{1}$$

Bridge mode amplifiers are different from single-ended amplifiers that drive loads connected between a single amplifier's output and ground. For a given supply voltage, bridge mode has a distinct advantage over the single-ended configuration: its differential output doubles the voltage swing

across the load. Theoretically, this produces four times the output power when compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited and that the output signal is not clipped. To ensure minimum output signal clipping when choosing an amplifier's closed-loop gain, refer to the **AUDIO POWER AMPLIFIER DESIGN** section.

Another advantage of the differential bridge output is no net DC voltage across the load. This is accomplished by biasing AMP1's and AMP2's outputs at half-supply. This eliminates the coupling capacitor that single supply, single-ended amplifiers require. Eliminating an output coupling capacitor in a typical single-ended configuration forces a single-supply amplifier's half-supply bias voltage across the load. This increases internal IC power dissipation and may permanently damage loads such as speakers.

#### **POWER DISSIPATION**

Power dissipation is a major concern when designing a successful single-ended or bridged amplifier. Equation (2) states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX-SE} = (V_{DD})^2 / (2\pi^2 R_L)$$

: Single Ended (2)

The LM4950's dissipation is twice the value given by Equation (2) when driving two SE loads. For a 12V supply and two  $8\Omega$  SE loads, the LM4950's dissipation is 1.82W.

The LM4950's dissipation when driving a BTL load is given by Equation (3). For a 12V supply and a single  $8\Omega$  BTL load, the dissipation is 3.65W.

$$P_{DMAX-MONOBTL} = 4(V_{DD})^2 / 2\pi^2 R_L$$

: Bridge Mode (3)

The maximum power dissipation point given by Equation (3) must not exceed the power dissipation given by Equation (4):

$$P_{DMAX}' = (T_{JMAX} - T_A) / \theta_{JA}$$

(4)

The LM4950's  $T_{JMAX}=150^{\circ}C$ . In the TS package, the LM4950's  $\theta_{JA}$  is  $20^{\circ}C/W$  when the metal tab is soldered to a copper plane of at least  $16\text{in}^2$ . This plane can be split between the top and bottom layers of a two-sided PCB. Connect the two layers together under the tab with a 5x5 array of vias. For the TA package, use an external heatsink with a thermal impedance that is less than  $20^{\circ}C/W$ . At any given ambient temperature  $T_A$ , use Equation (4) to find the maximum internal power dissipation supported by the IC packaging. Rearranging Equation (4) and substituting  $P_{DMAX}$  for  $P_{DMAX}$  results in Equation (5). This equation gives the maximum ambient temperature that still allows maximum stereo power dissipation without violating the LM4950's maximum junction temperature.

$$T_{A} = T_{JMAX} - P_{DMAX-MONOBTL}\theta_{JA}$$

(5)

For a typical application with a 12V power supply and a BTL  $8\Omega$  load, the maximum ambient temperature that allows maximum stereo power dissipation without exceeding the maximum junction temperature is approximately 77°C for the TS package.

$$T_{JMAX} = P_{DMAX-MONOBTL}\theta_{JA} + T_{A}$$

(6)

Equation (6) gives the maximum junction temperature  $T_{JMAX}$ . If the result violates the LM4950's 150°C, reduce the maximum junction temperature by reducing the power supply voltage or increasing the load resistance. Further allowance should be made for increased ambient temperatures.

The above examples assume that a device is operating around the maximum power dissipation point. Since internal power dissipation is a function of output power, higher ambient temperatures are allowed as output power or duty cycle decreases.

If the result of Equation (3) is greater than that of Equation (4), then decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. Further, ensure that speakers rated at a nominal  $4\Omega$  (SE operation) or  $8\Omega$  (BTL operation) do not fall below  $3\Omega$  or  $6\Omega$ , respectively. If these measures are insufficient, a heat sink can be added to reduce  $\theta_{JA}$ . The heat sink can be created using

additional copper area around the package, with connections to the ground pins, supply pin and amplifier output pins. Refer to the **Typical Performance Characteristics** curves for power dissipation information at lower output power levels.

#### **POWER SUPPLY VOLTAGE LIMITS**

Continuous proper operation is ensured by never exceeding the voltage applied to any pin, with respect to ground, as listed in the Absolute Maximum Ratings section.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a voltage regulator typically use a  $10\mu F$  in parallel with a  $0.1\mu F$  filter capacitors to stabilize the regulator's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 1.0µF tantalum bypass capacitance connected between the LM4950's supply pins and ground. Do not substitute a ceramic capacitor for the tantalum. Doing so may cause oscillation. Keep the length of leads and traces that connect capacitors between the LM4950's power supply pin and ground as short as possible. Connecting a 10µF capacitor, C<sub>BYPASS</sub>, between the BYPASS pin and ground improves the internal bias voltage's stability and improves the amplifier's PSRR. The PSRR improvements increase as the bypass pin capacitor value increases. Too large, however, increases turn-on time and can compromise the amplifier's click and pop performance. The selection of bypass capacitor values, especially  $C_{\mbox{\scriptsize BYPASS}}$ , depends on desired PSRR requirements, click and pop performance (as explained in the section, SELECTING EXTERNAL COMPONENTS), system cost, and size constraints.

#### **MICRO-POWER SHUTDOWN**

The LM4950 features an active-low micro-power shutdown mode. When active, the LM4950's micro-power shutdown feature turns off the amplifier's bias circuitry, reducing the supply current. The low 40µA typical shutdown current is achieved by applying a voltage to the SHUTDOWN pin that is as near to GND as possible. A voltage that is greater than GND may increase the shutdown current.

There are a few methods to control the micro-power shutdown. These include using a single-pole, single-throw switch (SPST), a microprocessor, or a microcontroller. When using a switch, connect a  $100k\Omega$  pull-up resistor between the SHUTDOWN pin and  ${\rm V_{DD}}$  and a second 100k $\!\Omega$  resistor in parallel with the SPST switch connected between the SHUT-DOWN pin and GND. The two resistors form a voltage divider that ensures that the voltage applied to the SHUT-DOWN pin does not exceed V<sub>DD</sub>/2. Select normal amplifier operation by opening the switch. Closing the switch applies GND to the SHUTDOWN pin, activating micro-power shutdown. The switch and resistor guarantee that the SHUT-DOWN pin will not float. This prevents unwanted state changes. In a system with a microprocessor or a microcontroller, use a digital output to apply the active-state voltage to the SHUTDOWN pin. Again, ensure that the microcontroller or microprocessor logic-high signal does not exceed the LM4950's V<sub>DD</sub>/2 SHUTDOWN signal limit.

#### SELECTING EXTERNAL COMPONENTS

#### **Input Capacitor Value Selection**

Two quantities determine the value of the input coupling capacitor: the lowest audio frequency that requires amplification and desired output transient suppression.

As shown in Figure 3, the input resistor  $(R_{IN})$  and the input capacitor  $(C_{IN})$  produce a high pass filter cutoff frequency that is found using Equation (7).

$$f_c = 1/2\pi R_i C_i \tag{7}$$

As an example when using a speaker with a low frequency limit of 50Hz,  $C_i$ , using Equation (7) is 0.159 $\mu$ F. The 0.39 $\mu$ F  $C_{INA}$  shown in *Figure 3* allows the LM4950 to drive high efficiency, full range speaker whose response extends below 30Hz.

#### **Bypass Capacitor Value**

Besides minimizing the input capacitor size, careful consideration should be paid to value of  $C_{\rm BYPASS}$ , the capacitor connected to the BYPASS pin. Since  $C_{\rm BYPASS}$  determines how fast the LM4950 settles to quiescent operation, its value is critical when minimizing turn-on pops. The slower the LM4950's outputs ramp to their quiescent DC voltage (nominally  $V_{\rm DD}/2$ ), the smaller the turn-on pop. Choosing  $C_{\rm BYPASS}$  equal to  $10\mu F$  along with a small value of  $C_{\rm IN}$  (in the range of  $0.1\mu F$  to  $0.39\mu F$ ), produces a click-less and pop-less shutdown function. As discussed above, choosing  $C_{\rm IN}$  no larger than necessary for the desired bandwidth helps minimize clicks and pops.

## OPTIMIZING CLICK AND POP REDUCTION PERFORMANCE

The LM4950 contains circuitry that eliminates turn-on and shutdown transients ("clicks and pops"). For this discussion, turn-on refers to either applying the power supply voltage or when the micro-power shutdown mode is deactivated.

As the  $V_{\rm DD}/2$  voltage present at the BYPASS pin ramps to its final value, the LM4950's internal amplifiers are configured as unity gain buffers and are disconnected from the AMP\_A and AMP\_B pins. An internal current source charges the capacitor connected between the BYPASS pin and GND in a

controlled manner. Ideally, the input and outputs track the voltage applied to the BYPASS pin. The gain of the internal amplifiers remains unity until the voltage applied to the BYPASS pin.

The gain of the internal amplifiers remains unity until the voltage on the bypass pin reaches  $V_{\rm DD}/2$ . As soon as the voltage on the bypass pin is stable, the device becomes fully operational and the amplifier outputs are reconnected to their respective output pins. Although the BYPASS pin current cannot be modified, changing the size of  $C_{\rm BYPASS}$  alters the device's turn-on time. Here are some typical turn-on times for various values of  $C_{\rm BYPASS}$ :

| C <sub>B</sub> (µF) | T <sub>ON</sub> (ms) |  |

|---------------------|----------------------|--|

| 1.0                 | 120                  |  |

| 2.2                 | 120                  |  |

| 4.7                 | 200                  |  |

| 10                  | 440                  |  |

In order eliminate "clicks and pops", all capacitors must be discharged before turn-on. Rapidly switching  $V_{\rm DD}$  may not allow the capacitors to fully discharge, which may cause "clicks and pops".

There is a relationship between the value of  $C_{\text{IN}}$  and  $C_{\text{BYPASS}}$  that ensures minimum output transient when power is applied or the shutdown mode is deactivated. Best performance is achieved by setting the time constant created by  $C_{\text{IN}}$  and  $R_i + R_f$  to a value less than the turn-on time for a given value of  $C_{\text{BYPASS}}$  as shown in the table above.

#### **DRIVING PIEZO-ELECTRIC SPEAKER TRANSDUCERS**

The LM4950 is able to drive capacitive piezo-electric transducer loads that are less than equal to 200nF. Stable operation is assured by placing 33pF capacitors in parallel with the  $20k\Omega$  feedback resistors. The additional capacitors are shown in Figure 4.

When driving piezo-electric tranducers, sound quality and accoustic power is entirely dependent upon a transducer's frequency response and efficiency. In this application, power dissipated by the LM4950 is very low, typically less than 250mW when driving a 200nF piezo-electric transduce  $(V_{DD}=12V)$ .

FIGURE 4. Piezo-electric Transducer Capacitance ≤ 200nF

#### **AUDIO POWER AMPLIFIER DESIGN**

#### Audio Amplifier Design: Driving 4W into an 8 $\Omega$ BTL

The following are the desired operational parameters:

$\begin{array}{lll} \mbox{Power Output} & 4\mbox{W}_{\mbox{RMS}} \\ \mbox{Load Impedance} & 8\Omega \\ \mbox{Input Level} & 0.3\mbox{V}_{\mbox{RMS}} \mbox{ (max)} \\ \mbox{Input Impedance} & 20\mbox{k}\Omega \\ \mbox{Bandwidth} & 50\mbox{Hz-20kHz} \pm 0.25\mbox{dB} \end{array}$

The design begins by specifying the minimum supply voltage necessary to obtain the specified output power. One way to find the minimum supply voltage is to use the *Output Power vs Power Supply Voltage* curve in the **Typical Performance Characteristics** section. Another way, using Equation (8), is to calculate the peak output voltage necessary to achieve the desired output power for a given load impedance. To account for the amplifier's dropout voltage, two additional voltages, based on the *Clipping Dropout Voltage vs Power Supply Voltage* in the **Typical Performance Characteristics** curves, must be added to the result obtained by Equation (8). The result is Equation (9).

$$V_{\text{opeak}} = \sqrt{(2R_{L}P_{0})}$$

(8)

$$V_{DD} = V_{OUTPEAK} + V_{ODTOP} + V_{ODBOT}$$

(9)

The *Output Power vs. Power Supply Voltage* graph for an  $8\Omega$  load indicates a minimum supply voltage of 10.2V. The commonly used 12V supply voltage easily meets this. The additional voltage creates the benefit of headroom, allowing the LM4950 to produce peak output power in excess of 4W without clipping or other audible distortion. The choice of

supply voltage must also not create a situation that violates of maximum power dissipation as explained above in the Power Dissipation section. After satisfying the LM4950's power dissipation requirements, the minimum differential gain needed to achieve 4W dissipation in an  $8\Omega$  BTL load is found using Equation (10).

$$A_{V} \ge \sqrt{(P_{0}R_{L})}/(V_{IN}) = V_{orms}/V_{inrms}$$

(10)

Thus, a minimum gain of 18.9 allows the LM4950's to reach full output swing and maintain low noise and THD+N performance. For this example, let  $A_{V-BTL}=19$ . The amplifier's overall BTL gain is set using the input (RIN<sub>A</sub>) and feedback (R) resistors of the first amplifier in the series BTL configuration. Additionally,  $A_{V-BTL}$  is twice the gain set by the first amplifier's  $R_{IN}$  and  $R_f$ . With the desired input impedance set at  $20k\Omega$ , the feedback resistor is found using Equation (11).

$$R_f / R_{IN} = A_{V-BTL} / 2$$

(11)

The value of  $R_{\rm f}$  is 190k $\!\Omega$  (choose 191k $\!\Omega$  , the closest value). The nominal output power is 4W.

The last step in this design example is setting the amplifier's -3dB frequency bandwidth. To achieve the desired  $\pm 0.25 dB$  pass band magnitude variation limit, the low frequency response must extend to at least one-fifth the lower bandwidth limit and the high frequency response must extend to at least five times the upper bandwidth limit. The gain variation for both response limits is 0.17dB, well within the  $\pm 0.25 dB$ -desired limit. The results are an

$$f_L = 50Hz / 5 = 10Hz$$

(12)

and an

$$f_1 = 20kHz \times 5 = 100kHz$$

(13)

As mentioned in the **SELECTING EXTERNAL COMPONENTS** section,  $R_{\rm INA}$  and  $C_{\rm INA}$  create a highpass filter that sets the amplifier's lower bandpass frequency limit. Find the coupling capacitor's value using Equation (14).

$$C_i = 1 / 2\pi R_{IN} f_L$$

(14)

The result is

1 /  $(2\pi x 20 k\Omega x 10 Hz) = 0.795 \mu F$

Use a 0.82µF capacitor, the closest standard value.

The product of the desired high frequency cutoff (100kHz in this example) and the differential gain  $A_{VD}$ , determines the

upper passband response limit. With  $A_{VD}=7$  and  $f_{H}=100 \mbox{kHz},$  the closed-loop gain bandwidth product (GBWP) is 700 \mbox{kHz}. This is less than the LM4950's 3.5 \mbox{MHz} GBWP. With this margin, the amplifier can be used in designs that require more differential gain while avoiding performance restricting bandwidth limitations.

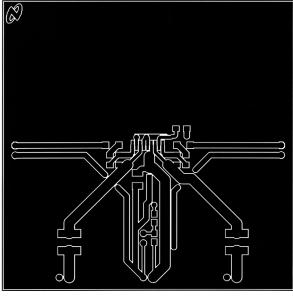

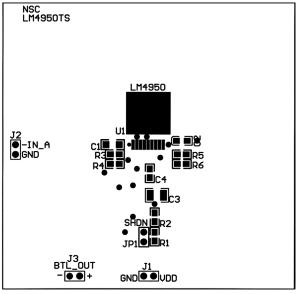

#### RECOMMENDED PRINTED CIRCUIT BOARD LAYOUT

Figure 5 through Figure 7 show the recommended two-layer PC board layout that is optimized for the TO263-packaged, SE-configured LM4950 and associated external components. Figure 8 through Figure 10 show the recommended two-layer PC board layout that is optimized for the TO263-packaged, BTL-configured LM4950 and associated external components. These circuits are designed for use with an external 12V supply and  $4\Omega(\text{min})(\text{SE})$  or  $8\Omega(\text{min})(\text{BTL})$  speakers.

These circuit boards are easy to use. Apply 12V and ground to the board's  $V_{\rm DD}$  and GND pads, respectively. Connect a speaker between the board's  ${\rm OUT_A}$  and  ${\rm OUT_Boutputs}$ .

### **Demonstration Board Layout**

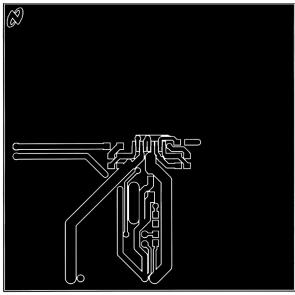

20047063

FIGURE 5. Recommended TS SE PCB Layout: Top Silkscreen

## **Demonstration Board Layout** (Continued)

2004706

FIGURE 6. Recommended TS SE PCB Layout: Top Layer

20047065

FIGURE 7. Recommended TS SE PCB Layout: Bottom Layer

## Demonstration Board Layout (Continued)

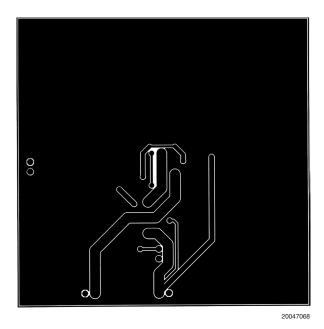

20047066

FIGURE 8. Recommended TS BTL PCB Layout: Top Silkscreen

2004706

FIGURE 9. Recommended TS BTL PCB Layout: Top Layer

## **Demonstration Board Layout** (Continued)

FIGURE 10. Recommended TS BTL PCB Layout:

Bottom Layer

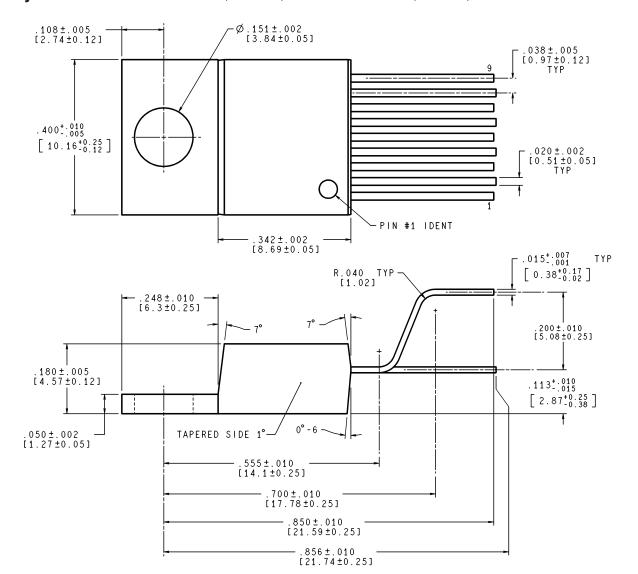

### Physical Dimensions inches (millimeters) unless otherwise noted 10° ± 3° TYP — .038±.005 TYP [0.97±0.12] .270 ± .010 [6.86 ±0.25] .400\*:010 [10.16\*0:25] .575 -[14.61] .410 [10.41] \_\_\_\_\_T024\_\_TYP .020 ± .002 TYP [0.51 ±0.05] -PIN 1 ID .342±.002 [8.69±0.05] .425 .050 MAX -TAPERED SIDE 1° R.030 MAX TYP · .015-.030 [0.38-0.76] -.035 [0.89] .180 ± .002 [4.57 ±0.05] .095 TYP RECOMMENDED LAND PATTERN ONTE 5 .050 ± .002 [1.27 ±0.05] STAND-OFF.000-.006 [0-0.15] - . 490 MAX [12.45] - . 565 MAX -[14.35] CONTROLLING DIMENSION: INCH VALUES IN [] ARE IN MILLIMETERS .250 MIN [6.35] .200 MIN [5.08] TS9A (Rev A)

Order Number LM4950TS NS Package Number TS9A

### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

CONTROLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

TA09A (Rev C)

For Staggered Lead Non-Isolated Package Order Number LM4950TA NS Package Number TA09A

#### **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560