#### LM2639

# 5-Bit Programmable, High Frequency Multi-phase PWM Controller

#### **General Description**

The LM2639 provides an attractive solution for power supplies of high power microprocessors (such as Pentium II™, M II<sup>™</sup>. K6<sup>™</sup>-2. K6<sup>™</sup>-3. etc.) exhibiting ultra fast load transients. Compared to a conventional single-phase supply, an LM2639 based multi-phase supply distributes the thermal and electrical loading among components in multiple phases and greatly reduces the corresponding stress in each component. The LM2639 can be programmed to control either a 3-phase converter or a 4-phase converter. Phase shift among the phases is 120° in the case of three phase and 90° with four-phase. Because the power channels are out of phase, there can be significant ripple cancellation for both the input and output current, resulting in reduced input and output capacitor size. Due to the nominal operating frequency of 2 MHz per phase, the size of the output inductors can be greatly reduced which results in a much faster load transient response and a dramatically shrunk output capacitor bank. Microprocessor power supplies with all surface mount components can be easily built.

The internal high speed transconductance amplifier guarantees good dynamic performance. The output drive voltages can be adjusted through a resistor divider to control switching loss in the external FETs.

The internal master clock frequency of up to 8 MHz is set by an external reference resistor. An external clock of 10 MHz can also be used to drive the chip to achieve frequency control and multi-chip operation.

The LM2639 also provides input under-voltage lock-out with hysteresis and input over-current protection.

#### **Features**

- Ultra fast load transient response

- Enables all surface-mount-design

- Selectable 2, 3, 4 phase operation

- Clock frequency from 40 kHz to 10 MHz

- Precision load current sharing

- 5-bit programmable from 3.5V to 1.3V

- VID code compatible to VRM 8.X specification

- Output voltage is 2.0V for VID code 11111

- Selectable internal or external clock

- Digital 16-step soft start

- Input under-voltage lock-out, over-current protection

#### **Applications**

- Servers and workstations

- High current, ultra-fast transient microprocessors

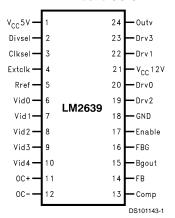

## **Pin Configuration**

#### 24-Pin Plastic SOIC

Top View See NS Package Number M24B

M II™ is a trademark of Cyrix Corporation a wholly owned subsidiary of National Semiconductor Corporation. Pentium II™ is a trademark of Intel Corporation. Kg™ is a trademark of Advanced Micro Devices, Inc.

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{\rm CC}$ 5V 7V 20V 20V Junction Temperature 125°C Power Dissipation (Note 2) 1.6W

Storage Temperature -65°C to +150°C

ESD Susceptibility (Note 8) 2 kV

Soldering Time, Temperature 10 sec., 300°C

### **Operating Ratings** (Note 1)

V<sub>CC</sub> 4.75V to 5.25V Junction Temperature Range 0°C to 70°C

#### **Electrical Characteristics**

$V_{CC}5V = 5V$ ,  $V_{CC}12V = 12V$  unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire operating temperature range.

| Symbol              | Parameter                                                                            | Conditions                                                      | Min            | Тур       | Max          | Units |  |

|---------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|-----------|--------------|-------|--|

| Vcc5V               | V <sub>CC</sub> 5V Pin Voltage                                                       |                                                                 | 4.5            | 5.0       | 5.5          | V     |  |

| Vcc12V              | V <sub>CC</sub> 12V Pin Voltage                                                      |                                                                 | 10.0           | 12.0 18.0 |              | V     |  |

| V <sub>DACOUT</sub> | 5-bit DAC Output Voltage                                                             | (Note 3)                                                        | <i>N</i> –1%   | Ν         | N+1%         |       |  |

|                     |                                                                                      |                                                                 | <i>N</i> –1.5% | N         | N+1.5%       | V     |  |

| I <sub>CC</sub> 12V | Quiescent V <sub>CC</sub> 12V Current Enable = 5V, VID = 00001, DRV Outputs Floating |                                                                 | 1.3            | 3         | mA           |       |  |

| I <sub>CC</sub> 5V  | Operating V <sub>CC</sub> 5V Current                                                 | V <sub>OUT</sub> = 2.00V                                        |                | 4.3       | 8            | mA    |  |

| V <sub>REF</sub>    | Rref Pin Voltage                                                                     |                                                                 |                | 1.225     |              | V     |  |

| V <sub>INL</sub>    | Vid0:4, Clksel, Divsel, and                                                          | Logic Low (Note 4)                                              |                | 1.8       | 1.5          | V     |  |

| V <sub>INH</sub>    | Enable Pins Logic Threshold                                                          | Logic High (Note 5)                                             | 3.5            | 2.8       |              | V     |  |

| I <sub>INL</sub>    | Vid0:4 and Enable Pins Internal Pullup Current                                       |                                                                 | 60             | 100       | 140          | μΑ    |  |

|                     | Clksel, Divsel Pins Internal<br>Pullup Current                                       | The Corresponding Pin = 0V                                      | -10            | 0         | 10           |       |  |

|                     | Gate Driver Resistance When Sinking Current                                          | $I_{SINK} = 50 \mu A, V_{CC} 12V = 14V$                         |                | 12        |              | Ω     |  |

| V <sub>DRV</sub>    | DRV0:3 Output Voltage                                                                | $I_{DRV} = 10 \text{ mA}, V_{CC}12V = 14V,$<br>OutV = 12V or 5V | OutV –<br>0.3V | OutV      | OutV + 0. 3V | V     |  |

| t <sub>fall</sub>   | DRV0:3 Fall Time                                                                     | (Note 6)                                                        |                | 7         |              | ns    |  |

| I <sub>SRC</sub>    | DRV0:3 Source Current                                                                | DRV0:3 = 0V, $V_{CC}12V = 14V$ ,<br>OutV = 5V                   | 40             | 60        |              | mA    |  |

| I <sub>SINK</sub>   | DRV0:3 Sink Current                                                                  | DRV0:3 = 5V, $V_{CC}12V = 14V$ ,<br>OutV = 5V                   | 90             | 160       | 250          | mA    |  |

|                     | B <sub>qOUT</sub> Voltage                                                            | Current Limit Not Activated                                     |                | 4         |              |       |  |

|                     |                                                                                      | Current Limit Activated                                         |                | 0         |              | V     |  |

| I <sub>FB</sub>     | FB Pin Bias Current                                                                  | FB = 2V                                                         |                | 30        |              | nA    |  |

|                     | B <sub>qOUT</sub> Sink Current                                                       | B <sub>qOUT</sub> = 1V                                          | 1.0            | 2.4       | 5            | mA    |  |

| F <sub>osc</sub>    | Oscillator Frequency                                                                 | $8.02k\Omega$ from Rref Pin to Ground                           | 7.0            | 8.0       | 8.7          | MHz   |  |

| $\Delta_{D}$        | DRV0:3 Duty Cycle Match                                                              | Duty Cycle = 50%                                                | -1             |           | +1           | %     |  |

| $\Delta_{ph}$       | DRV0:3 Phase Accuracy                                                                | Duty Cycle = 50%, F <sub>clock</sub> = 8<br>MHz                 | -1             |           | +1           | Deg   |  |

| T <sub>off</sub>    |                                                                                      | Divide by 4                                                     |                | 22        |              |       |  |

| T <sub>off</sub>    | PWM Off time                                                                         | Divide by 3                                                     | 22             |           |              | %     |  |

| OutV                | Drive Voltage Range                                                                  | Output Freq.= 2MHz, V <sub>O</sub> = 2.00V                      | 0              | 12        | Vcc12        | V     |  |

www.national.com 2

#### **Electrical Characteristics** (Continued)

$V_{CC}5V = 5V$ ,  $V_{CC}12V = 12V$  unless otherwise specified. Typicals and limits appearing in plain type apply for  $T_A = T_J = +25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire operating temperature range.

| Symbol               | Parameter                                    | Conditions                               | Min | Тур     | Max<br>12  | Units<br>V |  |

|----------------------|----------------------------------------------|------------------------------------------|-----|---------|------------|------------|--|

| V <sub>OCC_CM</sub>  | Over-current Comparator<br>Common Mode Range |                                          | 3   |         |            |            |  |

| IB_OC+               | OC+ Input Bias Current                       | V <sub>IN</sub> = 5V, OC+ = 5V, OC- = 4V | 100 | 145     | 145 200 µA |            |  |

| IB_OC-               | OC- Input Bias Current                       | V <sub>IN</sub> = 5V, OC+ = 6V, OC- = 5V | 85  | 125 165 |            | μА         |  |

| V <sub>os_occ</sub>  | Over-current Comparator Input                | V <sub>IN</sub> = 5V                     | 2   | 16      | 42         | mV         |  |

|                      | Offset Voltage                               | V <sub>IN</sub> = 12V                    |     | 21      |            |            |  |

| D <sub>MAX</sub>     | Maximun Duty Cycle                           | FB = 0V                                  |     | 78      |            | %          |  |

| gm                   | Error Amplifier Transconductance             |                                          |     | 1.36    |            | mmho       |  |

| V <sub>ramp</sub>    | Ramp Signal Peak-to-Peak<br>Amplitude        |                                          |     | 2       |            | V          |  |

| I <sub>comp</sub>    | COMP Pin Source Current                      |                                          | 250 | 400     | 550        | μΑ         |  |

| I <sub>comp</sub>    | COMP Pin Sink Current                        |                                          | 160 | 280     | 400        | μΑ         |  |

| V <sub>comp_hi</sub> | COMP Pin High Clamp                          |                                          |     | 2.9     |            | V          |  |

| V <sub>comp_lo</sub> | COMP Pin Low Clamp                           |                                          |     | 0.19    |            | V          |  |

| V <sub>POR</sub>     | Power On Reset Trip Point                    | Vcc5V Pin Voltage Rising                 |     | 4.0     |            | V          |  |

|                      |                                              | Vcc5V Pin Voltage Falling                |     | 3.6     |            | ] v        |  |

|                      | Vcc12V Minimum Working<br>Voltage            | (Note 7)                                 |     | 3.8     |            | V          |  |

| t <sub>ss</sub>      | Soft Start Delay                             | F <sub>OSC</sub> = 8MHz                  |     | 1.6     |            | ms         |  |

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating ratings do not imply guaranteed performance limits.

Note 2: Maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{JMAX}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{MAX} = (T_{JMAX} - T_A)\theta_{JA}$ . The junction-to-ambient thermal resistance,  $\theta_{JA}$ , for LM2639 is 78°C/W. For a  $T_{JMAX}$  of 150°C and  $T_A$  of 25°C, the maximum allowable power dissipation is 1.6W.

Note 3: The letter N stands for the typical output voltages appearing in  $italic\ boldface$  type in  $Table\ 1$ .

Note 4: Max value of logic low means any voltage below this value is guaranteed to be taken as logic low whereas a voltage higher than this value is not guaranteed to be taken as a logic low.

Note 5: Min value of logic high means any voltage above this value is guaranteed to be taken as logic high whereas a voltage lower than this value is not guaranteed to be taken as a logic high.

Note 6: When driving bipolar FET drivers in the typical application circuit.

Note 7: When Vcc12V pin goes below this voltage, all DRV pins go to 0V.

Note 8: ESD ratings for pins DRV0, DRV1, DRV2 and DRV3 is 1kV. ESD rating for all other pins is 2kV.

## Electrical Characteristics (Continued)

TABLE 1. 5-Bit DAC Output Voltage Table

| Symbol              | Parameter                                         | Conditions     | Typical | Units |

|---------------------|---------------------------------------------------|----------------|---------|-------|

| V <sub>DACOUT</sub> | 5-Bit DAC Output Voltages for Different VID Codes | VID4:0 = 01111 | 1.30    | V     |

|                     |                                                   | VID4:0 = 01110 | 1.35    | ]     |

|                     |                                                   | VID4:0 = 01101 | 1.40    | 1     |

|                     |                                                   | VID4:0 = 01100 | 1.45    | 1     |

|                     |                                                   | VID4:0 = 01011 | 1.50    | 1     |

|                     |                                                   | VID4:0 = 01010 | 1.55    | 1     |

|                     |                                                   | VID4:0 = 01001 | 1.60    | 1     |

|                     |                                                   | VID4:0 = 01000 | 1.65    | 1     |

|                     |                                                   | VID4:0 = 00111 | 1.70    | 1     |

|                     |                                                   | VID4:0 = 00110 | 1.75    | 1     |

|                     |                                                   | VID4:0 = 00101 | 1.80    |       |

|                     |                                                   | VID4:0 = 00100 | 1.85    | 1     |

|                     |                                                   | VID4:0 = 00011 | 1.90    | 1     |

|                     |                                                   | VID4:0 = 00010 | 1.95    | 1     |

|                     |                                                   | VID4:0 = 00001 | 2.00    | 1     |

|                     |                                                   | VID4:0 = 00000 | 2.05    | 1     |

|                     |                                                   | VID4:0 = 11111 | 2.0     | 1     |

|                     |                                                   | VID4:0 = 11110 | 2.1     | 1     |

|                     |                                                   | VID4:0 = 11101 | 2.2     | 1     |

|                     |                                                   | VID4:0 = 11100 | 2.3     | 1     |

|                     |                                                   | VID4:0 = 11011 | 2.4     | 1     |

|                     |                                                   | VID4:0 = 11010 | 2.5     | 1     |

|                     |                                                   | VID4:0 = 11001 | 2.6     | 1     |

|                     |                                                   | VID4:0 = 11000 | 2.7     | 1     |

|                     |                                                   | VID4:0 = 10111 | 2.8     | 1     |

|                     |                                                   | VID4:0 = 10110 | 2.9     | 1     |

|                     |                                                   | VID4:0 = 10101 | 3.0     | 1     |

|                     |                                                   | VID4:0 = 10100 | 3.1     | 1     |

|                     |                                                   | VID4:0 = 10011 | 3.2     | 1     |

|                     |                                                   | VID4:0 = 10010 | 3.3     | 1     |

|                     |                                                   | VID4:0 = 10001 | 3.4     |       |

|                     |                                                   | VID4:0 = 10000 | 3.5     | 1     |

www.national.com

## **Pin Description**

| Pin | Pin Name | Pin Function                                                                                                                                                         |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | Vcc5V    | Supply Voltage Input (5V nominal)                                                                                                                                    |  |

| 2   | Divsel   | Selects Phase Mode. Logic low selects 4 phase. Logic high selects 3 phase. 2 phase operation is achieved by using 2 outputs in 4 phase mode.                         |  |

| 3   | Clksel   | Clock Select: Logic high selects internal clock. Logic low selects external clock.                                                                                   |  |

| 4   | Extclk   | External Clock Input. Output frequency = Clock Input / No. of Phases. Connect to Vcc5V to select internal clock.                                                     |  |

| 5   | Rref     | Connects to external reference resistor. Sets the operating frequency of the internal clock and the ramp time for the PWM. Reference voltage at this pin is 1.26V.   |  |

| 6   | Vid0     | 5-Bit DAC Input (LSB).                                                                                                                                               |  |

| 7   | Vid1     | 5-Bit DAC Input.                                                                                                                                                     |  |

| 8   | Vid2     | 5-Bit DAC Input.                                                                                                                                                     |  |

| 9   | Vid3     | 5-Bit DAC Input.                                                                                                                                                     |  |

| 10  | Vid4     | 5-Bit DAC Input (MSB)                                                                                                                                                |  |

| 11  | OC+      | Over-current Comparator. Non-inverting input.                                                                                                                        |  |

| 12  | OC-      | Over-current Comparator. Inverting input.                                                                                                                            |  |

| 13  | COMP     | Compensation Pin. This is the output of the internal transconductance amplifier.  Compensation network should be connected between this pin and feedback ground FBG. |  |

| 14  | FB       | Feedback Input. Normally Kelvin connected to supply output.                                                                                                          |  |

| 15  | Bgout    | Current Limit Flag. Goes to logic low when current limit is activated. When over-current condition is removed, this pin is weakly pulled up to Vcc5V.                |  |

| 16  | FBG      | Feedback Ground. This pin should be connected to the ground at the supply output.                                                                                    |  |

| 17  | ENABLE   | Output Enable Pin. Tie to logic high to enable and logic low to disable.                                                                                             |  |

| 18  | GND      | Power Ground Pin.                                                                                                                                                    |  |

| 19  | DRV2     | Phase 2 Output.                                                                                                                                                      |  |

| 20  | DRV0     | Phase 0 Output.                                                                                                                                                      |  |

| 21  | Vcc12V   | Supply Voltage for FET Drivers DRV0:3.                                                                                                                               |  |

| 22  | DRV1     | Phase 1 Output.                                                                                                                                                      |  |

| 23  | DRV3     | Phase 3 Output.                                                                                                                                                      |  |

| 24  | OutV     | Sets the maximum DRV0:3 drive voltage to reduce switching loss in external FET's.                                                                                    |  |

5 www.national.com

# **Block Diagram** V<sub>CC</sub> 12V DS101143-2 DRV2 DRV3 COMP DRVO DRV1 OUTV GND Output Driver Output Driver Output Driver V<sub>CC</sub> 12V Under Voltage Lockout Logic Logic Logic Logic Current Bias fast comparators 4 Phase Ramps 16-Step Softstart Hold Oscillator 40 kHz to 10 MHz Power On Reset and Under Voltage Detect 5-Bit DAC Oscillator Bias FBG DENABLE Divsel Rref

6

# **Typical Application** 1.3V - 3.5V, 25A 22 μ 100 1210 Υ5V X12 1 20N03 300 nH 1 20N03 300 nH 14 20NO3 300 nH 22 μ 100/ 100/ 100/ 100/ 100/ 100/ 22 μ 100/ 100/ 8.2k V<sub>CC</sub>12V Drv0 Drv2 GND FBG Drv1 t: These resistors are optional. Pin Outv can float. LM2639 Extclk Nref Vid0 Vid2 Vid3 Vid4 OC+ +12V

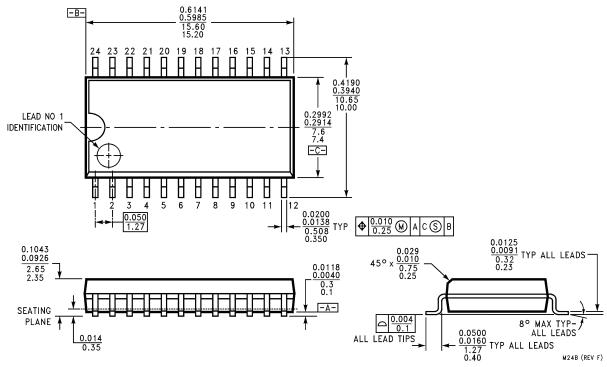

#### Physical Dimensions inches (millimeters) unless otherwise noted

24-Lead Small Outline Package Order Number LM2639M NS Package Number M24B

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor** Tel: 81-3-5639-7560

Fax: 81-3-5639-7507