LTC1400

Complete SO-8, 12-Bit, 400ksps ADC with Shutdown

The LTC®1400 is a complete 400ksps, 12-bit A/D con-

verter which draws only 75mW from a 5V or  $\pm$  5V supplies.

This easy-to-use device comes complete with a 200ns

sample-and-hold and a precision reference. Unipolar and

bipolar conversion modes add to the flexibility of the ADC.

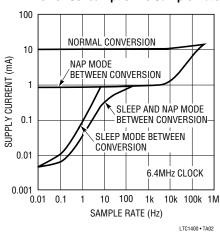

The LTC1400 has two power saving modes: Nap and

Sleep. In Nap mode, it consumes only 6mW of power and

can wake up and convert immediately. In the Sleep mode,

it consumes 30µW of power typically. Upon power-up

from Sleep mode, a reference ready (REFRDY) signal is

available in the serial data word to indicate that the

The LTC1400 converts 0V to 4.096V unipolar inputs from a single 5V supply and  $\pm 2.048V$  bipolar inputs from  $\pm 5V$

reference has settled and the chip is ready to convert.

DESCRIPTION

# FEATURES

- Complete 12-Bit ADC in SO-8

- Single Supply 5V or ±5V Operation

- Sample Rate: 400ksps

- Power Dissipation: 75mW (Typ)

- 72dB S/(N + D) and -80dB THD at Nyquist

- No Missing Codes over Temperature

- Nap Mode with Instant Wake-Up: 6mW

- Sleep Mode: 30µW

- High Impedance Analog Input

- Input Range (1mV/LSB): 0V to 4.096 or ± 2.048V

- Internal Reference Can Be Overdriven Externally

- 3-Wire Interface to DSPs and Processors (SPI and MICROWIRE<sup>TM</sup> Compatible)

# **APPLICATIONS**

- High Speed Data Acquisition

- Digital Signal Processing

- Multiplexed Data Acquisition Systems

- Audio and Telecom Processing

- Digital Radio

- Spectrum Analysis

- Low Power and Battery-Operated Systems

- Handheld or Portable Instruments

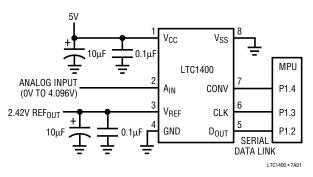

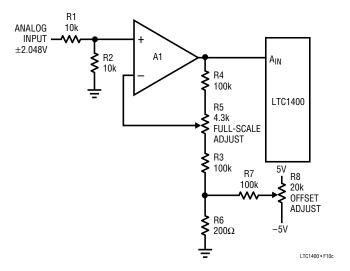

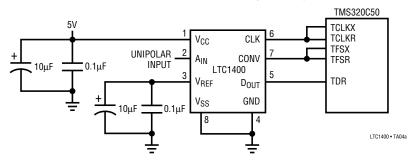

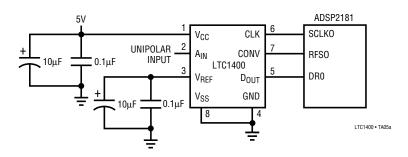

# TYPICAL APPLICATION

Single 5V Supply, 400kHz, 12-Bit Sampling A/D Converter

### supplies. Maximum DC specs include ±1LSB INL, ±1LSB

DNL and 45ppm/°C drift over temperature. Guaranteed AC performance includes 70dB S/(N + D) and -76dB THD at an input frequency of 100kHz, over temperature.

The 3-wire serial port allows compact and efficient data transfer to a wide range of microprocessors, microcontrollers and DSPs.

∠, LTC and LT are registered trademarks of Linear Technology Corporation. MICROWIRE is a trademark of National Semiconductor Corp.

#### Power Consumption vs Sample Rate

# **ABSOLUTE MAXIMUM RATINGS**

| (Notes 1, 2)                                               |

|------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> ) 7V                       |

| Negative Supply Voltage (V <sub>SS</sub> ) –6V to GND      |

| Total Supply Voltage (V <sub>CC</sub> to V <sub>SS</sub> ) |

| Bipolar Operation Only 12V                                 |

| Analog Input Voltage (Note 3)                              |

| Unipolar Operation $-0.3V$ to (V <sub>CC</sub> + 0.3V)     |

| Bipolar Operation $(V_{SS} - 0.3V)$ to $(V_{CC} + 0.3V)$   |

| Digital Input Voltage (Note 4)                             |

| Unipolar Operation–0.3V to 12V                             |

| Bipolar Operation (V <sub>SS</sub> – 0.3V) to 12V          |

| Digital Output Voltage                                     |

| Unipolar Operation $-0.3V$ to $(V_{CC} + 0.3V)$            |

| Bipolar Operation $(V_{SS} - 0.3V)$ to $(V_{CC} + 0.3V)$   |

| Power Dissipation                                          |

| Operation Temperature Range                                |

| LTC1400C                                                   |

| LTC1400I –40°C to 85°C                                     |

| Storage Temperature Range –65°C to 150°C                   |

| Lead Temperature (Soldering, 10 sec)                       |

|                                                            |

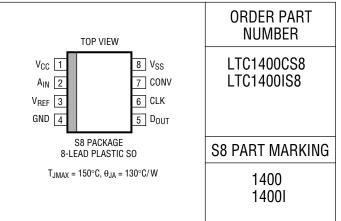

# PACKAGE/ORDER INFORMATION

Consult factory for PDIP packages and Military grade parts.

### POWER REQUIREMENTS (Note 5)

| SYMBOL          | PARAMETER                        | CONDITIONS                                           |   | MIN   | ТҮР | MAX   | UNITS |

|-----------------|----------------------------------|------------------------------------------------------|---|-------|-----|-------|-------|

| V <sub>CC</sub> | Positive Supply Voltage (Note 6) | Unipolar                                             |   | 4.75  |     | 5.25  | V     |

|                 |                                  | Bipolar                                              |   | 4.75  |     | 5.25  | V     |

| V <sub>SS</sub> | Negative Supply Voltage (Note 6) | Bipolar Only                                         |   | -2.45 |     | -5.25 | V     |

| I <sub>CC</sub> | Positive Supply Current          | f <sub>SAMPLE</sub> = 400ksps                        | • |       | 15  | 30    | mA    |

|                 |                                  | Nap Mode                                             | • |       | 1.0 | 3.0   | mA    |

|                 |                                  | Sleep Mode                                           | • |       | 5.0 | 20.0  | μA    |

| I <sub>SS</sub> | Negative Supply Current          | f <sub>SAMPLE</sub> = 400ksps, V <sub>SS</sub> = -5V | • |       | 0.3 | 0.6   | mA    |

|                 |                                  | Nap Mode                                             | • |       | 0.2 | 0.5   | mA    |

|                 |                                  | Sleep Mode                                           | • |       | 1   | 5     | μA    |

| P <sub>D</sub>  | Power Dissipation                | f <sub>SAMPLE</sub> = 400ksps                        | • |       | 75  | 160   | mW    |

|                 |                                  | Nap Mode                                             | • |       | 6   | 20    | mW    |

|                 |                                  | Sleep Mode                                           | • |       | 30  | 125   | μW    |

# ANALOG INPUT (Note 5)

| SYMBOL          | PARAMETER                    | CONDITIONS                                                                                                                                             |    | MIN | ТҮР                  | MAX | UNITS    |

|-----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|----------------------|-----|----------|

| V <sub>IN</sub> | Analog Input Range (Note 7)  | $\begin{array}{l} 4.75V \leq V_{CC} \leq 5.25V \; (Unipolar) \\ 4.75V \leq V_{CC} \leq 5.25V, -5.25V \leq V_{SS} \leq -2.45V \; (Bipolar) \end{array}$ | •• |     | 0 to 4.096<br>±2.048 |     | V<br>V   |

| IIN             | Analog Input Leakage Current | During Conversions (Hold Mode)                                                                                                                         | •  |     |                      | ±1  | μA       |

| C <sub>IN</sub> | Analog Input Capacitance     | Between Conversions (Sample Mode)<br>During Conversions (Hold Mode)                                                                                    |    |     | 45<br>5              |     | pF<br>pF |

# **CONVERTER CHARACTERISTICS** With internal reference (Notes 5, 8)

| PARAMETER                     | CONDITIONS         |   | MIN | ТҮР | MAX      | UNITS      |

|-------------------------------|--------------------|---|-----|-----|----------|------------|

| Resolution (No Missing Codes) |                    | • | 12  |     |          | Bits       |

| Integral Linearity Error      | (Note 9)           | • |     |     | ±1       | LSB        |

| Differential Linearity Error  |                    | • |     |     | ±1       | LSB        |

| Offset Error                  | (Note 10)          | • |     |     | ±6<br>±8 | LSB<br>LSB |

| Full-Scale Error              |                    |   |     |     | ±15      | LSB        |

| Full-Scale Tempco             | $I_{OUT(REF)} = 0$ | • |     | ±10 | ±45      | ppm/°C     |

### **DYNAMIC ACCURACY** $V_{CC} = 5V, V_{SS} = -5V, f_{SAMPLE} = 400 \text{kHz}$

| SYMBOL    | PARAMETER                                       | CONDITIONS                                                                                                              |   | MIN      | ТҮР        | MAX | UNITS    |

|-----------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|----------|------------|-----|----------|

| S/(N + D) | Signal-to-Noise<br>Plus Distortion Ratio        | 100kHz Input Signal Commercial<br>Industrial                                                                            | • | 70<br>69 | 72         |     | dB<br>dB |

|           |                                                 | 200kHz Input Signal                                                                                                     |   |          | 72         |     | dB       |

| THD       | Total Harmonic Distortion<br>Up to 5th Harmonic | 100kHz Input Signal<br>200kHz Input Signal                                                                              | • |          | -82<br>-80 | -76 | dB<br>dB |

|           | Peak Harmonic or<br>Spurious Noise              | 100kHz Input Signal<br>200kHz Input Signal                                                                              | • |          | -84<br>-82 | -76 | dB<br>dB |

| IMD       | Intermodulation Distortion                      | f <sub>IN1</sub> = 99.51kHz, f <sub>IN2</sub> = 102.44kHz<br>f <sub>IN1</sub> = 199.12kHz, f <sub>IN2</sub> = 202.05kHz |   |          | -82<br>-70 |     | dB<br>dB |

|           | Full Power Bandwidth                            |                                                                                                                         |   |          | 4          |     | MHz      |

|           | Full Linear Bandwidth (S/(N + D) $\ge$ 68dB)    |                                                                                                                         |   |          | 900        |     | kHz      |

# INTERNAL REFERENCE CHARACTERISTICS (Note 5)

| PARAMETER                                              | CONDITIONS                                             |   | MIN   | ТҮР          | MAX   | UNITS          |

|--------------------------------------------------------|--------------------------------------------------------|---|-------|--------------|-------|----------------|

| V <sub>REF</sub> Output Voltage                        | I <sub>OUT</sub> = 0                                   |   | 2.400 | 2.420        | 2.440 | V              |

| V <sub>REF</sub> Output Tempco                         | $I_{OUT} = 0$                                          | • |       | ±10          | ±45   | ppm/°C         |

| V <sub>REF</sub> Line Regulation                       | $4.75V \le V_{CC} \le 5.25V - 5.25V \le V_{SS} \le 0V$ |   |       | 0.01<br>0.01 |       | LSB/V<br>LSB/V |

| V <sub>REF</sub> Load Regulation                       | $0 \le  I_{OUT}  \le 1 \text{mA}$                      |   |       | 2            |       | LSB/mA         |

| V <sub>REF</sub> Wake-Up Time from Sleep Mode (Note 7) | $C_{VREF} = 10 \mu F$                                  |   |       | 4            |       | ms             |

# DIGITAL INPUTS AND OUTPUTS (Note 5)

| SYMBOL          | PARAMETER                 | CONDITIONS                                                            |   | MIN | ТҮР          | МАХ | UNITS  |

|-----------------|---------------------------|-----------------------------------------------------------------------|---|-----|--------------|-----|--------|

| VIH             | High Level Input Voltage  | V <sub>CC</sub> = 5.25V                                               | • | 2.0 |              |     | V      |

| V <sub>IL</sub> | Low Level Input Voltage   | V <sub>CC</sub> = 4.75V                                               | • |     |              | 0.8 | V      |

| I <sub>IN</sub> | Digital Input Current     | $V_{IN} = 0V$ to $V_{CC}$                                             | • |     |              | ±10 | μA     |

| CIN             | Digital Input Capacitance |                                                                       |   |     | 5            |     | pF     |

| V <sub>OH</sub> | High Level Output Voltage | $V_{CC} = 4.75V, I_0 = -10\mu A$<br>$V_{CC} = 4.75V, I_0 = -200\mu A$ | • | 4.0 | 4.7          |     | V<br>V |

| V <sub>OL</sub> | Low Level Output Voltage  | $V_{CC} = 4.75V, I_0 = 160\mu A$<br>$V_{CC} = 4.75V, I_0 = 1.6m A$    | • |     | 0.05<br>0.10 | 0.4 | V<br>V |

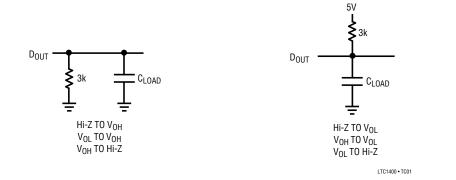

### DIGITAL INPUTS AND OUTPUTS (Note 5)

| SYMBOL            | PARAMETER                                         | CONDITIONS                         |   | MIN | ТҮР | MAX | UNITS |

|-------------------|---------------------------------------------------|------------------------------------|---|-----|-----|-----|-------|

| I <sub>OZ</sub>   | Hi-Z Output Leakage D <sub>OUT</sub>              | $V_{OUT} = 0V$ to $V_{CC}$         | • |     |     | ±10 | μA    |

| C <sub>OZ</sub>   | Hi-Z Output Capacitance D <sub>OUT</sub> (Note 7) |                                    |   |     | 15  |     | pF    |

| ISOURCE           | Output Source Current                             | V <sub>OUT</sub> = 0               |   |     | -10 |     | mA    |

| I <sub>SINK</sub> | Output Sink Current                               | V <sub>OUT</sub> = V <sub>CC</sub> |   |     | 10  |     | mA    |

# TIMING CHARACTERISTICS (Note 5)

| SYMBOL                   | PARAMETER                                                                | CONDITIONS                |   | MIN | ТҮР        | MAX        | UNITS    |

|--------------------------|--------------------------------------------------------------------------|---------------------------|---|-----|------------|------------|----------|

| f <sub>SAMPLE(MAX)</sub> | Maximum Sampling Frequency                                               | (Note 6)                  | • | 400 |            |            | kHz      |

| t <sub>CONV</sub>        | Conversion Time                                                          | f <sub>CLK</sub> = 6.4MHz | • |     |            | 2.1        | μs       |

| t <sub>ACQ</sub>         | Acquisition Time (Unipolar Mode)<br>(Bipolar Mode V <sub>SS</sub> = -5V) | (Note 7)                  | • |     | 230<br>200 | 300<br>270 | ns<br>ns |

| f <sub>CLK</sub>         | CLK Frequency                                                            |                           | • | 0.1 |            | 6.4        | MHz      |

| t <sub>CLK</sub>         | CLK Pulse Width                                                          | (Note 7)                  | • | 50  |            |            | ns       |

| t <sub>WK(NAP)</sub>     | Time to Wake Up from Nap Mode                                            | (Note 7)                  |   |     | 350        |            | ns       |

| t <sub>1</sub>           | CLK Pulse Width to Return to Active Mode                                 |                           | • | 50  |            |            | ns       |

| t <sub>2</sub>           | CONV↑ to CLK↑ Setup Time                                                 |                           | • | 80  |            |            | ns       |

| t <sub>3</sub>           | CONV <sup>↑</sup> After Leading CLK <sup>↑</sup>                         |                           | • | 0   |            |            | ns       |

| t <sub>4</sub>           | CONV Pulse Width                                                         | (Note 11)                 | • | 50  |            |            | ns       |

| t <sub>5</sub>           | Time from CLK↑to Sample Mode                                             | (Note 7)                  |   |     | 80         |            | ns       |

| t <sub>6</sub>           | Aperture Delay of Sample-and-Hold                                        | Jitter < 50ps (Note 7)    | • |     | 45         | 65         | ns       |

| t <sub>7</sub>           |                                                                          |                           | • |     | 265<br>235 | 385<br>355 | ns<br>ns |

| t <sub>8</sub>           | Delay Time, CLK↑ to D <sub>OUT</sub> Valid                               | C <sub>LOAD</sub> = 20pF  | • |     | 40         | 80         | ns       |

| t <sub>9</sub>           | Delay Time, CLK↑ to D <sub>OUT</sub> Hi-Z                                | C <sub>LOAD</sub> = 20pF  | • |     | 40         | 80         | ns       |

| t <sub>10</sub>          | Time from Previous Data Remains Valid After CLK↑                         | C <sub>LOAD</sub> = 20pF  | • | 14  | 25         |            | ns       |

The  $\bullet$  denotes specifications which apply over the full operating temperature range; all other limits and typicals T<sub>A</sub> = 25°C.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: All voltage values are with respect to GND.

**Note 3:** When these pin voltages are taken below  $V_{SS}$  (ground for unipolar mode) or above  $V_{CC}$ , they will be clamped by internal diodes. This product can handle input currents greater than 40mA below  $V_{SS}$  (ground for unipolar mode) or above  $V_{CC}$  without latch-up.

**Note 4:** When these pin voltages are taken below V<sub>SS</sub> (ground for unipolar mode), they will be clamped by internal diodes. This product can handle input currents greater than 40mA below V<sub>SS</sub> (ground for unipolar mode) without latch-up. These pins are not clamped to V<sub>CC</sub>.

Note 5:  $V_{CC}$  = 5V,  $f_{SAMPLE}$  = 400kHz,  $t_r$  =  $t_f$  = 5ns unless otherwise specified.

Note 6: Recommended operating conditions.

Note 7: Guaranteed by design, not subject to test.

**Note 8:** Linearity, offset and full-scale specifications apply for unipolar and bipolar modes.

**Note 9:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

**Note 10:** Bipolar offset is the offset voltage measured from -0.5LSB when the output code flickers between 0000 0000 0000 and 1111 1111 1111.

**Note 11:** The rising edge of CONV starts a conversion. If CONV returns low at a bit decision point during the conversion, it can create small errors. For best performance ensure that CONV returns low either within 120ns after conversion starts (i.e., before the first bit decision) or after the 14 clock cycle. (Figure 13 Timing Diagram).

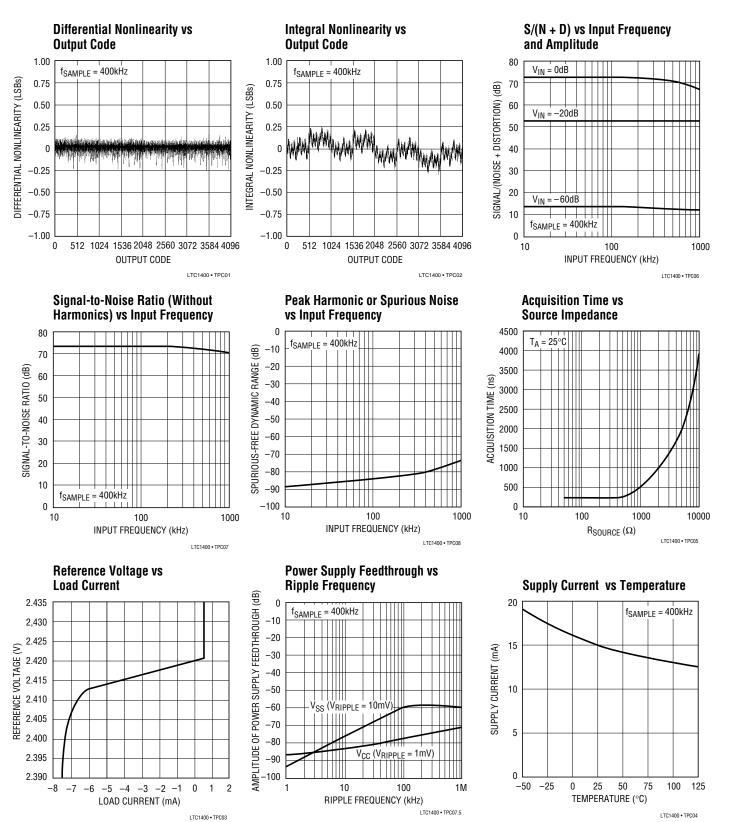

# TYPICAL PERFORMANCE CHARACTERISTICS

# PIN FUNCTIONS

$V_{CC}$  (Pin 1): Positive Supply, 5V. Bypass to GND (10 $\mu$ F tantalum in parallel with 0.1 $\mu$ F ceramic).

**A<sub>IN</sub> (Pin 2):** Analog Input. 0V to 4.096V (Unipolar), ±2.048V (Bipolar).

$V_{REF}$  (Pin 3): 2.42V Reference Output. Bypass to GND (10µF tantalum in parallel with 0.1µF ceramic).

**GND (Pin 4):** Ground. GND should be tied directly to an analog ground plane.

**D**<sub>OUT</sub> (**Pin 5**): The A/D conversion result is shifted out from this pin.

**CLK (Pin 6):** Clock. This clock synchronizes the serial data transfer. A minimum CLK pulse of 50ns will cause the ADC to wake up from Nap or Sleep mode.

**CONV (Pin 7):** Conversion Start Signal. This active high signal starts a conversion on its rising edge. Keeping CLK low and pulsing CONV two/four times will put the ADC into Nap/Sleep mode.

$V_{SS}$  (Pin 8): Negative Supply. –5V for bipolar operation. Bypass to GND with 0.1  $\mu F$  ceramic.  $V_{SS}$  should be tied to GND for unipolar operation.

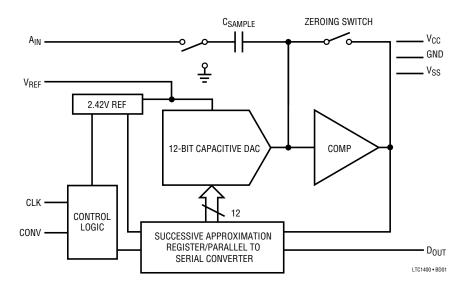

# FUNCTIONAL BLOCK DIAGRAM

# **TEST CIRCUITS**

#### **Conversion Details**

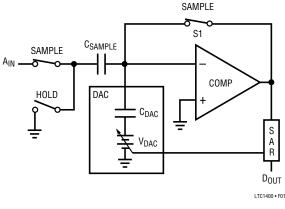

The LTC1400 uses a successive approximation algorithm and an internal sample-and-hold circuit to convert an analog signal to a 12-bit serial output based on a precision internal reference. The control logic provides easy interface to microprocessors and DSPs through 3-wire connections.

A rising edge on the CONV input starts a conversion. At the start of a conversion the successive approximation register (SAR) is reset. Once a conversion cycle has begun it cannot be restarted.

During conversion, the internal 12-bit capacitive DAC output is sequenced by the SAR from the most significant bit (MSB) to the least significant bit (LSB). Referring to Figure 1, the AIN input connects to the sample-and-hold capacitor during the acquired phase and the comparator offset is nulled by the feedback switch. In this acquire phase, it typically takes 200ns for the sample-and-hold capacitor to acquire the analog signal. During the convert phase, the comparator feedback switch opens, putting the comparator into the compare mode. The input switches connect C<sub>SAMPLF</sub> to ground, injecting the analog input charge onto the summing junction. This input charge is successively compared with the binary-weighted charges supplied by the capacitive DAC. Bit decisions are made by the high speed comparator. At the end of a conversion, the DAC output balances the  $A_{IN}$  input charge. The SAR contents (a 12-bit data word) which represent the input voltage, are output through the serial pin  $D_{OUT}$ .

#### **Dynamic Performance**

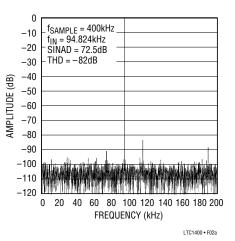

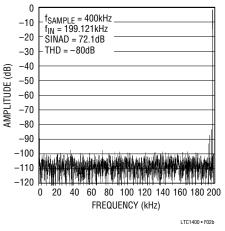

The LTC1400 has excellent high speed sampling capability. FFT (Fast Fourier Transform) test techniques are used to test the ADC's frequency response, distortion and noise at the rated throughput. By applying a low distortion sine wave and analyzing the digital output using an FFT algorithm, the ADC's spectral content can be examined for frequencies outside the fundamental. Figure 2a shows a typical LTC1400 FFT plot.

#### Signal-to-Noise Ratio

The signal-to-noise plus distortion ratio [S/(N + D)] is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other frequency components at the A/D output. The output is band limited to frequencies from DC to half the sampling frequency. Figure 2a shows a typical spectral content with a 400kHz sampling rate and a 100kHz input. The dynamic performance is excellent for input frequencies up to the Nyquist limit of 200kHz as shown in Figure 2b.

Figure 2a. LTC1400 Nonaveraged, 4096 Point FFT Plot with 100kHz Input Frequency in Bipolar Mode

#### **Effective Number of Bits**

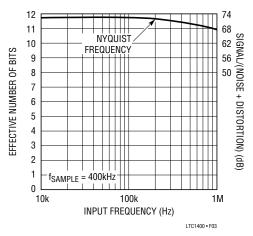

The effective number of bits (ENOBs) is a measurement of the effective resolution of an ADC and is directly related to the S/(N + D) by the equation:

$$N = \frac{S/(N+D) - 1.76}{6.02}$$

Figure 2b. LTC1400 Nonaveraged, 4096 Point FFT Plot with 200kHz Input Frequency in Bipolar Mode

where N is the effective number of bits of resolution and S/(N + D) is expressed in dB. At the maximum sampling rate of 400kHz, the LTC1400 maintains very good ENOBs up to the Nyquist input frequency of 200kHz (refer to Figure 3).

Figure 3. Effective Bits and Signal-to-Noise + Distortion vs Input Frequency in Bipolar Mode

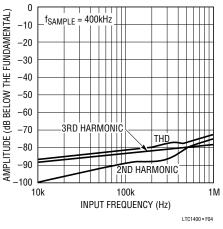

### Total Harmonic Distortion

Total harmonic distortion (THD) is the ratio of the RMS sum of all harmonics of the input signal to the fundamental itself. The out-of-band harmonics alias into the frequency band between DC and half of the sampling frequency. THD is expressed as:

$$THD = 20 \log \frac{\sqrt{V2^2 + V3^2 + V4^2 + \dots Vn^2}}{V1}$$

where V1 is the RMS amplitude of the fundamental frequency and V2 through Vn are the amplitudes of the second through nth harmonics. THD vs input frequency is shown in Figure 4. The LTC1400 has good distortion performance up to the Nyquist frequency and beyond.

Figure 4. Distortion vs Input Frequency in Bipolar Mode

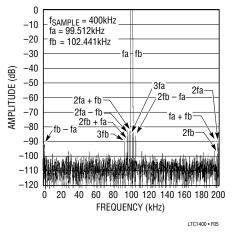

### Intermodulation Distortion

If the ADC input signal consists of more than one spectral component, the ADC transfer function nonlinearity can produce intermodulation distortion (IMD) in addition to THD. IMD is the change in one sinusoidal input caused by the presence of another sinusoidal input at a different frequency.

If two pure sine waves of frequencies fa and fb are applied to the ADC input, nonlinearities in the ADC transfer function can create distortion products at sum and difference frequencies of mfa  $\pm$  nfb, where m and n = 0, 1, 2, 3, etc. For example, the 2nd order IMD terms include (fa + fb) and (fa - fb) while the 3rd order IMD terms includes (2fa + fb), (2fa - fb), (fa + 2fb) and (fa - 2fb). If the two input sine waves are equal in magnitude, the value (in decibels) of the 2nd order IMD products can be expressed by the following formula.

$$IMD(fa \pm fb) = 20log \frac{Amplitude at (fa \pm fb)}{Amplitude at fa}$$

Figure 5. Intermodulation Distortion Plot in Bipolar Mode

Figure 5 shows the IMD performance at a 100kHz input.

### Peak Harmonic or Spurious Noise

The peak harmonic or spurious noise is the largest spectral component excluding the input signal and DC. This value is expressed in decibels relative to the RMS value of a full-scale input signal.

### Full Power and Full Linear Bandwidth

The full power bandwidth is the input frequency at which the amplitude of the reconstructed fundamental is reduced by 3dB for a full-scale input signal.

The full linear bandwidth is the input frequency at which the S/(N + D) has dropped to 68dB (11 effective bits). The LTC1400 has been designed to optimize input bandwidth, allowing the ADC to undersample input signals with frequencies above the converter's Nyquist Frequency. The noise floor stays very low at high frequencies; S/(N + D) becomes dominated by distortion at frequencies far beyond Nyquist.

### **Driving the Analog Input**

The analog input of the LTC1400 is easy to drive. It draws only one small current spike while charging the sampleand-hold capacitor at the end of a conversion. During conversion, the analog input draws only a small leakage current. The only requirement is that the amplifier driving the analog input must settle after the small current spike before the next conversion starts. Any op amp that settles in 200ns to small load current transient will allow maximum speed operation. If a slower op amp is used, more settling time can be provided by increasing the time between conversions. Suitable devices capable of driving the ADC's  $A_{\rm IN}$  input include the LT  $^{\odot}$ 1360 and the LT1363 op amps.

LTC1400 comes with a built-in unipolar/bipolar detection circuit. If  $V_{SS}$  potential is forced below GND, the internal circuitry will automatically switch to bipolar mode.

The following list is a summary of the op amps that are suitable for driving the LTC1400, more detailed information is available in the Linear Technology databooks and the LinearView<sup>™</sup> CD-ROM.

**LT 1215/LT1216:** Dual and quad 23MHz,  $50V/\mu s$  single supply op amps. Single 5V to  $\pm 15V$  supplies, 6.6mA specifications, 90ns settling to 0.5LSB.

**LT1223:** 100MHz video current feedback amplifier.  $\pm$ 5V to  $\pm$ 15V supplies, 6mA supply current. Low distortion up to and above 400kHz. Low noise. Good for AC applications.

**LT1227:** 140MHz video current feedback amplifier.  $\pm$ 5V to  $\pm$ 15V supplies, 10mA supply current. Lowest distortion at frequencies above 400kHz. Low noise. Best for AC applications.

**LT1229/LT1230:** Dual and quad 100MHz current feedback amplifiers.  $\pm 2V$  to  $\pm 15V$  supplies, 6mA supply current each amplifier. Low noise. Good AC specs.

**LT1360:** 37MHz voltage feedback amplifier.  $\pm$ 5V to  $\pm$ 15V supplies. 3.8mA supply current. Good AC and DC specs. 70ns settling to 0.5LSB.

**LT1363:** 50MHz, 450V/ $\mu$ s op amps.  $\pm$ 5V to  $\pm$ 15V supplies. 6.3mA supply current. Good AC and DC specs. 60ns settling to 0.5LSB.

**LT1364/LT1365:** Dual and quad 50MHz, 450V/ $\mu$ s op amps.  $\pm$ 5V to  $\pm$ 15V supplies, 6.3mA supply current per amplifier. 60ns settling to 0.5LSB.

#### **Internal Reference**

The LTC1400 has an on-chip, temperature compensated, curvature corrected, bandgap reference, which is factory

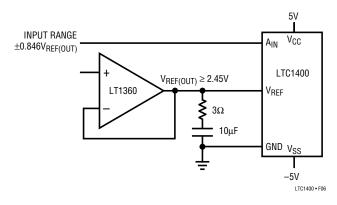

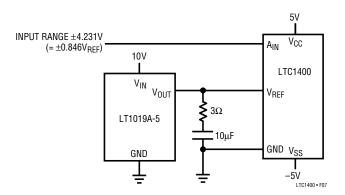

trimmed to 2.42V. It is internally connected to the DAC and is available at Pin 3 to provide up to 1mA of current to an external load. For minimum code transition noise, the reference output should be decoupled with a capacitor to filter wideband noise from the reference (10µF tantalum in parallel with a  $0.1\mu$ F ceramic). The V<sub>BFF</sub> pin can be driven with a DAC or other means to provide input span adjustment in bipolar mode. The V<sub>RFF</sub> pin must be driven to at least 2.45V to prevent conflict with the internal reference. The reference should not be driven to more than 5V. Figure 6 shows an LT 1306 op amp driving the reference pin. Figure 7 shows a typical reference, the LT1019A-5 connected to the LTC1360. This will provide an improved drift (equal to the maximum 5ppm/°C of the LT1019A-5) and a  $\pm 4.231V$  full scale. If V<sub>REF</sub> is forced lower than 2.42V, the REFRDY bit in the serial data output will be forced to low.

Figure 6. Driving the  $V_{REF}$  with the LT1360 Op Amp

### UNIPOLAR/BIPOLAR OPERATION AND ADJUSTMENT

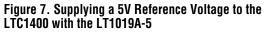

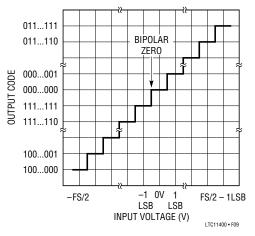

Figure 8 shows the ideal input/output characteristics for the LTC1400. The code transitions occur midway between successive integer LSB values (i.e., 0.5LSB, 1.5LSB, 2.5LSB, ... FS-1.5LSB). The output code is natural binary with 1LSB = 4.096/4096 = 1mV. Figure 9 shows the input/output transfer characteristics for the bipolar mode in two's complement format.

Figure 8. LTC1400 Unipolar Transfer Characteristics

Figure 9. LTC1400 Bipolar Transfer Characteristics

### **Unipolar Offset and Full-Scale Error Adjustments**

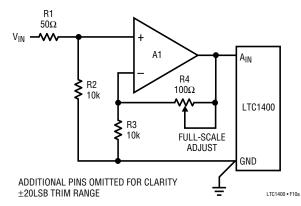

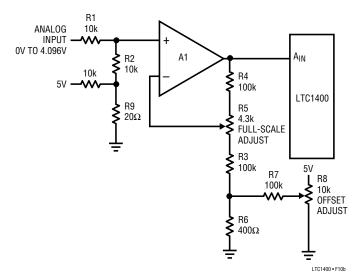

In applications where absolute accuracy is important, offset and full-scale errors can be adjusted to zero. Figure 10a shows the extra components required for full-scale

Figure 10a. LTC1400 Full-Scale Adjust Circuit

Figure 10c. LTC1400 Bipolar Offset and Full-Scale Adjust Circuit

error adjustment. Figure 10b shows offset and full-scale adjustment. Offset error must be adjusted before full-scale error. Zero offset is achieved by applying 0.5mV (i.e., 0.5LSB) at the input and adjusting the offset trim until the LTC1400 output code flickers between 0000 0000 0000 and 0000 0001. For zero full-scale error, apply an analog input of 4.0945V (FS – 1.5LSB or last code transition) at the input and adjust R5 until the LTC1400 output code flickers between 1111 1111 1111 1111

#### **Bipolar Offset and Full-Scale Error Adjustments**

Bipolar offset and full-scale errors are adjusted in a similar fashion to the unipolar case. Bipolar offset error adjustment is achieved by applying an input voltage of -0.5mV (-0.5LSB) to the input in Figure 10c and adjusting the op amp until the ADC output code flickers between 0000 0000 0000 and 1111 1111 1111. For full-scale adjustment, an input voltage of 2.0465V (FS – 1.5LSBs) is applied to the input and R5 is adjusted until the output code flickers between 0111 1111 1110 and 0111 1111 1111.

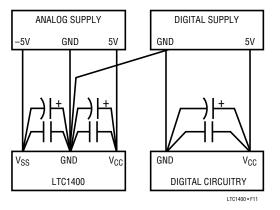

### **BOARD LAYOUT AND BYPASSING**

To obtain the best performance from the LTC1400, a printed circuit board is required. Layout for the printed circuit board should ensure that digital and analog signal lines are separated as much as possible. In particular, care should be taken not to run any digital track alongside an analog signal track or underneath the ADC. The analog input should be screened by GND.

High quality tantalum and ceramic bypass capacitors should be used at the V<sub>CC</sub> and V<sub>REF</sub> pins as shown in the Typical Application on the first page of this data sheet. For the bipolar mode, a  $0.1\mu$ F ceramic provides adequate bypassing for the V<sub>SS</sub> pin. For optimum performance, a  $10\mu$ F surface mount AVX capacitor with a  $0.1\mu$ F ceramic is recommended for the V<sub>CC</sub> and V<sub>REF</sub> pins. The capacitors must be located as close to the pins as possible. The traces connecting the pins and the bypass capacitors must be kept short and should be made as wide as possible. In unipolar mode operation, V<sub>SS</sub> should be isolated from any noise source before shorting to the GND pin.

Input signal leads to  $A_{IN}$  and signal return leads from GND (Pin 4) should be kept as short as possible to minimize noise coupling. In applications where this is not possible, a shielded cable between source and ADC is recommended. Also, since any potential difference in grounds between the signal source and ADC appears as an error voltage in series with the input signal, attention should be paid to reducing the ground circuit impedance as much as possible.

Figure 11. Power Supply Connection

Figure 11 shows the recommended system ground connections. All analog circuitry grounds should be terminated at the LTC1400 GND pin. The ground return from the LTC1400 Pin 4 to the power supply should be low impedance for noise free operation. Digital circuitry grounds must be connected to the digital supply common.

In applications where the ADC data outputs and control signals are connected to a continuously active microprocessor bus, it is possible to get errors in the conversion results. These errors are due to feedthrough from the microprocessor to the successive approximation comparator. The problem can be eliminated by forcing the microprocessor into a Wait state during conversion or by using three-state buffers to isolate the ADC data bus.

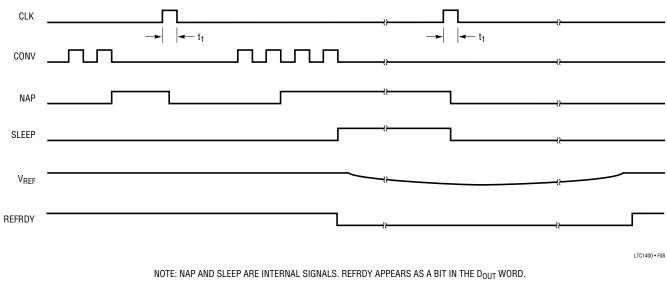

#### **Power-Down Mode**

Upon power-up, the LTC1400 is initialized to the active state and is ready for conversion. However, the chip can be easily placed into the Nap or Sleep mode by exercising the right combination of CLK and CONV signal. In the Nap mode all power is off except the internal reference, which is still active and provides 2.42V output voltage to the other circuitry. In this mode, the ADC draws only 6mW of power instead of 75mW (for minimum power, the logic inputs must be within 500mV of the supply rails). The wake-up time from the Nap mode to the active mode is

Figure 12. Nap Mode and Sleep Mode Waveforms

350ns. In the Sleep mode, power consumption is reduced to a minimum by cutting off the supply to all internal circuitry including the reference. Figure 12 shows the ways to power down the LTC1400. The chip can enter the Nap mode by keeping the CLK signal low and pulsing the CONV signal twice. For Sleep mode operation, CONV signal should be activated four times while CLK is kept low.

The LTC1400 can be returned to active mode easily. The rising edge of CLK will wake-up the LTC1400. During the transition from Sleep mode to active mode, the  $V_{REF}$  voltage ramp-up time is a function of the loading conditions. With a 10µF bypass capacitor, the wake-up time from Sleep mode is typically 4ms. A REFRDY signal will be activated once the reference has settled and is ready for an A/D conversion. This REFRDY bit is output to the D<sub>OUT</sub> pin before the rest of the A/D converted code.

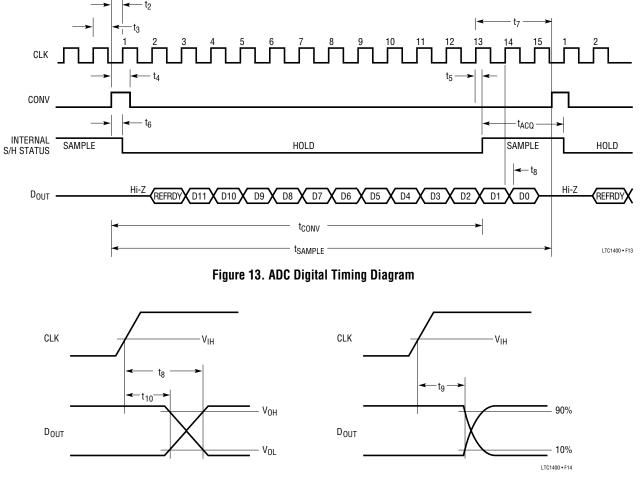

### **DIGITAL INTERFACE**

The digital interface requires only three digital lines. CLK and CONV are both inputs, and the  $D_{OUT}$  output provides the conversion result in serial form.

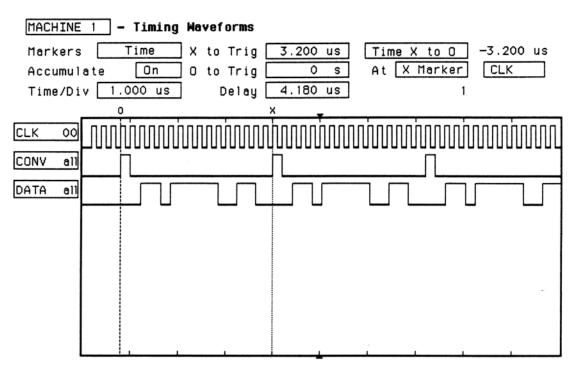

Figure 13 shows the digital timing diagram of the LTC1400 during the A/D conversion. The CONV rising edge starts the conversion. Once initiated, it can not be restarted until the conversion is completed. If the time from CONV signal to CLK rising edge is less than  $t_2$ , the digital output will be delayed by one clock cycle.

The digital output data is updated on the rising edge of the CLK line.  $D_{OUT}$  data should be captured by the receiving system on the rising CLK edge. Data remains valid for a minimum time of  $t_{10}$  after the rising CLK edge to allow capture to occur.

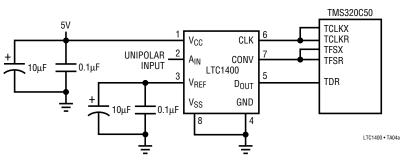

Hardware Interface to TMS320C50's TDM Serial Port (Frame Sync is Generated from TFSX)

Logic Analyzer Waveforms Show 3.2µs Throughput Rate (Input Voltage = 3.046V, Output Code = 1011 1110 0110 = 3046<sub>10</sub>)

Data from LTC1400 Loaded into TMS320C50's TRCV Register

Data Stored in TMS320C50's Memory (in Right Justified Format)

#### TMS320C50 Code for Circuit

| THIS PF     |                |                | ES LTC1400 INTERFACE TO TMS320C50       |           | erial Communicati             |                                                                  |

|-------------|----------------|----------------|-----------------------------------------|-----------|-------------------------------|------------------------------------------------------------------|

| *1          |                | STNC PULSE     | E IS GENERATED FROM TFSX                |           | . TDXR<br>( #040h, IMR        | ; Generate frame sync pulse<br>; Turn on TRNT receiver interrupt |

| *Initializa |                |                | . Defines alshel sumhalis assess        |           | INTM                          | ; Enable interrupt                                               |

| .mmi        |                |                | ; Defines global symbolic names         | CLRC      | SXM                           | ; For Unipolar input, set for right shift                        |

| ; Initia    |                | memory to zer  |                                         | 01.10     |                               | ; with no sign extension                                         |

|             | .ds            | 0F00h          | ; Initialize data to zero               | MAR       | *AR7                          | ; Load the auxiliary register pointer with seven                 |

| DATAO       | .word          | 0              | ; Begin sample data location            | LAR       | AR7, #0F00h                   | ; Load the auxiliary register seven with #0F00h                  |

| DATA1       | .word          | 0              | ;.                                      |           | 7.117, # 01 0011              | ; as the begin address for data storage                          |

| DATA2       | .word          | 0              | ; Location of data                      | WAIT:     | NOP                           | ; Wait for a receive interrupt                                   |

| DATA3       | .word          | 0              | ;.                                      | WAII.     | NOP                           |                                                                  |

| DATA4       | .word          | 0              | ;.                                      |           | NOP                           | •                                                                |

| DATA5       | .word          | 0              | ; End sample data location              | CACI      | . TDXR                        | ,<br>; !! regenerate the frame sync pulse                        |

| ; Set u     | p the ISR v    | vector         |                                         |           |                               | , !! regenerate the name sync pulse                              |

|             | .ps            | 080Ah          | ; Serial ports interrupts               | В         | WAIT                          | ,                                                                |

| rint :      | B              | RECEIVE        | ; 0A;                                   | ;         | end of main pr                | ogram ;                                                          |

| xint :      | В              | TRANSMIT       | ; OC;                                   | *Receive  | r Interrupt Servic            | e Routine*                                                       |

| trnt :      | В              | TREC           | ; 0E;                                   | TREC:     | •                             |                                                                  |

| txnt :      | В              | TTRANX         | ; 10;                                   |           | M TRCV                        | ; Load the data received from LTC1400                            |

|             | o the reset    |                | ,,                                      | SFR       |                               | ; Shift right two times                                          |

|             | A00h           | 100101         |                                         | SFR       |                               | ·                                                                |

| .entry      |                |                |                                         |           | #1FFFh, 0                     | ,<br>: ANDed with #1FFFh                                         |

| START:      | y              |                |                                         | 7110      | <i>"</i> 111111, <b>O</b>     | ; For converting the data to right                               |

| -           |                |                |                                         |           |                               | ; justified format                                               |

|             | C050 Initia    |                |                                         |           |                               | , justilieu loitilat                                             |

|             | ; intm         |                | porarily disable all interrupts         | SVU       | . *+, 0                       | ,<br>; Write to data memory pointed by AR7 and                   |

| LDP         |                |                | data page pointer to zero               | SAUL      | . +, 0                        | ; increase the memory address by one                             |

|             |                | PMST ; Set ı   | up the PMST status and control register | 1 4 0 0   |                               | , increase the memory address by one                             |

| LACC        | C #0           |                |                                         |           | AR7                           | ,<br>Compare to and comple address #0505h                        |

| SAM         | MCWSR          | ; Set s        | software wait state to 0                |           | #0F05h,0                      | ; Compare to end sample address #0F05h                           |

| SAM         | <b>M PDWSR</b> |                |                                         | BONL      | J END_TROV, GEQ               | ; If the end sample address has exceeded jump                    |

|             |                | ,<br>          |                                         |           |                               | to END_TRCV                                                      |

|             | Ire Serial P   |                |                                         |           |                               | ;                                                                |

| SPLK        | (#0038h,       |                | TDM Serial Port                         |           | ( #040h, IMR                  | ; Else Re-enable the TRNT receive interrupt                      |

|             |                |                | 1 = 0 Stand Alone mode                  | RETE      |                               | ; Return to main program and enable interrupt                    |

|             |                |                | =0 Not loop back                        | *After Of | ntained the Data fr           | rom LTC1400, Program Jump to END_TRCV*                           |

|             |                | , -            | 0 16 Bits                               | END_TR    | CV <sup>.</sup>               |                                                                  |

|             |                |                | =1 Burst Mode                           |           | #002h, IMR                    | ; Enable INT2 for program to halt                                |

|             |                | ; MCN          | M=1 CLKX is generated internally        |           | C INTM                        | , Enable nutz for program to hait                                |

|             |                | ; TXM          | I=1 FSX as output pin                   | SUCCES    |                               |                                                                  |

|             |                |                | serial port into reset                  | B         | SUCCESS                       |                                                                  |

|             |                |                | ST=RRST=0)                              |           |                               |                                                                  |

| SPLK        | (#00F8h,       |                | e Serial Port out of reset              | *Fill the | Unused Interrupt <sup>,</sup> | with RETE, to avoid program get "lost"*                          |

|             |                |                | ST=RRST=1)                              | TTRANX:   |                               |                                                                  |

| SPLK        | (#OFFFFh       | , IFR 🛛 ; Člea | r all the pending interrupts            | RETE      |                               |                                                                  |

|             |                |                |                                         | RECEIVE   |                               |                                                                  |

|             |                |                |                                         | RETE      |                               |                                                                  |

|             |                |                |                                         | TRANSM    |                               |                                                                  |

|             |                |                |                                         | RETE      |                               |                                                                  |

|             |                |                |                                         | INT2:     |                               |                                                                  |

|             |                |                |                                         |           |                               |                                                                  |

B halt

; Halts the running CPU

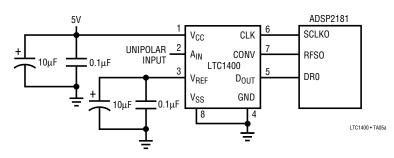

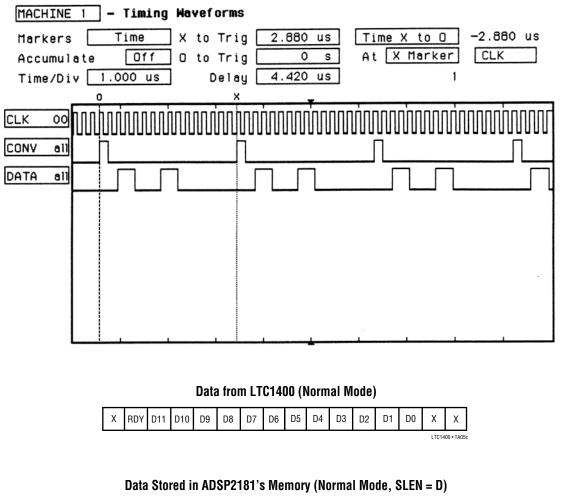

LTC1400 Interface to ADSP2181's SPORTO (Frame Sync is Generated from RFS0)

Logic Analyzer Waveforms Show 2.88µs Throughput Rate (Input Voltage = 2.240V, Output Code = 1000 1100 0000 = 224010)

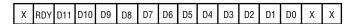

| 0 | 0 | 0 | RDY | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1    | DO        |

|---|---|---|-----|-----|-----|----|----|----|----|----|----|----|----|-------|-----------|

|   |   |   |     |     |     |    |    |    |    |    |    |    |    | LTC14 | 00 • TA05 |

#### ADSP2181 Code for Circuit

|                                                                                                                                                               | MONSTRATES LTC1400 INTERFACE TO ADSP-2181<br>Ync Pulse is generated from RFS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | /*Section 3: configure CLKDIV and RFSDIV, setup interrupts*/<br>/*to configure CLKDIV reg*/                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| jump start;<br>nop; nop; nop;<br>rti; rti; rti; rti;<br>rti; rti; rti; rti;<br>rti; rti; rti; rti;<br>rti; rti; rti; rti;<br>ax0 = rx0;                       | ion*/<br>adspltc; /*define the program module*/<br>/*jump over interrupt vectors*/<br>/*code vectors here upon IRQ2 int*/<br>/*code vectors here upon IRQL0 int*/<br>/*code vectors here upon SPORT0 TX int*/<br>/*code vectors here upon SPORT0 TX int*/<br>/*Section 5*/<br>0; /*begin of SPORT0 receive interrupt*/<br>/* */<br>/* */<br>/* end of SPORT0 receive interrupt*/<br>/* code vectors here upon JIRQE int*/<br>/*code vectors here upon BDMA interrupt*/<br>/*code vectors here upon SPORT1 TX (IRQ1) int*/<br>/*code vectors here upon TIMER int*/<br>/*code vectors here upon POWER DOWN int*/ | /*to Configure RFSDIV<br>ax0= 2;<br>dm(0x3FF5) =ax0;<br>/*to Configure RFSDIV<br>ax0 = 15;<br>dm(0x3FF4) =ax0;<br>/*to setup interrupt*/<br>ifc= 0x0066;<br>icntl= 0;<br>imask= 0x0020; | /*set the serial clock divide modulus reg<br>SCLKDIV*/<br>/*the input clock frequency = 16.67MHz*/<br>/*CLKOUT frequency = 2x = 33MHz*/<br>/*SCLK= 1/2*CLKOUT*1/(SCLKDIV+1)*/<br>/*for SCLKDIV = 2, SCLK = 33/6 = 5.5MHz*/<br>*/<br>/*set the RFSDIV reg = 15*/<br>/*set the RFSDIV reg = 15*/<br>/*if frame sync pulse for every 16 SCLK*/<br>/*if frame sync pulse in every 15 SCLK, ax0=14<br>/*clear any extraneous SPORT interrupts*/<br>/*IRQXB = level sensitivity*/<br>/*disable nesting interrupt*/<br>/*bit 0 = timer int = 0*/<br>/*bit 1 = SPORT1 or IRQ0B int = 0*/<br>/*bit 2 = SPORT1 or IRQ1B int = 0*/ |

| /*Section 2: Configure SPORT0 */<br>start:<br>/*to configure SPORT0 control reg*/<br>/*SPORT0 address = 0X3FF6*/<br>/*RFS is used for frame sync generation*/ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                         | /*bit 3 = BDMA int = 0*/<br>/*bit 4 = IRQEB int = 0*/<br>/*bit 5 = SPORT0 receive int = 1*/<br>/*bit 6 = SPORT0 transmit int = 0*/<br>/*bit 7 = IRQ2B int = 0*/<br>/*enable SPORT0 receive interrupt*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ax0 = 0x6B0D;                                                                                                                                                 | /*RFS0 is internal, TFS is not use*/<br>/*bit 0-3 = Slen*/<br>/*F = 15 = 1111*/<br>/*E = 14 = 1110*/<br>/*D = 13 = 1101*/<br>/*bit 4,5 data type right justified zero filled MSB*/<br>/*bit 6 INVRFS = 0*/<br>/*bit 7 INVTFS = 0*/<br>/*bit 8 IRFS=1 receive internal frame sync*/<br>/*bit 9,10,11 are for TFS (don't care)*/<br>/*bit 12 TFSW=1 receive is Normal mode*/<br>/*bit 13 RTFS=1 receive is framed mode*/<br>/*bit 13 RTFS=1 receive is framed mode*/<br>/*bit 14 ISCLK internal = 1*/<br>/*bit 15 multichannel mode = 0*/<br>/*normal mode, bit12=0*/                                            | /*to configure system (<br>ax0 = dm(0x3FFF);<br>ay0 = 0xFFF0;<br>ar = ax0 AND ay0;<br>ay0 = 0x1000;<br>ar = ar OR ay0;<br>dm(0x3FFF) = ar;                                              | System Control Register and Start Communication*/<br>control reg*/<br>/*read the system control reg*/<br>/*set wait state to zero*/<br>/*bit12 = 1, enable SPORTO*/<br>enerated automatically*/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| dm (0x3FF6) =ax0                                                                                                                                              | /*if alternate mode bit12=1, ax0=0x7F0E*/<br>;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nop;                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nop;<br>waitloop: nop;<br>rts;<br>andmod:                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

.endmod;

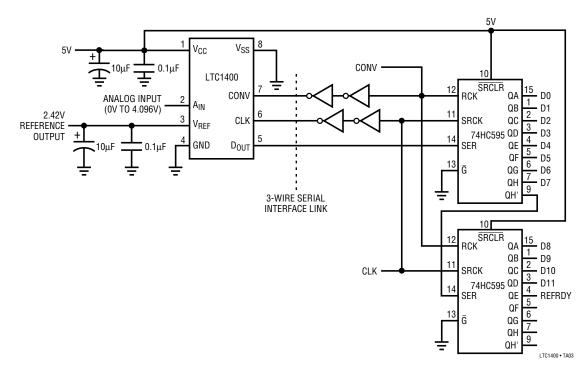

#### Quick Look Circuit for Converting Data to Parallel Format

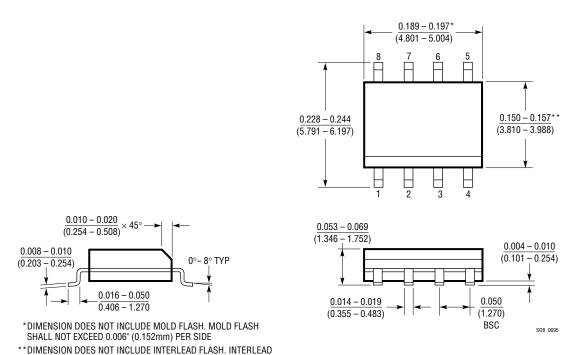

PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

S8 Package 8-Lead Plastic Small Outline (Narrow 0.150) (LTC DWG # 05-08-1610)

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

#### LTC1400 Interface to TMS320C50

LTC1400 Interface to ADSP2181

### **RELATED PARTS**

#### 12-Bit Parallel Output ADCs

| PART NUMBER             | SAMPLE RATE | POWER DISSIPATION | DESCRIPTION                                                  |

|-------------------------|-------------|-------------------|--------------------------------------------------------------|

| LTC1272                 | 250ksps     | 75mW              | Single 5V, 7572 Upgrade                                      |

| LTC1273/LTC1275/LTC1276 | 300ksps     | 75mW              | With Clock and Reference                                     |

| LTC1274/LTC1277         | 100ksps     | 10mW              | Low Power ADCs with 1µA Shutdown                             |

| LTC1278/LTC1279         | 500/600ksps | 75mW              | 70dB at Nyquist, Low Power, Single 5V                        |

| LTC1282                 | 140ksps     | 12mW              | $3V \text{ or } \pm 3V \text{ ADC}$ with Clock and Reference |

| LTC1410                 | 1.25Msps    | 150mW             | 71dB at Nyquist, Differential Input                          |

#### **12-Bit Serial Output ADCs**

| PART NUMBER     | V <sub>CC</sub> | SAMPLE RATE   | POWER DISSIPATION | DESCRIPTION                                            |

|-----------------|-----------------|---------------|-------------------|--------------------------------------------------------|

| LTC1285/LTC1288 | 3V              | 7.5/6.6ksps   | 0.48mW            | 3V, One or Two Input, Micropower, SO-8                 |

| LTC1286/LTC1298 | 5V              | 12.5/11.1ksps | 1.25mV            | One or Two Input, Micropower, SO-8                     |

| LTC1290         | 5/±5V           | 50ksps        | 30mW              | 8 Input, Full-Duplex Serial I/O                        |

| LTC1296         | 5/±5V           | 46.5ksps      | 30mW              | 8 Input, Half-Duplex Serial I/O, Power Shutdown Output |