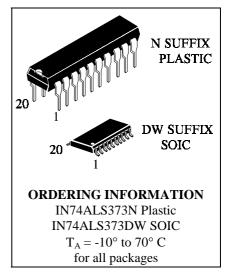

# **IN74ALS373**

# **Octal D-Type 3-State Transparent Latch**

These 8-bit registers feature totem-pole 3-State outputs designed specifically for driving highly-capacitive or relatively low-impedance loads. The high-impedance state and increased high-logic-level drive provide these registers with the capability of being connected directly to and driving the bus lines in a bus-organized system without need for interface or pull-up components. They are particularly attractive for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

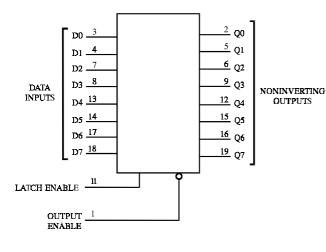

The eight latches of the ALS373 are transparent D-type latches. While the Latch Enable is high the Q outputs will follow the data(D) inputs. When the enable is taken low the output will be latched at the level of the data that was set up.

A buffered output control input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state the outputs neither load nor drive the bus lines significanty.

The output control does not affect the internal operation of the latches. That is, the old data can be retained or new data can be entered even while the outputs are off.

- Switching specifications at 50 pF

- Switching specifications guaranteed over full temperature and V<sub>CC</sub> range

- Functionally and pin for pin compatible with LS TTL counterpart

- Improved AC performance over LS373 at approximately half the power

LOGIC DIAGRAM

TRI-STATE buffer-type outputs drive bus lines directly

### PIN ASSIGNMENT

| OUTPUT<br>ENABLE | 1• | 20       | V CC            |

|------------------|----|----------|-----------------|

| <b>Q</b> 0 E     | 2  | 19       | Q7              |

| D0 [             | 3  | 18       | D7              |

| D1 [             | 4  | 17       | D6              |

| <b>Q</b> 1 [     | 5  | 16       | <b>Q</b> 6      |

| Q2 [             | 6  | 15       | Q5              |

| D2 [             | 7  | 14       | D5              |

| D3 [             | 8  | 13       | D4              |

| Q3 [             | 9  | 12       | Q4              |

| gnd [            | 10 | <u>n</u> | LATCH<br>ENABLE |

#### **FUNCTION TABLE**

| Inputs           |                 |   | Output    |

|------------------|-----------------|---|-----------|

| Output<br>Enable | Latch<br>Enable | D | Q         |

| L                | Н               | Н | Н         |

| L                | Н               | L | L         |

| L                | L               | Х | No Change |

| Н                | Х               | Х | Z         |

X = Don't Care

Z = High Impedance

PIN 20= $V_{CC}$ PIN 10 = GND

## $\mathbf{MAXIMUM}\ \mathbf{RATINGS}^*$

| Symbol           | Parameter                          | Value       | Unit |

|------------------|------------------------------------|-------------|------|

| V <sub>CC</sub>  | Supply Voltage                     | 7.0         | V    |

| V <sub>IN</sub>  | Input Voltage                      | 7.0         | V    |

| V <sub>OUT</sub> | Output Voltage (Referenced to GND) | 5.5         | V    |

| Tstg             | Storage Temperature Range          | -65 to +150 | °C   |

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                 | Min | Max  | Unit |

|-----------------|---------------------------|-----|------|------|

| V <sub>CC</sub> | Supply Voltage            | 4.5 | 5.5  | V    |

| V <sub>IH</sub> | High Level Input Voltage  | 2.0 |      | V    |

| V <sub>IL</sub> | Low Level Input Voltage   |     | 0.8  | V    |

| I <sub>OH</sub> | High Level Output Current |     | -2.6 | mA   |

| I <sub>OL</sub> | Low Level Output Current  |     | 24   | mA   |

| T <sub>A</sub>  | Ambient Temperature Range | -10 | +70  | °C   |

## DC ELECTRICAL CHARACTERISTICS over full operating conditions

|                  |                              |                                 |                             | Guarant | eed Limit |      |

|------------------|------------------------------|---------------------------------|-----------------------------|---------|-----------|------|

| Symbol           | Parameter                    | Test C                          | onditions                   | Min     | Max       | Unit |

| V <sub>IK</sub>  | Input Clamp Voltage          | $V_{CC} = min, I_{IN}$          | = -18 mA                    |         | -1.5      | V    |

| V <sub>OH</sub>  | High Level Output Voltage    | $V_{CC} = \min, I_{OI}$         | $_{\rm H} = -0.4 ~{\rm mA}$ | 2.5     |           | V    |

|                  |                              | $V_{CC} = min, I_{OI}$          | $_{\rm H}$ = -2.6 mA        | 2.4     |           |      |

| V <sub>OL</sub>  | Low Level Output Voltage     | $V_{CC} = min, I_{OI}$          | L = 12  mA                  |         | 0.4       | V    |

|                  |                              | $V_{CC} = min, I_{OI}$          | L = 24  mA                  |         | 0.5       |      |

| I <sub>OZH</sub> | Output Off Current HIGH      | $V_{CC} = max, V$               | $_{OUT} = 2.7 \text{ V}$    |         | 20        | μA   |

| I <sub>OZL</sub> | Output Off Current LOW       | $V_{\rm CC} = \max, V_{\rm CC}$ | $_{OUT} = 0.4 \text{ V}$    |         | -20       | μΑ   |

| I <sub>IH</sub>  | High Level Input Current     | $V_{CC} = max, V$               | $_{IN} = 2.7 \text{ V}$     |         | 20        | μΑ   |

|                  |                              | $V_{CC} = max, V$               | $_{\rm IN} = 7.0 \ {\rm V}$ |         | 0.1       | mA   |

| I <sub>IL</sub>  | Low Level Input Current      | $V_{CC} = max, V$               | $_{IN} = 0.4 V$             |         | -0.1      | mA   |

| I <sub>O</sub>   | Output Short Circuit Current | $V_{\rm CC} = \max, V_{\rm CC}$ | <sub>o</sub> = 2.25 V       | -30     | -112      | mA   |

| I <sub>CC</sub>  | Supply Current               | $V_{CC} = max$                  | Outputs Low                 |         | 16        | mA   |

|                  |                              |                                 | Outputs High                |         | 25        | ]    |

|                  |                              |                                 | 3-State<br>(High Z)         |         | 27        |      |

|                  |                                                | Guarant | <b>Guaranteed Limit</b> |      |

|------------------|------------------------------------------------|---------|-------------------------|------|

| Symbol           | Parameter                                      | Min     | Max                     | Unit |

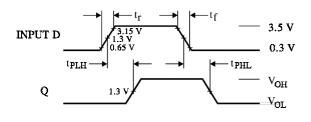

| t <sub>PLH</sub> | Propagation Delay Time, Data to Any Q          |         | 12                      | ns   |

| t <sub>PHL</sub> | Propagation Delay Time, Data to Any Q          |         | 16                      | ns   |

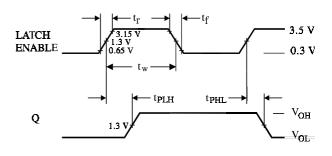

| t <sub>PLH</sub> | Propagation Delay Time, Latch Enable to Any Q  |         | 22                      | ns   |

| t <sub>PHL</sub> | Propagation Delay Time, Latch Enable to Any Q  |         | 23                      | ns   |

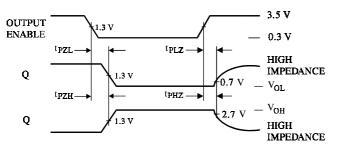

| t <sub>PZH</sub> | Propagation Delay Time, Output Enable to Any Q |         | 20                      | ns   |

| t <sub>PZL</sub> | Propagation Delay Time, Output Enable to Any Q |         | 18                      | ns   |

| t <sub>PHZ</sub> | Propagation Delay Time, Output Enable to Any Q |         | 40                      | ns   |

| t <sub>PLZ</sub> | Propagation Delay Time, Output Enable to Any Q |         | 30                      | ns   |

| t <sub>w</sub>   | Enable Width                                   | 10      |                         | ns   |

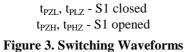

| t <sub>su</sub>  | Setup Time                                     | 10      |                         | ns   |

| t <sub>h</sub>   | Hold Time                                      | 7       |                         | ns   |

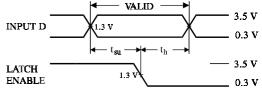

# $\label{eq:constraint} \begin{array}{l} \textbf{AC ELECTRICAL CHARACTERISTICS} \text{ over full operating conditions} \\ \hline (V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ } \text{C}_{L} = 50 \text{ } \text{pF}, \text{ } \text{R}_{L1} = \text{R}_{L2} = 500 \text{ } \Omega \text{, } \text{Input } t_r = t_f = 2.0 \text{ } \text{ns} \text{)} \end{array}$

Figure 1. Switching Waveforms

Figure 2. Switching Waveforms

Figure 4. Switching Waveforms

\* Includes all probe and jig capacitance.

Figure 3. Test Circuit

\* Includes all probe and jig capacitance.

#### Figure 4. Test Circuit