### **DS1312**

# Nonvolatile Controller with Lithium Battery Monitor

#### www.dalsemi.com

### **FEATURES**

- Converts CMOS SRAM into nonvolatile memory

- Unconditionally write-protects SRAM when V<sub>CC</sub> is out of tolerance

- Automatically switches to battery backup supply when V<sub>CC</sub> power failure occurs

- Monitors voltage of a lithium cell and provides advanced warning of impending battery failure

- Signals low-battery condition on active low Battery Warning output signal

- Optional -5% or -10% power-fail detection

- Space-saving 8-pin DIP and SOIC packages

- Optional 16-pin SOIC and 20-pin TSSOP versions reset processor when power failure occurs and hold processor in reset during system power-up

- Industrial temperature range of -40°C to +85°C

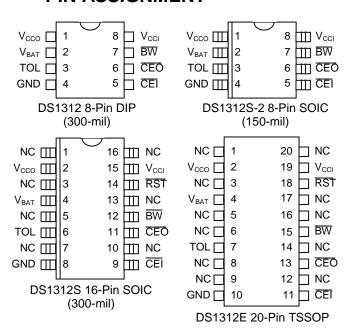

### **PIN ASSIGNMENT**

#### PIN DESCRIPTION

| $V_{CCI}$                | - +5V Power Supply Input           |

|--------------------------|------------------------------------|

| $V_{CCO}$                | - SRAM Power Supply Output         |

| $V_{BAT}$                | - Backup Battery Input             |

| CEI                      | - Chip Enable Input                |

| CEO                      | - Chip Enable Output               |

| TOL                      | - V <sub>CC</sub> Tolerance Select |

| $\overline{\mathrm{BW}}$ | - Battery Warning Output           |

|                          | (Open Drain)                       |

| RST                      | - Reset Output (Open Drain)        |

| GND                      | - Ground                           |

| NC                       | - No Connection                    |

#### DESCRIPTION

The DS1312 Nonvolatile Controller with Battery Monitor is a CMOS circuit which solves the application problem of converting CMOS RAM into nonvolatile memory. Incoming power is monitored for an out-of-tolerance condition. When such a condition is detected, chip enable is inhibited to accomplish write protection and the battery is switched on to supply the RAM with uninterrupted power. Special circuitry uses a low-leakage CMOS process which affords precise voltage detection at extremely low battery consumption.

1 of 11 111999

In addition to battery-backup support, the DS1312 performs the important function of monitoring the remaining capacity of the lithium battery and providing a warning before the battery reaches end-of-life. Because the open-circuit voltage of a lithium backup battery remains relatively constant over the majority of its life, accurate battery monitoring requires loaded-battery voltage measurement. The DS1312 performs such measurement by periodically comparing the voltage of the battery as it supports an internal resistive load with a carefully selected reference voltage. If the battery voltage falls below the reference voltage under such conditions, the battery will soon reach end-of-life. As a result, the Battery Warning pin is activated to signal the need for battery replacement.

### **MEMORY BACKUP**

The DS1312 performs all the circuit functions required to provide battery-backup for an SRAM. First, the device provides a switch to direct power from the battery or the system power supply ( $V_{CCI}$ ). Whenever  $V_{CCI}$  is less than the switch point  $V_{SW}$  and  $V_{CCI}$  is less than the battery voltage  $V_{BAT}$ , the battery is switched in to provide backup power to the SRAM. This switch has voltage drop of less than 0.2 volts.

Second, the DS1312 handles power failure detection and SRAM write-protection.  $V_{CCI}$  is constantly monitored, and when the supply goes out of tolerance, a precision comparator detects power failure and inhibits chip enable output ( $\overline{CEO}$ ) in order to write-protect the SRAM. This is accomplished by holding  $\overline{CEO}$  to within 0.2 volts of  $V_{CCO}$  when  $V_{CCI}$  is out of tolerance. If  $\overline{CEI}$  is (active) low at the time that power failure is detected, the  $\overline{CEO}$  signal is kept low until  $\overline{CEI}$  is brought high again. Once  $\overline{CEI}$  is brought high,  $\overline{CEO}$  is taken high and held high until after  $V_{CCI}$  has returned to its nominal voltage level. If  $\overline{CEI}$  is not brought high by 1.5  $\mu$ s after power failure is detected,  $\overline{CEO}$  is forced high at that time. This specific scheme for delaying write protection for up to 1.5  $\mu$ s guarantees that any memory access in progress when power failure occurs will complete properly. Power failure detection occurs in the range of 4.75 to 4.5 volts (5% tolerance) when the TOL pin is wired to GND or in the range of 4.5 to 4.25 volts (10% tolerance) when TOL is connected to  $V_{CCO}$ .

### **BATTERY VOLTAGE MONITORING**

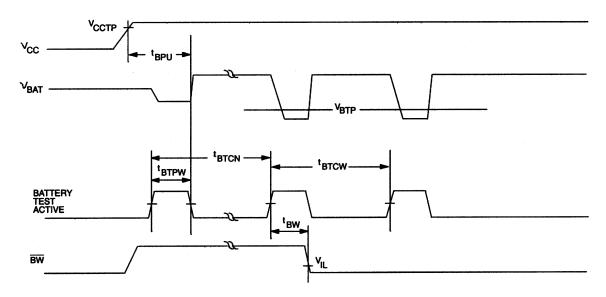

The DS1312 automatically performs periodic battery voltage monitoring at a factory-programmed time interval of 24 hours. Such monitoring begins within  $t_{REC}$  after  $V_{CCI}$  rises above  $V_{CCTP}$ , and is suspended when power failure occurs.

After each 24-hour period ( $t_{BTCN}$ ) has elapsed, the DS1312 connects  $V_{BAT}$  to an internal 1.2 M $\Omega$  test resistor ( $R_{INT}$ ) for one second ( $t_{BTPW}$ ). During this one second, if  $V_{BAT}$  falls below the factory-programmed battery voltage trip point ( $V_{BTP}$ ), the battery warning output  $\overline{BW}$  is asserted. While  $\overline{BW}$  is active battery testing will be performed with period  $t_{BTCW}$  to detect battery removal and replacement. Once asserted,  $\overline{BW}$  remains active until the battery is physically removed and replaced by a fresh cell. The battery is still retested after each  $V_{CC}$  power-up, however, even if  $\overline{BW}$  was active on power-down. If the battery is found to be higher than  $V_{BTP}$  during such testing,  $\overline{BW}$  is deasserted and regular 24-hour testing resumes.  $\overline{BW}$  has an open-drain output driver.

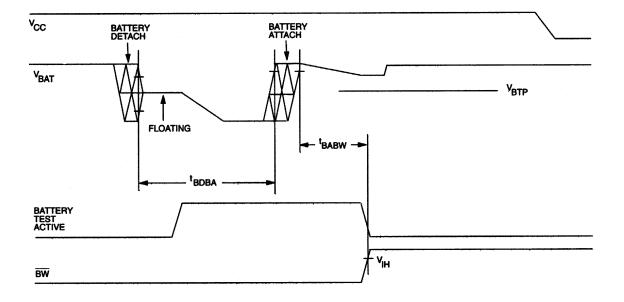

Battery replacement following  $\overline{BW}$  activation is normally done with  $V_{CCI}$  nominal so that SRAM data is not lost. During battery replacement, the minimum time duration between old battery detachment and new battery attachment ( $t_{BDBA}$ ) must be met or  $\overline{BW}$  will not deactivate following attachment of the new battery. Should  $\overline{BW}$  not deactivate for this reason, the new battery can be detached for  $t_{BDBA}$  and then reattached to clear  $\overline{BW}$ .

**NOTE:** The DS1312 cannot constantly monitor an attached battery because such monitoring would drastically reduce the life of the battery. As a result, the DS1312 only tests the battery for one second out of every 24 hours and does not monitor the battery in any way between tests. If a good battery (one that has not been previously flagged with  $\overline{BW}$ ) is removed between battery tests, the DS1312 may not immediately sense the removal and may not activate  $\overline{BW}$  until the next scheduled battery test. If a battery is then reattached to the DS1312, the battery may not be tested until the next scheduled test.

**NOTE:** Battery monitoring is only a useful technique when testing can be done regularly over the entire life of a lithium battery. Because the DS1312 only performs battery monitoring when  $V_{CC}$  is nominal, systems which are powered-down for excessively long periods can completely drain their lithium cells without receiving any advanced warning. To prevent such an occurrence, systems using the DS1312 battery monitoring feature should be powered-up periodically (at least once every few months) in order to perform battery testing. Furthermore, anytime  $\overline{BW}$  is activated on the first battery test after a power-up, data integrity should be checked via checksum or other technique.

### **POWER MONITORING**

DS1312S and DS1312E varieties have an additional reset pin. These varieties detect out-of-tolerance power supply conditions and warn a processor-based system of impending power failure. When  $V_{CCI}$  falls below the trip point level defined by the TOL pin ( $V_{CCTP}$ ), the  $V_{CCI}$  comparator activates the reset signal  $\overline{RST}$ . Reset occurs in the range of 4.75 to 4.5 volts (5% tolerance) when the TOL pin is connected to GND or in the range of 4.5 to 4.25 volts (10% tolerance) when TOL is connected to  $V_{CCO}$ .

RST also serves as a power-on reset during power-up. After  $V_{CCI}$  exceeds  $V_{CCTP}$ , RST will be held active for 200 ms nominal ( $t_{RPU}$ ). This reset period is sufficiently long to prevent system operation during power-on transients and to allow  $t_{REC}$  to expire. RST has an open-drain output driver.

#### FRESHNESS SEAL MODE

When the battery is first attached to the DS1312 without  $V_{CC}$  power applied, the device does not immediately provide battery-backup power on  $V_{CCO}$ . Only after  $V_{CCI}$  exceeds  $V_{CCTP}$  and later falls below both  $V_{SW}$  and  $V_{BAT}$  will the DS1312 leave Freshness Seal Mode and provide battery-backup power. This mode allows a battery to be attached during manufacturing but not used until after the system has been activated for the first time. As a result, no battery energy is drained during storage and shipping.

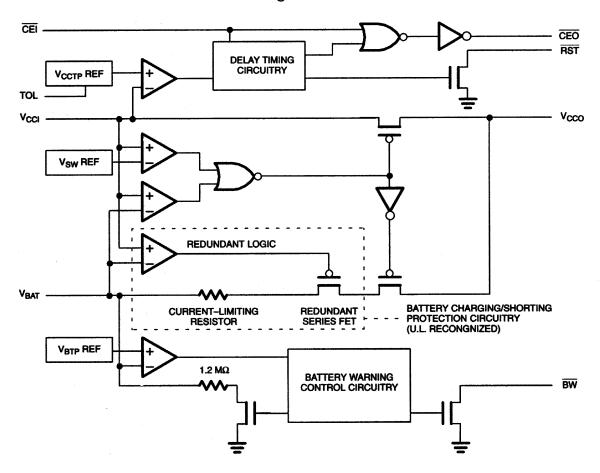

# FUNCTIONAL BLOCK DIAGRAM Figure 1

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground

Operating Temperature

Storage Temperature

-40°C to +85°C

-55°C to +125°C

Soldering Temperature

260°C for 10 seconds

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### RECOMMENDED DC OPERATING CONDITIONS

(-40°C to +85°C)

| PARAMETER               | SYMBOL             | MIN  | TYP | MAX           | UNITS | NOTES |

|-------------------------|--------------------|------|-----|---------------|-------|-------|

| Supply Voltage TOL=GND  | $V_{CCI}$          | 4.75 | 5.0 | 5.5           | V     | 1     |

| Supply Voltage TOL=VCCO | $V_{CCI}$          | 4.5  | 5.0 | 5.5           | V     | 1     |

| Battery Supply Voltage  | $V_{\mathrm{BAT}}$ | 2.0  |     | 6.0           | V     | 1     |

| Logic 1 Input           | $V_{ m IH}$        | 2.0  |     | $V_{CCI}+0.3$ | V     | 1, 12 |

| Logic 0 Input           | $V_{\rm IL}$       | -0.3 |     | +0.8          | V     | 1, 12 |

### DC ELECTRICAL CHARACTERISTICS

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{\text{CCI}} > V_{\text{CCTP}})$

| PARAMETER                                          | SYMBOL           | MIN  | TYP  | MAX  | UNITS | NOTES |

|----------------------------------------------------|------------------|------|------|------|-------|-------|

| Operating Current (TTL inputs)                     | I <sub>CC1</sub> |      | 200  | 400  | μΑ    | 2     |

| Operating Current (CMOS inputs)                    | $I_{CC2}$        |      | 50   | 100  | μA    | 2, 5  |

| RAM Supply Current                                 | $I_{CCO1}$       |      |      | 140  | mA    | 3     |

| $(V_{CCO} \ge V_{CCI} - 0.2V)$                     |                  |      |      |      |       |       |

| RAM Supply Current                                 | $I_{CCO1}$       |      |      | 200  | mA    | 4     |

| $(V_{CCO} \ge V_{CCI} - 0.3V)$                     |                  |      |      |      |       |       |

| V <sub>CC</sub> Trip Point (TOL=GND)               | $V_{CCTP}$       | 4.50 | 4.62 | 4.75 | V     | 1     |

| V <sub>CC</sub> Trip Point (TOL=V <sub>CCO</sub> ) | $V_{CCTP}$       | 4.25 | 4.37 | 4.50 | V     | 1     |

| V <sub>BAT</sub> Trip Point                        | $ m V_{BTP}$     | 2.5  | 2.6  | 2.7  | V     | 1     |

| V <sub>CC</sub> /V <sub>BAT</sub> Switch Point     | $ m V_{SW}$      | 2.6  | 2.7  | 2.8  | V     | 1     |

| Output Current @ 2.4V                              | $I_{OH}$         | -1   |      |      | mA    | 7, 10 |

| Output Current @ 0.4V                              | $I_{OL}$         |      |      | 4    | mA    | 7, 10 |

| Input Leakage                                      | ${ m I}_{ m IL}$ | -1.0 |      | +1.0 | μA    |       |

| Output Leakage                                     | $I_{LO}$         | -1.0 |      | +1.0 | μA    |       |

| Battery Monitoring Test Load                       | $R_{INT}$        | 0.8  | 1.2  | 1.5  | ΜΩ    |       |

### DC ELECTRICAL CHARACTERISTICS (-40°C to +85°C; V<sub>CCI</sub> < V<sub>BAT</sub>; V<sub>CCI</sub> < V<sub>SW</sub>)

| PARAMETER              | SYMBOL       | MIN                   | TYP | MAX | UNITS | NOTES |

|------------------------|--------------|-----------------------|-----|-----|-------|-------|

| Battery Current        | $I_{BAT}$    |                       |     | 100 | nA    | 2     |

| Battery Backup Current | $I_{CCO2}$   |                       |     | 500 | μA    | 6     |

| Supply Voltage         | $V_{CCO}$    | $V_{BAT}$ -0.2        |     |     | V     | 1     |

| CEO Output             | $V_{ m OHL}$ | V <sub>BAT</sub> -0.2 |     |     | V     | 1, 8  |

$\frac{DS1312}{(t_A = 25^{\circ}C)}$ CAPACITANCE

| PARAMETER                                                              | SYMBOL      | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------------------------------------------------|-------------|-----|-----|-----|-------|-------|

| Input Capacitance (CEI, TOL)                                           | $C_{ m IN}$ |     |     | 7   | pF    |       |

| Output Capacitance                                                     | $C_{OUT}$   |     |     | 7   | pF    |       |

| $(\overline{\text{CEO}}, \overline{\text{BW}}, \overline{\text{RST}})$ |             |     |     |     |       |       |

AC ELECTRICAL CHARACTERISTICS  $(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{CCL} > V_{CCTP})$

|                                                     |              |     |     |     | , 001 | 00117 |

|-----------------------------------------------------|--------------|-----|-----|-----|-------|-------|

| PARAMETER                                           | SYMBOL       | MIN | TYP | MAX | UNITS | NOTES |

| CEI to CEO Propagation Delay                        | $t_{ m PD}$  |     | 5   | 10  | ns    |       |

| CE Pulse Width                                      | $t_{CE}$     |     |     | 1.5 | μs    | 11    |

| V <sub>CC</sub> Valid to End of<br>Write Protection | $t_{REC}$    |     | 12  | 125 | ms    | 9     |

| V <sub>CC</sub> Valid to CEI Inactive               | $t_{ m PU}$  |     |     | 2   | ms    |       |

| V <sub>CC</sub> Valid to RST Inactive               | $t_{ m RPU}$ | 150 | 200 | 350 | ms    | 10    |

| V <sub>CC</sub> Valid to BW Valid                   | $t_{ m BPU}$ |     |     | 1   | S     | 10    |

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{\text{CCI}} < V_{\text{CCTP}})$ **AC ELECTRICAL CHARACTERISTICS**

| PARAMETER                                 | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------------|------------------|-----|-----|-----|-------|-------|

| V <sub>CC</sub> Slew Rate                 | $t_{\mathrm{F}}$ | 150 |     |     | μs    |       |

| V <sub>CC</sub> Fail Detect to RST Active | $t_{ m RPD}$     |     | 5   | 15  | μs    | 10    |

| V <sub>CC</sub> Slew Rate                 | $t_{R}$          | 150 |     |     | μs    |       |

AC ELECTRICAL CHARACTERISTICS  $(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{CCI} > V_{CCTP})$

| PARAMETER                        | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|----------------------------------|-------------------|-----|-----|-----|-------|-------|

| Battery Test to BW Active        | $t_{ m BW}$       |     |     | 1   | S     | 10    |

| Battery Test Cycle-Normal        | t <sub>BTCN</sub> |     | 24  |     | hr    |       |

| Battery Test Cycle-Warning       | $t_{ m BTCW}$     |     | 5   |     | S     |       |

| Battery Test Pulse Width         | $t_{ m BTPW}$     |     |     | 1   | S     |       |

| Battery Detach to Battery Attach | $t_{ m BDBA}$     | 7   |     |     | S     |       |

| Battery Attach to BW Inactive    | $t_{ m BABW}$     |     |     | 1   | S     | 10    |

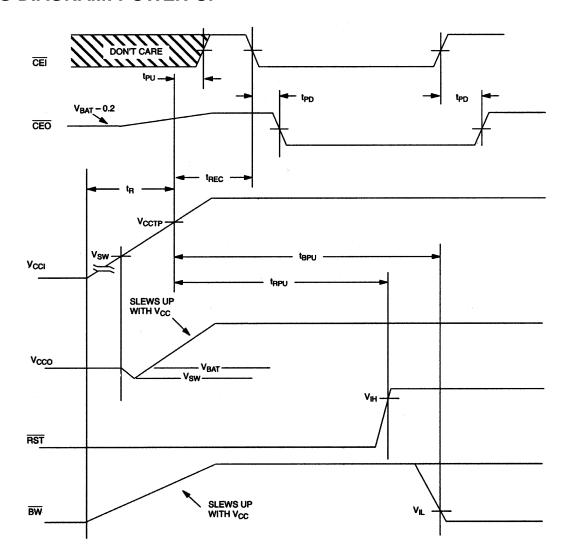

# **TIMING DIAGRAM: POWER-UP**

## NOTE:

If  $V_{BAT} < V_{SW}$ ,  $V_{CCO}$  will begin to slew with  $V_{CCI}$  when  $V_{CCI} = V_{BAT}$ .

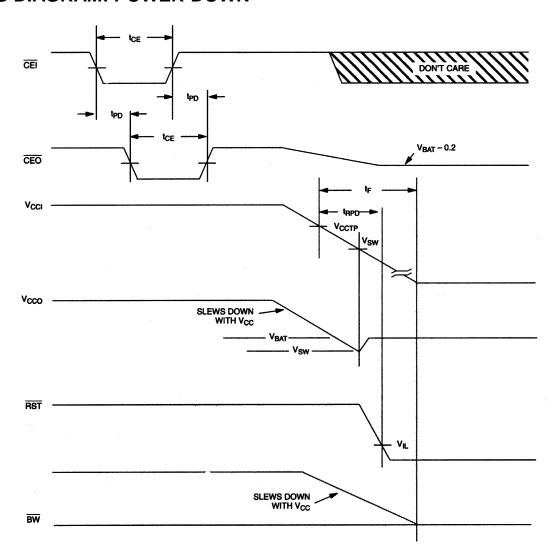

# **TIMING DIAGRAM: POWER-DOWN**

### **NOTE:**

If  $V_{BAT} < V_{SW}$ ,  $V_{CCO}$  will slew down with  $V_{CCI}$  until  $V_{CCI} = V_{BAT}$ .

### **TIMING DIAGRAM: BATTERY WARNING DETECTION**

### **NOTE:**

$t_{BW}$  is measured from the expiration of the internal timer to the activation of the battery warning output  $\overline{BW}$ .

### TIMING DIAGRAM: BATTERY REPLACEMENT

#### NOTES:

- 1. All voltages referenced to ground.

- 2. Measured with outputs open circuited.

- 3.  $I_{CCO1}$  is the maximum average load which the DS1312 can supply to attached memories at  $V_{CCO} > V_{CCI}$  -0.2V.

- 4.  $I_{CCO1}$  is the maximum average load which the DS1312 can supply to attached memories at  $V_{CCO} > V_{CCI}$  -0.3V.

- 5. All inputs within 0.3V of ground or  $V_{CCI}$ .

- 6.  $I_{CCO2}$  is the maximum average load current which the DS1312 can supply to the memories in the battery backup mode.

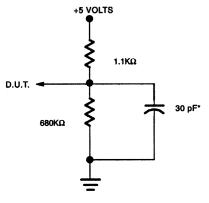

- 7. Measured with a load as shown in Figure 2.

- 8. Chip Enable Output CEO can only sustain leakage current in the battery backup mode.

- 9. CEO will be held high for a time equal to  $t_{REC}$  after  $V_{CCI}$  crosses  $V_{CCTP}$  on power-up.

- 10. BW and RST are open-drain outputs and, as such, cannot source current. External pull-up resistors should be connected to these pins for proper operation. Both BW and RST can sink 10 mA.

- 11. t<sub>CE</sub> maximum must be met to ensure data integrity on power-down.

- 12. In battery-backup mode, inputs must never be below ground or above V<sub>CCO</sub>.

- 13. The DS1312 is recognized by Underwriters Laboratory (U.L.®) under file E99151.

#### DC TEST CONDITIONS

Outputs Open All voltages are referenced to ground

#### AC TEST CONDITIONS

Output Load: See below Input Pulse Levels: 0 - 3.0V

Timing Measurement Reference Levels

Input: 1.5V Output: 1.5V

Input pulse Rise and Fall Times: 5 ns

### **OUTPUT LOAD** Figure 2

\* INCLUDING SCOPE AND JIG CAPACITANCE

#### DATA SHEET REVISION SUMMARY

The following represent the key differences between 12/16/96 and 06/12/97 version of the DS1312 data sheet. Please review this summary carefully.

- 1. Changed V<sub>BAT</sub> max to 6V

- 2. Changed  $t_{BABW}$  from 75 to 1s max

- 3. Changed block diagram to show UL compliance

The following represent the key differences between 06/12/97 and 08/29/97 version of the DS1312 data sheet. Please review this summary carefully.

1. Changed AC test conditions

The following represent the key differences between 08/29/97 and 12/16/97 version of the DS1312 data sheet. Please review this summary carefully.

- 1. Specified Input Capacitance as being only for  $\overline{\text{CEI}}$ , TOL and output capacitance as being only for  $\overline{\text{CEO}}$ ,  $\overline{\text{BW}}$  and  $\overline{\text{RST}}$ . This is not a change but rather a clarification.

- 2. Add note 13 describing UL recognition.