# 10-Bit, 40 MSPS, 3 V, 74 mW A/D Converter

AD9203

#### **FEATURES**

CMOS 10-Bit 40 MSPS Sampling A/D Converter Power Dissipation: 74 mW (3 V Supply, 40 MSPS)

17 mW (3 V Supply, 5 MSPS)

Operation Between 2.7 V and 3.6 V Supply

Differential Nonlinearity: ±0.25 LSB Power-Down (Standby) Mode, 0.65 mW

ENOB:  $9.55 @ f_{IN} = 20 MHz$ Out-of-Range Indicator

Adjustable On-Chip Voltage Reference IF Undersampling up to f<sub>IN</sub> = 130 MHz

Input Range: 1 V to 2 V p-p Differential or Single-Ended

**Adjustable Power Consumption**

**Internal Clamp Circuit**

APPLICATIONS

CCD Imaging

Video

Portable Instrumentation

IF and Baseband Communications

Cable Modems

# Medical Ultrasound PRODUCT DESCRIPTION

The AD9203 is a monolithic low power, single supply, 10-bit, 40 MSPS analog-to-digital converter, with an on-chip voltage reference. The AD9203 uses a multistage differential pipeline architecture and guarantees no missing codes over the full operating temperature range. Its input range may be adjusted between 1 V and 2 V p-p.

The AD9203 has an onboard programmable reference. An external reference can also be chosen to suit the dc accuracy and temperature drift requirements of an application.

An external resistor can be used to reduce power consumption when operating at lower sampling rates. This yields power savings for users who do not require the maximum sample rate. This feature is especially useful at sample rates far below 40 MSPS. Excellent performance is still achieved at reduced power. For example, 9.7 ENOB performance may be realized with only 17 mW of power, using a 5 MHz clock.

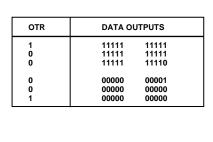

A single clock input is used to control all internal conversion cycles. The digital output data is presented in straight binary or twos complementary output format by using the DFS pin. An out-of-range signal (OTR) indicates an overflow condition that can be used with the most significant bit to determine over or under range.

The AD9203 can operate with a supply range from 2.7 V to 3.6 V, attractive for low power operation in high speed portable applications.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

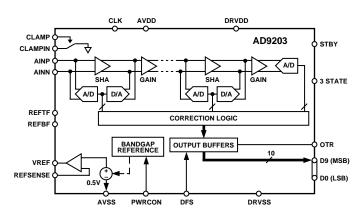

#### **FUNCTIONAL BLOCK DIAGRAM**

The AD9203 is specified over industrial (-40°C to +85°C) temperature ranges and is available in a 28-lead TSSOP package.

#### PRODUCT HIGHLIGHTS

#### Low Power

The AD9203 consumes 74 mW on a 3 V supply operating at 40 MSPS. In standby mode, power is reduced to 0.65 mW.

#### **High Performance**

Maintains better than 9.55 ENOB at 40 MSPS input signal from dc to Nyquist.

#### Very Small Package

The AD9203 is available in a 28-lead TSSOP.

#### **Programmable Power**

The AD9203 power can be further reduced by using an external resistor at lower sample rates.

#### **Built-In Clamp Function**

Allows dc restoration of video signals.

# $\textbf{AD9203-SPECIFICATIONS} \text{ (AVDD} = +3 \text{ V, DRVDD} = +3 \text{ V, F}_S = 40 \text{ MSPS, input span from 0.5 V to 2.5 V, Internal 1 V Reference, PWRCON = AVDD, 50% clock duty cycle, <math>T_{\text{MIN}}$ to $T_{\text{MAX}}$ unless otherwise noted.)

| Parameter                                                                                                                                                                                                          | Symbol                                                             | Min                   | Typ                                            | Max                                       | Units                                    | Conditions                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|------------------------------------------------|-------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESOLUTION                                                                                                                                                                                                         |                                                                    |                       | 10                                             |                                           | Bits                                     |                                                                                                                                                      |

| MAX CONVERSION RATE                                                                                                                                                                                                | Fs                                                                 | 40                    |                                                |                                           | MSPS                                     |                                                                                                                                                      |

| PIPELINE DELAY                                                                                                                                                                                                     | -                                                                  |                       |                                                | 5.5                                       | Clock Cycles                             |                                                                                                                                                      |

| DC ACCURACY Differential Nonlinearity Integral Nonlinearity Offset Error Gain Error                                                                                                                                | DNL<br>INL<br>E <sub>ZS</sub><br>E <sub>FS</sub>                   |                       | ±0.25<br>±0.65<br>±0.6<br>±0.7                 |                                           | LSB<br>LSB<br>% FSR<br>% FSR             |                                                                                                                                                      |

| ANALOG INPUT Input Voltage Range Input Capacitance Aperture Delay Aperture Uncertainty (Jitter) Input Bandwidth (–3 dB) Input Referred Noise                                                                       | AIN<br>C <sub>IN</sub><br>T <sub>AP</sub><br>T <sub>AJ</sub><br>BW | 1                     | 1.4<br>2.0<br>1.2<br>390<br>0.3                | 2                                         | V p-p<br>pF<br>ns<br>ps rms<br>MHz<br>mV | Switched, Single-Ended                                                                                                                               |

| INTERNAL REFERENCE Output Voltage (0.5 V Mode) Output Voltage (1 V Mode) Output Voltage Tolerance (1 V Mode) Load Regulation                                                                                       | VREF<br>VREF                                                       |                       | 0.5<br>1<br>±5<br>0.65                         | ±30<br>1.2                                | V<br>V<br>mV<br>mV                       | REFSENSE = VREF<br>REFSENSE = GND<br>1.0 mA Load                                                                                                     |

| POWER SUPPLY Operating Voltage  Analog Supply Current Digital Supply Current Power Consumption                                                                                                                     | AVDD<br>DRVDD<br>IAVDD<br>IDRVDD                                   | 2.7<br>2.7            | 3.0<br>3.0<br>20.1<br>4.4<br>9.5<br>74         | 3.6<br>3.6<br>22.0<br>6.0<br>14.0<br>84.0 | V<br>V<br>mA<br>mA<br>mA<br>mW           | $f_{\rm IN}$ = 4.8 MHz, Output Bus Load = 10 pF<br>$f_{\rm IN}$ = 20 MHz, Output Bus Load = 20 pF<br>$f_{\rm IN}$ = 4.8 MHz, Output Bus Load = 10 pF |

| Power-Down Power Supply Rejection Ratio                                                                                                                                                                            | P <sub>D</sub><br>PSRR                                             |                       | 88.8<br>0.65<br>0.04                           | 108.0<br>1.2<br>±0.25                     | mW<br>mW<br>% FS                         | $f_{\rm IN} = 4.8$ MHz, Output Bus Load = 10 pF<br>$f_{\rm IN} = 20$ MHz, Output Bus Load = 20 pF                                                    |

| DYNAMIC PERFORMANCE  (AIN = 0.5 dBFS)  Signal-to-Noise and Distortion  f = 4.8 MHz  f = 20 MHz  Effective Bits  f = 4.8 MHz  f = 20 MHz  Signal-to-Noise Ratio  f = 4.8 MHz  f = 20 MHz  Total Harmonic Distortion | SINAD ENOB SNR THD                                                 | 57.2<br>9.2<br>57.5   | 59.7<br>59.3<br>9.6<br>9.55<br>60.0<br>59.5    |                                           | dB<br>dB<br>Bits<br>Bits<br>dB           | Note 1  Note 1                                                                                                                                       |

| f = 4.8 MHz<br>f = 20 MHz<br>Spurious Free Dynamic Range<br>f = 4.8 MHz<br>f = 20 MHz<br>Two-Tone Intermodulation Distortion<br>Differential Phase<br>Differential Gain                                            | SFDR  IMD  DP  DG                                                  | 67.8                  | -76.0<br>-74.0<br>80<br>78<br>68<br>0.2<br>0.3 | -65.0                                     | dB<br>dB<br>dB<br>dB<br>Degree<br>%      | Note 1  Note 1  f = 44.49 MHz and 45.52 MHz  NTSC 40 IRE Ramp                                                                                        |

| DIGITAL INPUTS High Input Voltage Low Input Voltage Clock Pulsewidth High Clock Pulsewidth Low Clock Period <sup>2</sup>                                                                                           | $V_{IH}$ $V_{IL}$                                                  | 2.0<br>11.25<br>11.25 | 25                                             | 0.4                                       | V<br>V<br>ns<br>ns<br>ns                 |                                                                                                                                                      |

-2- REV. 0

| Parameter                                               | Symbol Min       |       | Тур | Max       | Units | Conditions            |

|---------------------------------------------------------|------------------|-------|-----|-----------|-------|-----------------------|

| DIGITAL OUTPUTS                                         |                  |       |     |           |       |                       |

| High-Z Leakage                                          | $I_{OZ}$         |       |     | $\pm 5.0$ | μΑ    | Output = 0 to DRVDD   |

| Data Valid Delay                                        | t <sub>OD</sub>  |       | 5   |           | ns    | $C_L = 20 \text{ pF}$ |

| Data Enable Delay                                       | t <sub>DEN</sub> |       | 6   |           | ns    | $C_L = 20 \text{ pF}$ |

| Data High-Z Delay                                       | t <sub>DHZ</sub> |       | 6   |           | ns    | $C_L = 20 \text{ pF}$ |

| LOGIC OUTPUT (with DRVDD = 3 V)                         |                  |       |     |           |       |                       |

| High Level Output Voltage ( $I_{OH} = 50 \mu A$ )       | $V_{OH}$         | +2.95 |     |           | V     |                       |

| High Level Output Voltage ( $I_{OH} = 0.5 \text{ mA}$ ) | $V_{OH}$         | +2.80 |     |           | V     |                       |

| Low Level Output Voltage ( $I_{OL} = 1.6 \text{ mA}$ )  | $V_{OL}$         |       |     | +0.3      | V     |                       |

| Low Level Output Voltage ( $I_{OL} = 50 \mu A$ )        | V <sub>OL</sub>  |       |     | +0.05     | V     |                       |

Specifications subject to change without notice.

$(C_{LOAD} = 20pF)$

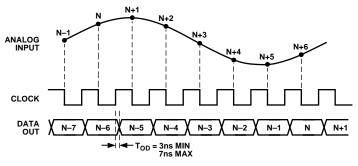

Figure 1. Timing Diagram

REV. 0 -3-

NOTES

<sup>1</sup>Differential Input (2 V p-p).

<sup>2</sup>The AD9203 will convert at clock rates as low as 20 kHz.

#### ABSOLUTE MAXIMUM RATINGS\*

|                      | With    |            |             |       |  |  |  |  |

|----------------------|---------|------------|-------------|-------|--|--|--|--|

|                      | Respect |            |             |       |  |  |  |  |

| Parameter            | to      | Min        | Max         | Units |  |  |  |  |

| AVDD                 | AVSS    | -0.3       | +3.9        | V     |  |  |  |  |

| DRVDD                | DRVSS   | -0.3       | +3.9        | V     |  |  |  |  |

| AVSS                 | DRVSS   | -0.3       | +0.3        | V     |  |  |  |  |

| AVDD                 | DRVDD   | -3.9       | +3.9        | V     |  |  |  |  |

| REFCOM               | AVSS    | -0.3       | +0.3        | V     |  |  |  |  |

| CLK                  | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| Digital Outputs      | DRVSS   | -0.3       | DRVDD + 0.3 | V     |  |  |  |  |

| AINP                 | AINN    | AVSS – 0.3 | AVDD + 0.3  | V     |  |  |  |  |

| VREF                 | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| REFSENSE             | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| REFTF, REFBF         | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| STBY                 | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| CLAMP                | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| CLAMPIN              | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| PWRCON               | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| DFS                  | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| 3-STATE              | AVSS    | -0.3       | AVDD + 0.3  | V     |  |  |  |  |

| Junction Temperature |         |            | +150        | °C    |  |  |  |  |

| Storage Temperature  |         | -65        | +150        | °C    |  |  |  |  |

| Lead Temperature     |         |            |             |       |  |  |  |  |

| (10 sec)             |         |            | +300        | °C    |  |  |  |  |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

28-Lead TSSOP

$\theta_{JA} = 97.9^{\circ} \text{C/W}$

$\theta_{\rm JC} = 14.0^{\circ} \rm C/W$

#### **ORDERING GUIDE**

| Model     | Temperature<br>Range | Package<br>Description | Package<br>Option |

|-----------|----------------------|------------------------|-------------------|

| AD9203ARU | −40°C to +85°C       | 28-Lead Thin Shrink    | RU-28             |

|           |                      | Small Outline          |                   |

| AD9203-EB |                      | Evaluation Board       |                   |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9203 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-4- REV. 0

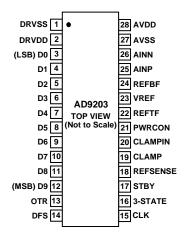

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin | Name     | Description                                                       |

|-----|----------|-------------------------------------------------------------------|

| 1   | DRVSS    | Digital Ground                                                    |

| 2   | DRVDD    | Digital Supply                                                    |

| 3   | D0       | Bit 0, Least Significant Bit                                      |

| 4   | D1       | Bit 1                                                             |

| 5   | D2       | Bit 2                                                             |

| 6   | D3       | Bit 3                                                             |

| 7   | D4       | Bit 4                                                             |

| 8   | D5       | Bit 5                                                             |

| 9   | D6       | Bit 6                                                             |

| 10  | D7       | Bit 7                                                             |

| 11  | D8       | Bit 8                                                             |

| 12  | D9       | Bit 9, Most Significant Bit                                       |

| 13  | OTR      | Out-of-Range Indicator                                            |

| 14  | DFS      | Data Format Select. (HI: Twos Complement. LO: Straight Binary)    |

| 15  | CLK      | Clock Input                                                       |

| 16  | 3-STATE  | HI: High Impedance State Output. LO: Active Digital Output Drives |

| 17  | STBY     | HI: Power-Down Mode. LO: Normal Operation                         |

| 18  | REFSENSE | Reference Select                                                  |

| 19  | CLAMP    | HI: Enable Clamp. LO: Open Clamp                                  |

| 20  | CLAMPIN  | Clamp Signal Input                                                |

| 21  | PWRCON   | Power Control Input                                               |

| 22  | REFTF    | Top Reference Decoupling                                          |

| 23  | VREF     | Reference In/Out                                                  |

| 24  | REFBF    | Bottom Reference Decoupling                                       |

| 25  | AINP     | Noninverting Analog Input                                         |

| 26  | AINN     | Inverting Analog Input                                            |

| 27  | AVSS     | Analog Ground                                                     |

| 28  | AVDD     | Analog Supply                                                     |

REV. 0 -5-

# DEFINITIONS OF SPECIFICATIONS INTEGRAL NONLINEARITY ERROR (INL)

Linearity error refers to the deviation of each individual code from a line drawn from "negative full scale" through "positive full scale." The point used as "negative full scale" occurs 1/2 LSB before the first code transition. "Positive full scale" is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

# DIFFERENTIAL NONLINEARITY ERROR (DNL, NO MISSING CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 10-bit resolution indicates that all 1024 codes respectively, must be present over all operating ranges.

## SIGNAL-TO-NOISE AND DISTORTION (S/N+D, SINAD) RATIO

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

#### **EFFECTIVE NUMBER OF BITS (ENOB)**

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula,

$$N = (SINAD - 1.76)/6.02$$

it is possible to get a measure of performance expressed as N, the effective number of bits.

Thus, effective number of bits for a device for sine wave inputs at a given input frequency can be calculated directly from its measured SINAD.

#### TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

#### SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

#### **SPURIOUS FREE DYNAMIC RANGE (SFDR)**

The difference in dB between the rms amplitude of the input signal and the peak spurious signal.

#### **OFFSET ERROR**

First transition should occur for an analog value 1/2 LSB above –full scale. Offset error is defined as the deviation of the actual transition from that point.

#### **GAIN ERROR**

The first code transition should occur at an analog value 1/2 LSB above –full scale. The last transition should occur for an analog value 1 1/2 LSB below the +full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

#### POWER SUPPLY REJECTION

The specification shows the maximum change in full scale from the value with the supply at the minimum limit to the value with the supply at its maximum limit.

#### APERTURE JITTER

Aperture jitter is the variation in aperture delay for successive samples and is manifested as noise on the input to the A/D.

#### APERTURE DELAY

Aperture delay is a measure of the Sample-and-Hold Amplifier (SHA) performance and is measured from the rising edge of the clock input to when the input signal is held for conversion.

#### **PIPELINE DELAY (LATENCY)**

The number of clock cycles between conversion initiation and the associated output data being made available. New output data is provided on every rising edge.

-6- REV. 0

### **Typical Performance Characteristics—AD9203**

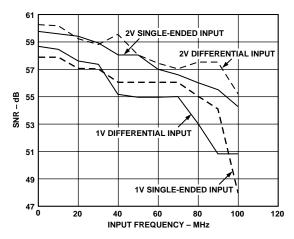

(AVDD = +3 V, DRVDD = +3 V, F<sub>S</sub> = 40 MSPS, 1 V Internal Reference, PWRCON = AVDD, 50% Duty Cycle, unless otherwise noted)

Figure 2. SNR vs. Input Frequency and Configuration

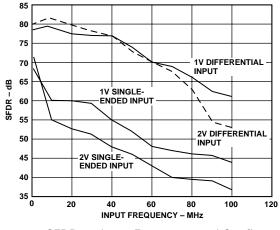

Figure 5. SFDR vs. Input Frequency and Configuration

Figure 3. SINAD vs. Input Frequency and Configuration

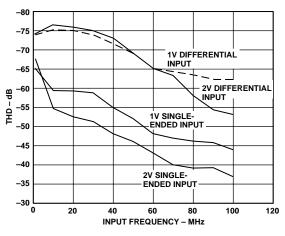

Figure 6. THD vs. Input Frequency and Configuration

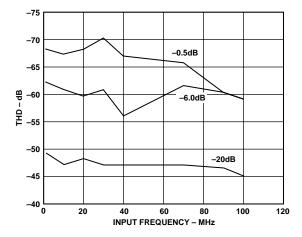

Figure 4. THD vs. Input Frequency and Amplitude (Differential Input VREF = 0.5 V)

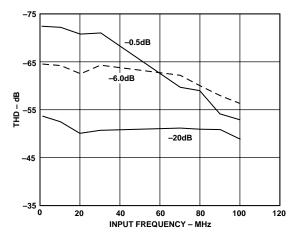

Figure 7. THD vs. Input Frequency and Amplitude (Differential Input VREF = 1 V)

REV. 0 -7-

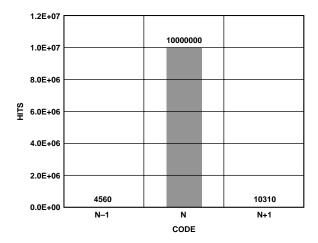

Figure 8. Grounded Input Histogram

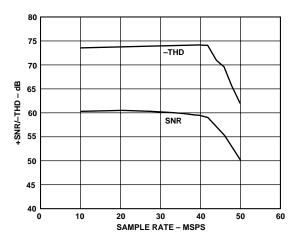

Figure 9. SNR and THD vs. Sample Rate ( $f_{IN} = 20 \text{ MHz}$ )

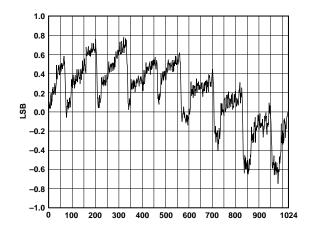

Figure 10. Typical INL Performance

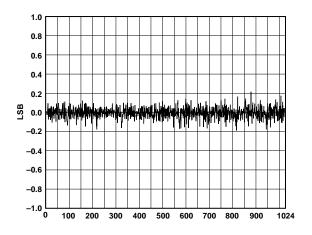

Figure 11. Typical DNL Performance

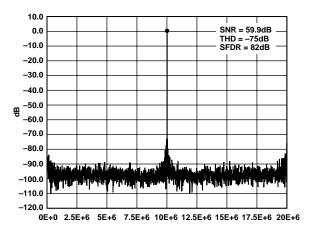

Figure 12. Single Tone Frequency Domain Performance (Input Frequency = 10 MHz, Sample Rate = 40 MSPS 2 V Differential Input, 8192 Point FFT)

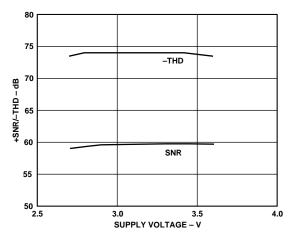

Figure 13. THD vs. Power Supply ( $f_{IN} = 20$  MHz, Sample Rate = 40 MSPS)

-8- REV. 0

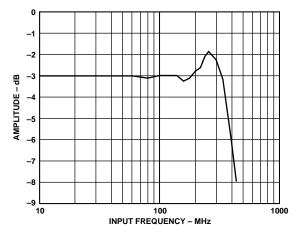

Figure 14. Full Power Bandwidth

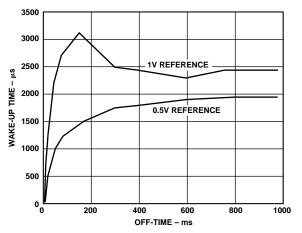

Figure 15. Wake-Up Time vs. Off Time (VREF Decoupling =  $10 \mu$ F)

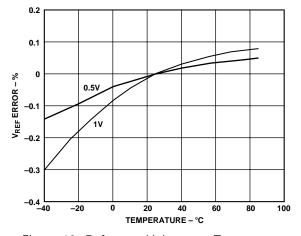

Figure 16. Reference Voltage vs. Temperature

#### APPLYING THE AD9203 THEORY OF OPERATION

The AD9203 implements a pipelined multistage architecture to achieve high sample rates while consuming low power. The AD9203 distributes the conversion over several smaller A/D subblocks, refining the conversion with progressively higher accuracy as it passes the results from stage to stage. As a consequence of the distributed conversion, the AD9203 requires a small fraction of the 1023 comparators used in a traditional 10-bit flash-type A/D. A sample-and-hold function within each of the stages permits the first stage to operate on a new input sample while the remaining stages operate on preceding samples.

Each stage of the pipeline, excluding the last, consists of a low resolution flash A/D connected to a switched capacitor DAC and interstage residue amplifier (MDAC). The residue amplifier magnifies the difference between the reconstructed DAC output and the flash input for the next stage in the pipeline. One bit of redundancy is used in each one of the stages to facilitate digital correction of flash errors. The last stage simply consists of a flash A/D.

The input of the AD9203 incorporates a novel structure that merges the input sample and hold amplifier (SHA) and the first pipeline residue amplifier into a single, compact switched capacitor circuit. This structure achieves considerable noise and power savings over a conventional implementation that uses separate amplifiers by eliminating one amplifier in the pipeline. By matching the sampling network of the input SHA with the first stage flash A/D, the AD9203 can sample inputs well beyond the Nyquist frequency with no degradation in performance.

Sampling occurs on the falling edge of the clock.

#### **OPERATIONAL MODES**

The AD9203 may be connected in several input configurations (see Table I).

The AD9203 may be driven differentially from a source that keeps the signal peaks within the power supply rails.

Alternatively, the input may be driven into AINP or AINN from a single-ended source. The input span will be 2× the programmed reference voltage. One input will accept the signal, while the opposite input will be set to midscale by connecting it to the internal or an external reference. For example, a 2 V p-p signal may be applied to AINP while a 1 V reference is applied to AINN. The AD9203 will then accept a signal varying between 2 V and 0 V. See Figures 17, 18 and 19 for more details.

The AD9203's single-ended (ac-coupled) input may also be clamped to ground by the AD9203's internal clamp switch. This is accomplished by connecting the CLAMP pin to AINN or AINP.

Digital output formats may be configured in binary and twos complement. This is determined by the potential on the DFS pin. If the pin is set to Logic "0," the data will be in straight binary format. If the pin is asserted to Logic "1," the data will be in twos complement format.

Power consumption may be reduced by placing a resistor between PWRCON and AVSS. This may be done to conserve power when not encoding high speed analog input frequencies or sampling at the maximum conversion rate. See Power Control section.

REV. 0 –9–

Table I. Modes

| Name             | Figure Number                             | Advantages                                            |

|------------------|-------------------------------------------|-------------------------------------------------------|

| 1 V Differential | Figure 26 with VREF Connected to REFSENSE | Differential Modes Yield the Best Dynamic Performance |

| 2 V Differential | Figure 26 with REFSENSE Connected to AGND | Differential Modes Yield the Best Dynamic Performance |

| 1 V Single-Ended | Figure 18                                 | Video and Applications Requiring Clamping Require     |

|                  |                                           | Single-Ended Inputs                                   |

| 2 V Single-Ended | Figure 17                                 | Video and Applications Requiring Clamping Require     |

|                  |                                           | Single-Ended Inputs                                   |

-10-

#### INPUT AND REFERENCE OVERVIEW

Like the voltage applied to the top of the resistor ladder in a flash A/D converter, the value VREF defines the maximum input voltage to the A/D core. The minimum input voltage to the A/D core is automatically defined to be -VREF.

The addition of a differential input structure gives the user an additional level of flexibility that is not possible with traditional flash converters. The input stage allows the user to easily configure the inputs for either single-ended operation or differential operation. The A/D's input structure allows the dc offset of the input signal to be varied independently of the input span of the converter. Specifically, the input to the A/D core is the difference of the voltages applied at the AINP and AINN input pins. Therefore, the equation,

$$V_{CORE} = AINP - AINN \tag{1}$$

defines the output of the differential input stage and provides the input to the A/D core.

The voltage,  $V_{CORE}$ , must satisfy the condition,

$$-VREF \le V_{CORE} \le VREF \tag{2}$$

where VREF is the voltage at the VREF pin.

The actual span (AINP – AINN) of the ADC is  $\pm$ VREF.

While an infinite combination of AINP and AINN inputs exist that satisfy Equation 2, an additional limitation is placed on the inputs by the power supply voltages of the AD9203. The power supplies bound the valid operating range for AINP and AINN. The condition.

$$AVSS - 0.3 \ V < AINP < AVDD + 0.3 \ V$$

$AVSS - 0.3 \ V < AINN < AVDD + 0.3 \ V$  (3)

where AVSS is nominally 0 V and AVDD is nominally +3 V, defines this requirement. The range of valid inputs for AINP and AINN is any combination that satisfies both Equations 2 and 3.

#### INTERNAL REFERENCE CONNECTION

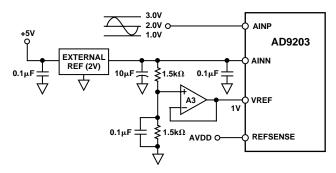

A comparator within the AD9203 will detect the potential of the VREF pin. If REFSENSE is grounded, the reference amplifier switch will connect to the resistor divider (see Figure 17). That will make VREF equal to 1 V. If resistors are placed between VREF, REFSENSE and ground, the switch will be connected to the REFSENSE position and the reference amplitude will depend on the external programming resistors (Figure 19). If REFSENSE is tied to VREF, the switch will also connect to REFSENSE and the reference voltage will be 0.5 V (Figure 18). REFTF and REFBF will drive the ADC conversion core and establish its maximum and minimum span. The range of the

ADC will equal the twice voltage at the reference pin for both an internal or external reference.

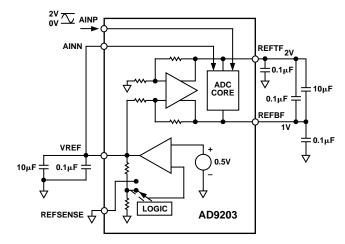

Figure 17 illustrates the input configured with a 1 V reference. This will set the single-ended input of the AD9203 in the 2 V span ( $2 \times VREF$ ). This example shows the AINN input is tied to the 1 V VREF. This will configure the AD9203 to accept a 2 V input centered around 1 V.

Figure 17. Internal Reference Set for a 2 V Span

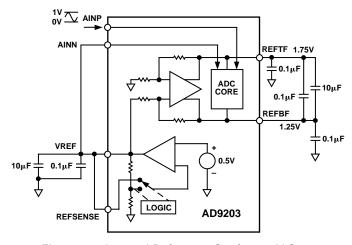

Figure 18 illustrates the input configured with a 0.5 V reference. This will set the single ended input of the ADC in a 1 V span  $(2 \times VREF)$ . The AINN input is tied to the 0.5 VREF. This will configure the AD9203 to accept a 1 V input centered around 0.5 V.

Figure 18. Internal Reference Set for a 1 V Span

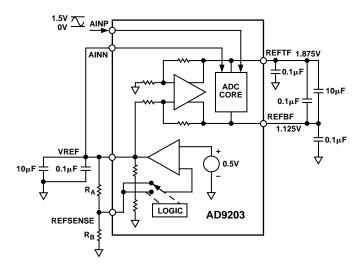

Figure 19 shows the reference programmed by external resistors for 0.75 V. This will set the ADC to receive a 1.5 V span centered about 0.75 V. The reference is programmed according to the algorithm

$$VREF = 0.5 V \times [1 + (RA/RB)]$$

Figure 19. Programmable Reference Configuration

#### **EXTERNAL REFERENCE OPERATION**

Figure 20 illustrates the use of an external reference. An external reference may be necessary for several reasons. Tighter reference tolerance will enhance the accuracy of the ADC and will allow lower temperature drift performance. When several ADC's track one another, a single reference (internal or external) will be necessary. The AD9203 will draw less power when an external reference is used.

When the REFSENSE pin is tied to AVDD, the internal reference will be disabled, allowing the use of an external reference.

The AD9203 contains an internal reference buffer. It will load the external reference with an equivalent 10 k $\Omega$  load. The internal buffer will generate positive and negative full-scale references for the ADC core.

In Figure 20, an external reference is used to set the midscale set point for single-ended use. At the same time, it sets the input voltage span through a resistor divider. If the ADC is being driven differentially through a transformer, the external reference can set the center tap (common-mode voltage).

Figure 20. External Reference Configuration

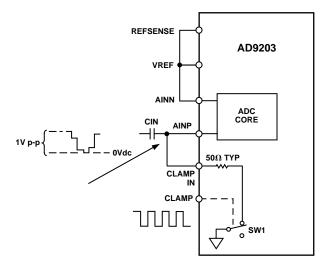

#### **CLAMP OPERATION**

The AD9203 contains an internal clamp. It may be used when operating the input in a single-ended mode. The AD9203's clamp is very useful for clamping NTSC and PAL video signals to ground. The clamp cannot be used in the differential input mode.

Figure 21. Clamp Configuration (VREF = 0.5 V)

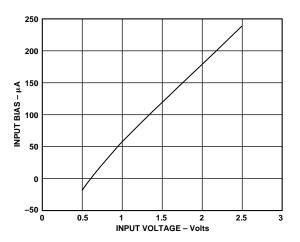

Figure 21 shows the internal clamp circuitry and the external control signals needed for clamp operation. To enable the clamp, apply a logic high "1" to the CLAMP pin. This will close the internal switch SW1. SW1 is opened by asserting the CLAMP pin low "0." The capacitor holds the voltage across C<sub>IN</sub> constant until the next interval. The charge on the capacitor will leak off as a function of input bias current (see Figure 22).

Figure 22. Input Bias Current vs. Input Voltage  $(F_S = 40 \text{ MSPS})$

REV. 0 -11-

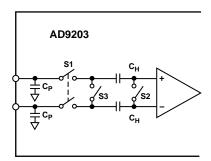

#### DRIVING THE ANALOG INPUT

Figure 23 illustrates the equivalent analog input of the AD9203, (a switched capacitor input). Bringing CLK to a logic high, opens S3 and closes S1 and S2. The input source connected to AIN and must charge Capacitor C<sub>H</sub> during this time. Bringing CLK to a logic low opens S2, and then S1 opens followed by closing S3. This puts the input in the hold mode.

Figure 23. Input Architecture

The structure of the input SHA places certain requirements on the input drive source. The combination of the pin capacitance, C<sub>P</sub>, and the hold capacitance, C<sub>H</sub>, is typically less than 5 pF. The input source must be able to charge or discharge this capacitance to 10-bit accuracy in one half of a clock cycle. When the SHA goes into track mode, the input source must charge or discharge capacitor C<sub>H</sub> from the voltage already stored on C<sub>H</sub> to the new voltage. In the worst case, a full-scale voltage step on the input source must provide the charging current through the  $R_{ON}$  (100  $\Omega$ ) of Switch 1 and quickly (within 1/2 CLK period) settle. This situation corresponds to driving a low input impedance. Adding series resistance between the output of the signal source and the AIN pin reduces the drive requirements placed on the signal source. Figure 24 shows this configuration. The bandwidth of the particular application limits the size of this resistor. To maintain the performance outlined in the data sheet specifications, the resistor should be limited to 50  $\Omega$  or less. The series input resistor can be used to isolate the driver from the AD9203's switched capacitor input. The external capacitor may be selected to limit the bandwidth into the AD9203. Two input RC networks should be used to balance differential input drive schemes (Figure 24).

The input span of the AD9203 is a function of the reference voltage. For more information regarding the input range, see the Internal and External Reference sections of the data sheet.

Figure 24. Simple AD9203 Drive Configuration

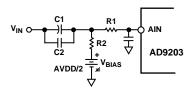

In many cases, particularly in single-supply operation, ac coupling offers a convenient way of biasing the analog input signal to the proper signal range. Figure 25 shows a typical configuration for ac-coupling the analog input signal to the AD9203. Maintaining the specifications outlined in the data sheet requires careful selection of the component values. The most important is the  $f_{3\,dB}$  high-pass corner frequency. It is a function of R2 and the parallel combination of C1 and C2.

Figure 25. AC-Coupled Input

The  $f_{-3 dB}$  point can be approximated by the equation:

$$f_{-3 dB} = 1/(2 \pi \times [R2] C_{EO})$$

where  $C_{EQ}$  is the parallel combination of C1 and C2. Note that C1 is typically a large electrolytic or tantalum capacitor that becomes inductive at high frequencies. Add a small ceramic or polystyrene capacitor (on the order of 0.01  $\mu$ F) that is negligibly inductive at higher frequencies while maintaining a low impedance over a wide frequency range.

There are additional considerations when choosing the resistor values for an ac-coupled input. The ac-coupling capacitors integrate the switching transients present at the input of the AD9203 and cause a net dc bias current, IB, to flow into the input. The magnitude of the bias current increases as the signal changes and as the clock frequency increases. This bias current will result in an offset error of  $(R1+R2) \times IB$ . If it is necessary to compensate for this error, consider modifying VBIAS to account for the resultant offset. In systems that must use dc coupling, use an op amp to level-shift ground-referenced signals to comply with the input requirements of the AD9203.

#### **OP AMP SELECTION GUIDE**

Op amp selection for the AD9203 is highly application dependent. In general, the performance requirements of any given application can be characterized by either time domain or frequency domain constraints. In either case, one should carefully select an op amp that preserves the performance of the A/D. This task becomes challenging when one considers the AD9203's high performance capabilities coupled with other system level requirements such as power consumption and cost.

The ability to select the optimal op amp may be further complicated by either limited power supply availability and/or limited acceptable supplies for a desired op amp. Newer, high performance op amps typically have input and output range limitations in accordance with their lower supply voltages. As a result, some op amps will be more appropriate in systems where accoupling is allowed. When dc-coupling is required, op amps' headroom constraints (such as rail-to-rail op amps) or ones where larger supplies can be used, should be considered.

The following section describes some op amps currently available from Analog Devices. Please contact the factory or local sales office for updates on Analog Devices latest amplifier product offerings.

**AD8051:**  $f_{-3 dB} = 110 \text{ MHz}.$

Low cost. Best used for driving single-ended ac-coupled configuration. Operates on a 3 V power rail.

AD8052: Dual Version of above amp.

**AD8138** is a higher performance version of AD8131. Its gain is programmable and provides 14-bit performance.

-12- REV. 0

#### DIFFERENTIAL MODE OF OPERATION

Since not all applications have a signal preconditioned for differential operation, there is often a need to perform a single-ended-to-differential conversion. In systems that do not need a dc input, an RF transformer with a center tap is a method to generate differential inputs beyond 20 MHz for the AD9203. This provides all the benefits of operating the A/D in the differential mode without contributing additional noise or distortion. An RF transformer also has the added benefit of providing electrical isolation between the signal source and the A/D.

An improvement in THD and SFDR performance can be realized by operating the AD9203 in differential mode. The performance enhancement between the differential and single-ended mode is most considerable as the input frequency approaches and goes beyond the Nyquist frequency (i.e.,  $f_{\rm IN} > F_{\rm S}/2$ ).

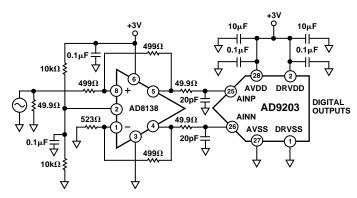

Figure 26. AD8138 Driving an AD9203, a 10-Bit, 40 MSPS A/D Converter

The AD8138 provides a convenient method of converting a single-ended signal to a differential signal. This is an ideal method for generating a direct coupled signal to the AD9203. The AD8138 will accept a signal and shift it to an externally provided common-mode level. The AD8138 configuration is shown in Figure 26.

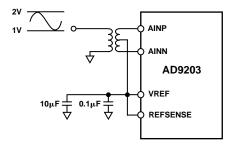

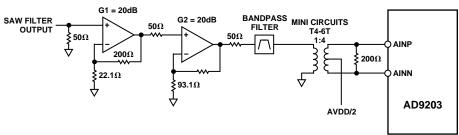

Figure 27 shows the schematic of a suggested transformer circuit. The circuit uses a Minicircuits RF transformer, model number T4–1T, which has an impedance ratio of four (turns ratio of 2).

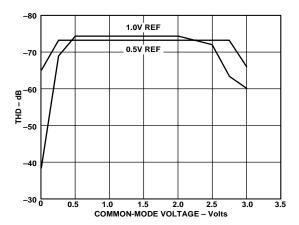

The center tap of the transformer provides a convenient means of level-shifting the input signal to a desired common-mode voltage. Figure 28 illustrates the performance of the AD9203 over a wide range of common-mode levels.

Figure 27. Transformer Coupled Input

Transformers with other turns ratios may also be selected to optimize the performance of a given application. For example, selecting a transformer with a higher impedance ratio (e.g., Minicircuits T16–6T with a impedance ratio of 16) effectively "steps up" the signal amplitude, thus further reducing the driving requirements of the signal source.

The AD9203 can be easily configured for either a 1 V p-p input span or 2 V p-p input span by setting the internal reference. Other input spans can be realized with two external gain setting resistors as shown in Figure 19 of this data sheet. Figures 32 and 33 demonstrate the SNR and SFDR performance over a wide range of amplitudes required by most communication applications.

Figure 28. THD vs. Common-Mode Voltage vs. THD (AIN = 2 V Differential) ( $f_{\text{IN}} = 5 \text{ MHz}$ ,  $f_{\text{S}} = 40 \text{ MSPS}$ )

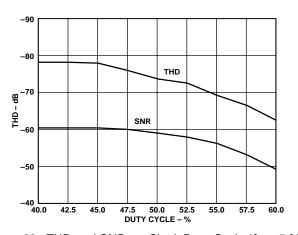

Figure 29. THD and SNR vs. Clock Duty Cycle ( $f_{\rm IN}$  = 5 MHz Differential, Clock = 40 MSPS)

REV. 0 -13-

Table II. Power Programming Resistance

| Clock<br>MHz | f <sub>IN</sub><br>MHz | THD<br>dB       | SNR<br>dB | SINAD<br>dB | SFDR<br>dB | IAVDD<br>mA | IDRVDD<br>mA | Total Power<br>Into 5 pF Load<br>mW | Power Control<br>Resistor<br>kΩ |

|--------------|------------------------|-----------------|-----------|-------------|------------|-------------|--------------|-------------------------------------|---------------------------------|

| 5            | 2.5                    | -72             | 60.6      | 59.9        | 77.9       | 5.0         | 0.86         | 17                                  | 37                              |

| 10           | 2.5                    | -74.3           | 60.7      | 60.4        | 77.8       | 5.9         | 1.2          | 21.3                                | 37                              |

| 15           | 2.5                    | -74             | 60.1      | 59.9        | 77.7       | 6.7         | 1.8          | 25                                  | 37                              |

| 20           | 5                      | -75.1           | 53.4      | 53.2        | 78.9       | 7.8         | 2.4          | 30                                  | 50                              |

| 30           | 5                      | <del>-</del> 75 | 59.5      | 59.4        | 74.8       | 10          | 4.0          | 42                                  | 50                              |

#### **POWER CONTROL**

Power consumed by the AD9203 may be reduced by placing a resistor between the PWRCON pin and ground. This function will be valuable to users who do not need the AD9203's high conversion rate, but do need even lower power consumption. The external resistor sets the programming of the analog current mirrors. Table II illustrates the relationship between programmed power and performance.

At lower clock rates, less power is required within the analog sections of the AD9203. Placing an external resistor on the PWRCON pin will shunt control current away from some of the current mirrors. This enables the ADC to convert low data rates with extremely low power consumption.

#### INTERFACING TO 5 V SYSTEMS

The AD9203 can be integrated into +5 V systems. This is accomplished by deriving a 3 V power supply from the existing 5 V analog power line through an AD3307-3 linear regulator.

Care must be maintained so that logic inputs do not exceed the maximum rated values listed on the Specifications page.

#### **CLOCK INPUT AND CONSIDERATIONS**

The AD9203 internal timing uses the two edges of the clock input to generate a variety of internal timing signals. Sampling occurs on the falling edge. The clock input to the AD9203 operating at 40 MSPS may have a duty cycle between 45% to 55% to meet this timing requirement since the minimum specified  $t_{CH}$  and  $t_{CL}$  is 11.25 ns. For clock rates below 40 MSPS, the duty cycle may deviate from this range to the extent that both  $t_{CH}$  and  $t_{CL}$  are satisfied. See Figure 29 for dynamics vs. duty cyle.

High speed high resolution A/Ds are sensitive to the quality of the clock input. The degradation in SNR at a given full-scale input frequency  $(f_{\rm IN})$  due only to aperture jitter  $(t_{\rm A})$  can be calculated with the following equation:

$$SNR \ degradation = 20 \log_{10} \left[ 1/2 \pi f_{IN} t_A \right]$$

In the equation, the rms aperture jitter,  $t_A$ , represents the rootsum square of all the jitter sources, which include the clock input, analog input signal, and A/D aperture jitter specification. Undersampling applications are particularly sensitive to jitter.

Clock input should be treated as an analog signal in cases where aperture jitter may affect the dynamic range of the AD9203. Power supplies for clock drivers should be separated from the A/D output driver supplies to avoid modulating the clock signal with digital noise. Low jitter crystal controlled oscillators make the best clock sources. If the clock is generated from another type of source (by gating, dividing or other method), it should be retimed by the original clock at the last step.

The clock input is referred to the analog supply. Its logic threshold is AVDD/2.

#### **DIGITAL INPUTS AND OUTPUTS**

Each of the AD9203 digital control inputs, 3-STATE, DFS and STBY are referenced to analog ground. CLK is also referenced to analog ground. A low power mode feature is provided such that for STBY = HIGH and the static power of the AD9203 drops to 0.65 mW.

Asserting the DFS pin high will invert the MSB pin, changing the data to a two complement format.

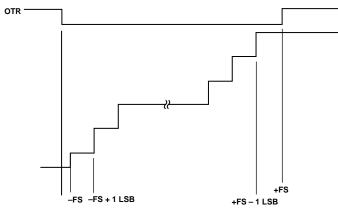

The AD9203 has an OTR (out of range) function. If the input voltage is above or below full scale by 1 LSB, the OTR flag will go high. See Figure 30.

Figure 30. Output Data Format

Figure 31. Simplified IF Sampling Circuit

#### **APPLICATIONS**

#### **DIRECT IF DOWN CONVERSION USING THE AD9203**

Sampling IF signals above an ADC's baseband region (i.e., dc to FS/2) is becoming increasingly popular in communication applications. This process is often referred to as Direct IF Down Conversion or Undersampling. There are several potential benefits in using the ADC to alias (i.e., or mix) down a narrow band or wide band IF signal. First and foremost is the elimination of a complete mixer stage with its associated amplifiers and filters, reducing cost and power dissipation. Second is the ability to apply various DSP techniques to perform such functions as filtering, channel selection, quadrature demodulation, data reduction, detection, etc. A detailed discussion on using this technique in digital receivers can be found in Analog Devices Application Notes AN-301 and AN-302.

In Direct IF Down Conversion applications, one exploits the inherent sampling process of an ADC in which an IF signal lying outside the baseband region can be aliased back into the baseband region in a manner similar to a mixer down-converting an IF signal. Similar to the mixer topology, an image rejection filter is required to limit other potential interfering signals from also aliasing back into the ADC's baseband region. A trade-off exists between the complexity of this image rejection filter and the ADC's sample rate as well as dynamic range.

The AD9203 is well suited for various IF sampling applications. The AD9203's low distortion input SHA has a full-power bandwidth extending to 130 MHz, thus encompassing many popular IF frequencies. Only the 2 V span should be used for undersampling beyond 20 MHz. A DNL of  $\pm 0.25$  LSB combined with low thermal input referred noise allows the AD9203 in the 2 V span to provide >59 dB of SNR for a baseband input sine wave. Also, its low aperture jitter of 1.2 ps rms ensures minimum SNR degradation at higher IF frequencies. In fact, the AD9203 is capable of still maintaining 58 dB of SNR at an IF of 70 MHz with a 2 V input span.

To maximize its distortion performance, the AD9203 should be configured in the differential mode with a 2 V span using a transformer. The center-tap of the transformer is biased to the reference output of the AD9203. Preceding the AD9203 and transformer is an optional bandpass filter as well as a gain stage. A low Q passive bandpass filter can be inserted to reduce out-of-band distortion and noise that lies within the AD9203's 390 MHz bandwidth. A large gain stage(s) is often required to compensate for the high insertion losses of a SAW filter used for channel selection and image rejection. The gain stage will also provide adequate isolation for the SAW filter from the charge "kick back" currents associated with the AD9203's switched capacitor input stage.

The distortion and noise performance of an ADC at the given IF frequency is of particular concern when evaluating an ADC

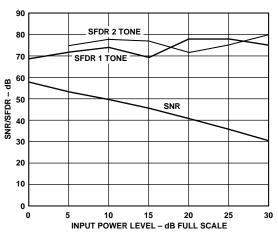

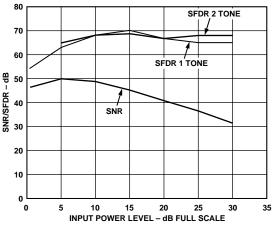

for a narrowband IF sampling application. Both single tone and dual tone SFDR vs. amplitude are very useful in assessing an ADC's dynamic and static nonlinearities. SNR vs. amplitude performance at the given IF is useful in assessing the ADC's noise performance and noise contribution due to aperture jitter. In any application, one is advised to test several units of the same device under the same conditions to evaluate the given applications sensitivity to that particular device. Figures 32 and 33 combine the dual tone SFDR as well as single tone SFDR and SNR performances at IF frequencies of 70 MHz, and 130 MHz. Note, the SFDR vs. amplitude data is referenced to dBFS while the single tone SNR data is referenced to dBc. The performance characteristics in these figures are representative of the AD9203 without any preceding gain stage. The AD9203 was operated in the differential mode (via transformer) with a 2 V span and a sample rate of 40 MSPS. The analog supply (AVDD) and the digital supply (DRVDD) were set to 3.0 V.

Figure 32. SNR/SFDR for IF @ 70 MHz (Clock = 40 MSPS)

Figure 33. SNR/SFDR for IF @ 130 MHz (Clock = 40 MSPS)

REV. 0 -15-

#### **ULTRASOUND APPLICATIONS**

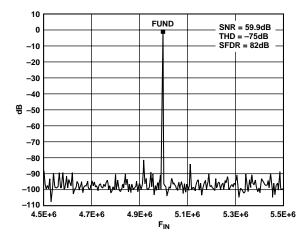

The AD9203 provides excellent performance in 10-bit ultrasound applications. This is demonstrated by its high SNR with analog input frequencies up to and including Nyquist. The presence of spurs near the base of a fundamental frequency bin is demonstrated by Figure 35. Note that the spurs near the noise floor are more than 80 dB below  $f_{\rm IN}$ . This is especially valuable in Doppler ultrasound applications where low frequency shifts from the fundamental are important.

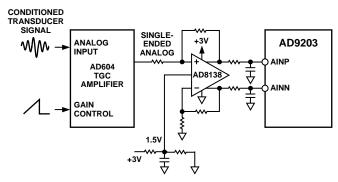

Figure 34. Ultrasound Connection for the AD9203

Figure 34 illustrates the AD604 variable gain amplifier configured for time gain compensation (TGC). The low power AD9203 is powered from a 3 V supply rail while the high performance AD604 is powered from 5 V supply rails. An AD8138 is used to drive the AD9203. This is implemented due to the ability of differential drive techniques to cancel common mode noise and input anomalies.

The 74 mW power consumption gives the 40 MSPS AD9203 an order of magnitude improvement over older generation components.

Figure 35. SFDR Performance Near the Fundamental Signal (8192 Point FFT,  $f_{IN} = 5$  MHz,  $F_S = 40$  MSPS)

#### **EVALUATION BOARD**

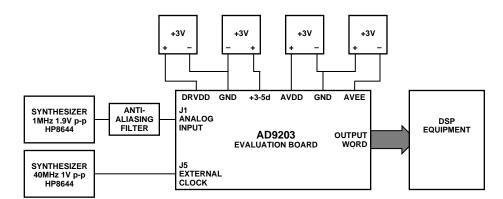

The AD9203 evaluation board is shipped wired for 2 V differential operation. The board should be connected to power and test equipment as shown in Figure 36. It is easily configured for single ended and differential operation as well as 1 V and 2 V spans. Refer to schematic on next page.

Figure 36. Evaluation Board Connection

-16- REV. 0

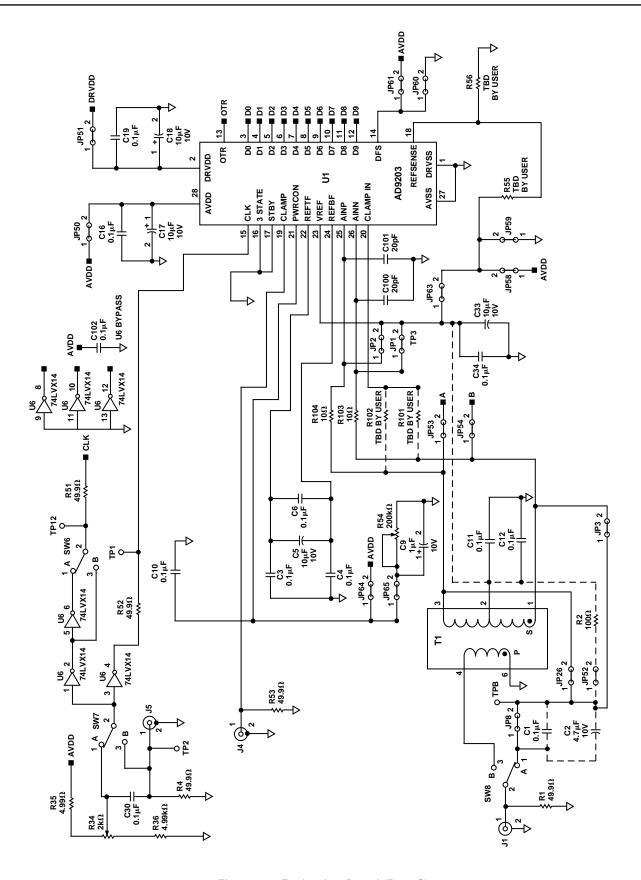

Figure 37. Evaluation Board (Rev. C)

REV. 0 –17–

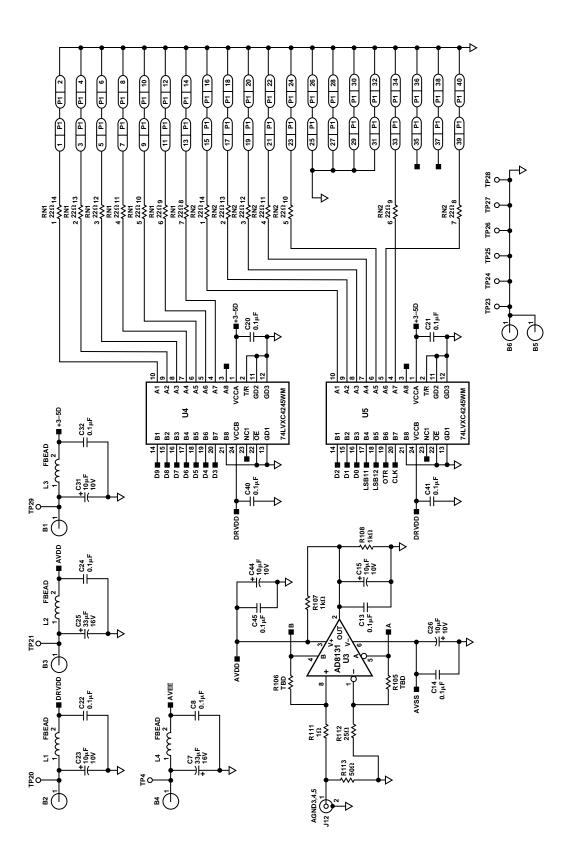

Figure 38. Evaluation Board (Rev. C)

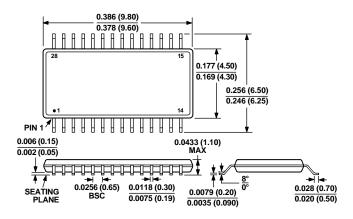

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

# 28-Lead Thin Shrink Small Outline (RU-28)

REV. 0 -19-